|

coreboot

coreboot is an Open Source project aimed at replacing the proprietary BIOS found in most computers.

|

|

coreboot

coreboot is an Open Source project aimed at replacing the proprietary BIOS found in most computers.

|

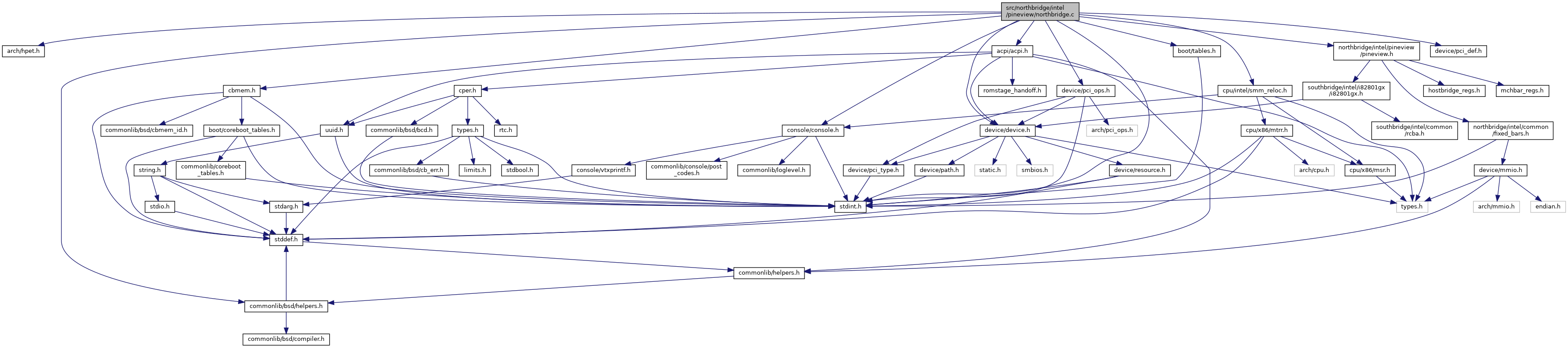

#include <arch/hpet.h>#include <cbmem.h>#include <console/console.h>#include <commonlib/bsd/helpers.h>#include <device/pci_def.h>#include <device/pci_ops.h>#include <stdint.h>#include <device/device.h>#include <boot/tables.h>#include <acpi/acpi.h>#include <northbridge/intel/pineview/pineview.h>#include <cpu/intel/smm_reloc.h>

Go to the source code of this file.

Functions | |

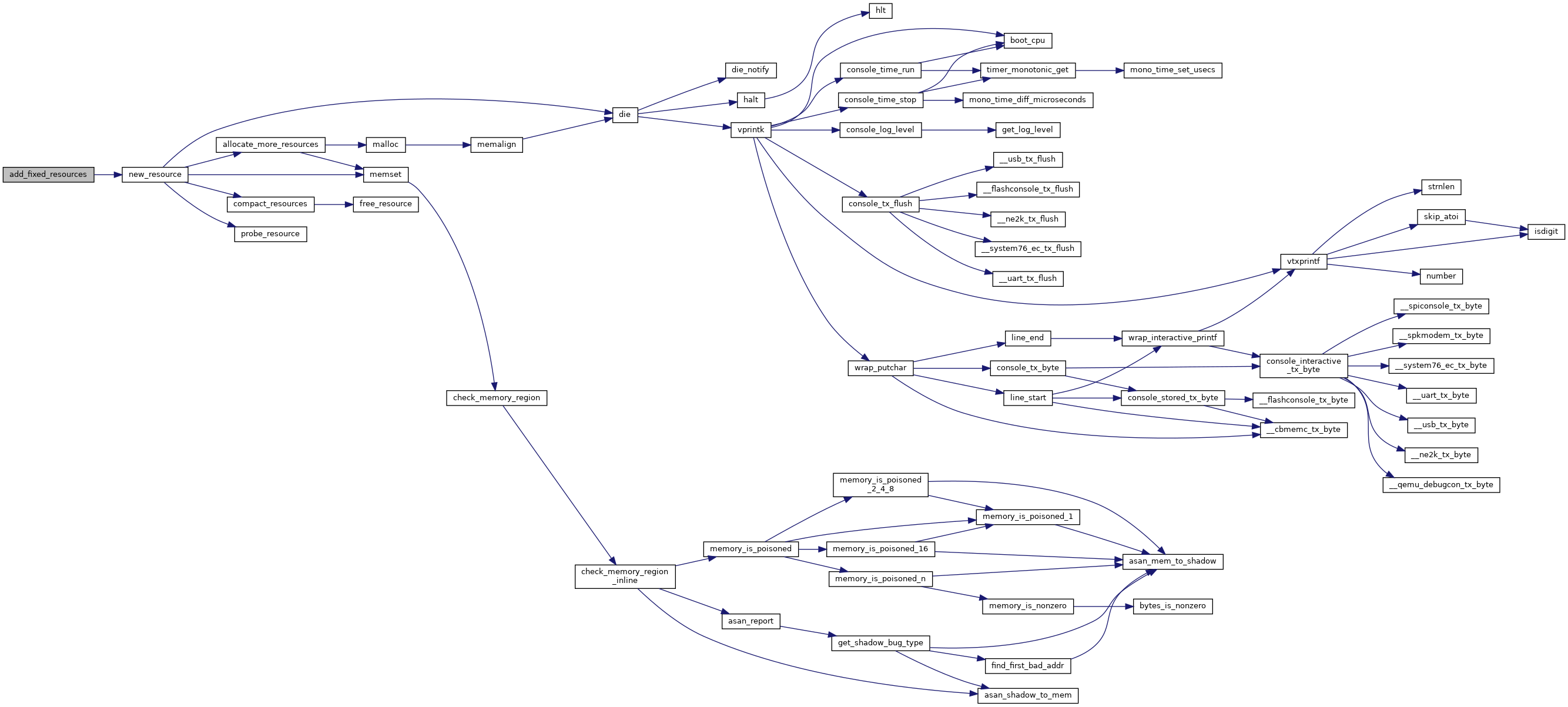

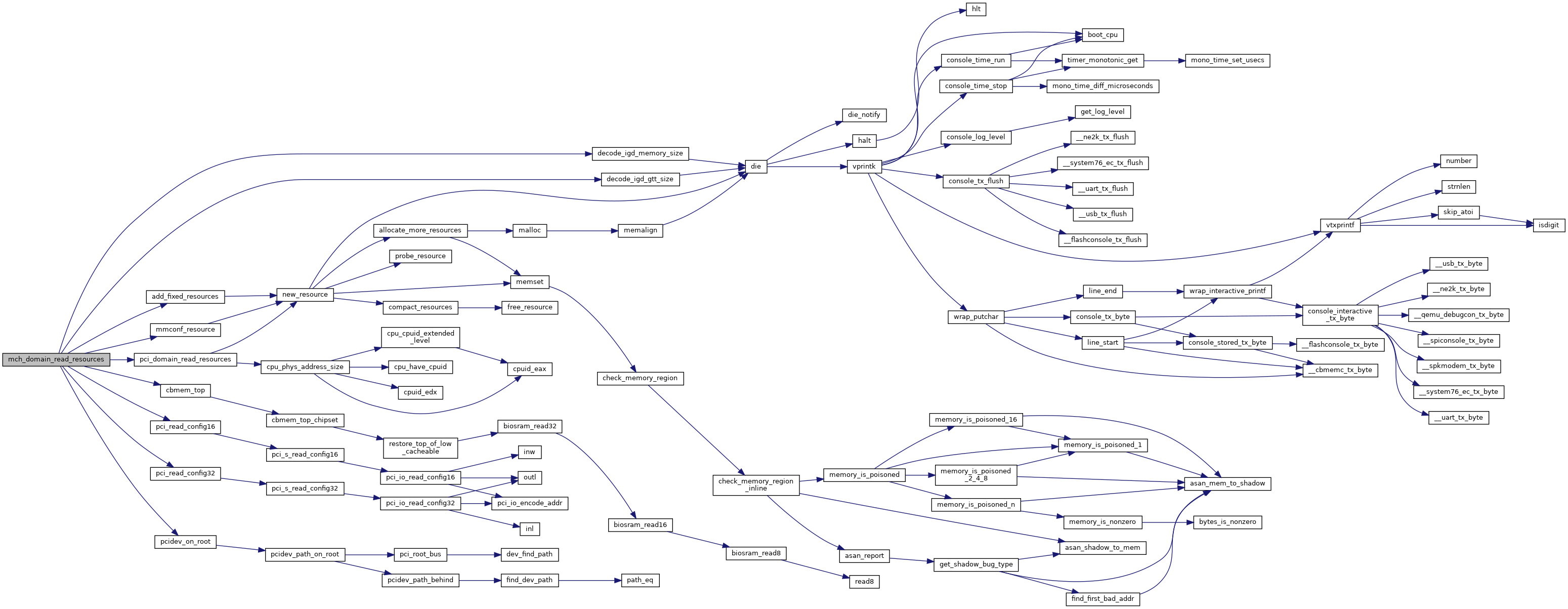

| static void | add_fixed_resources (struct device *dev, int index) |

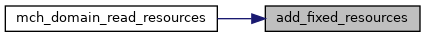

| static void | mch_domain_read_resources (struct device *dev) |

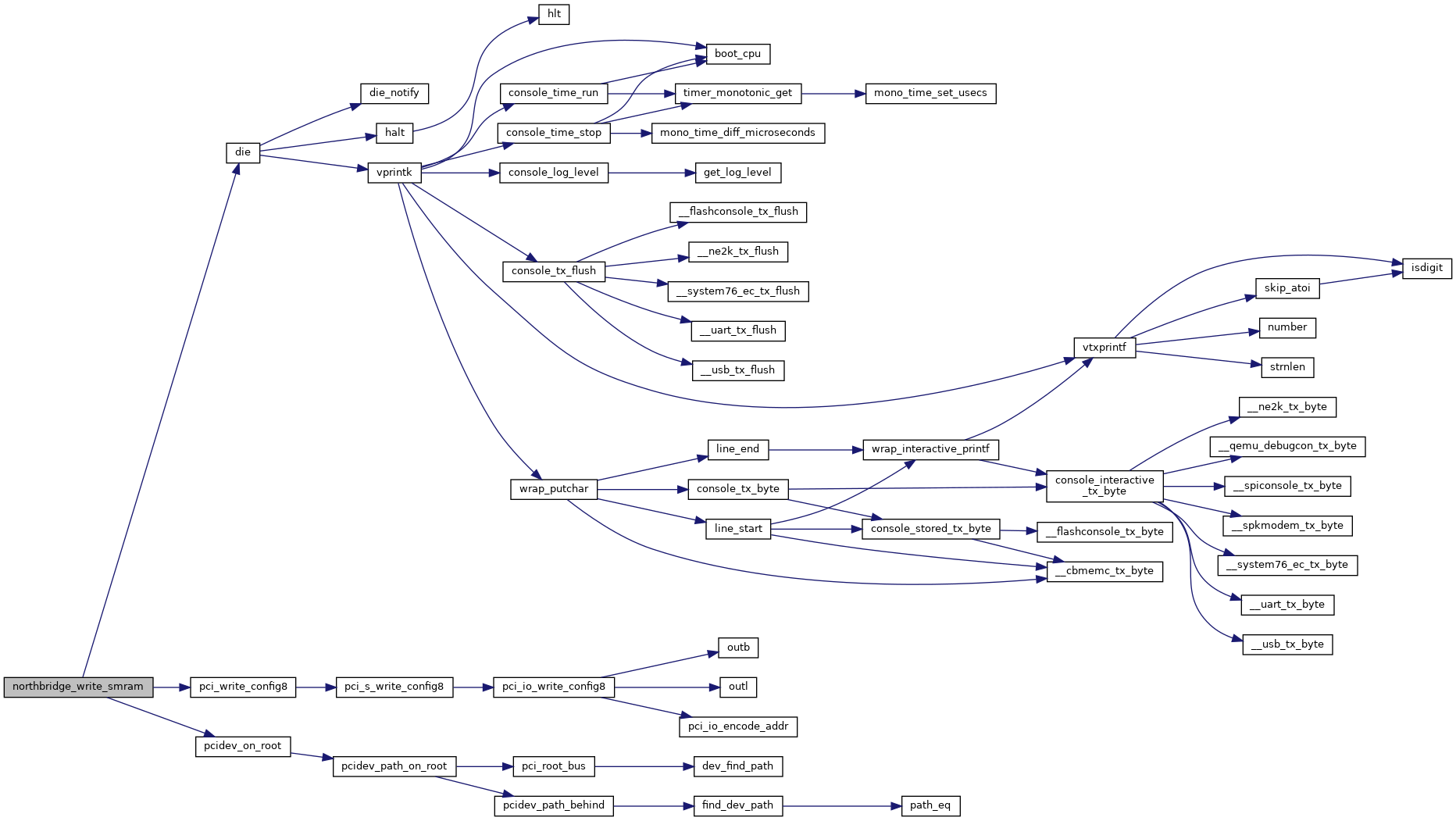

| void | northbridge_write_smram (u8 smram) |

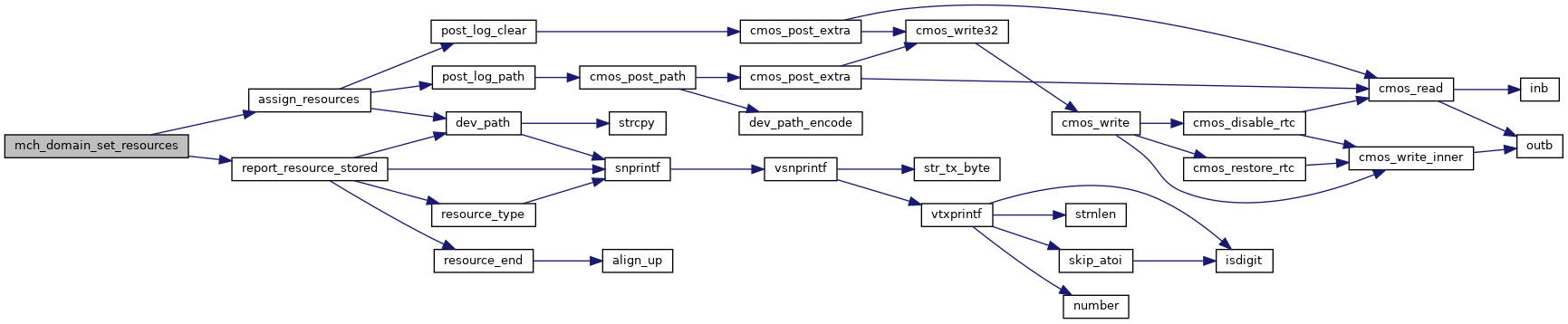

| static void | mch_domain_set_resources (struct device *dev) |

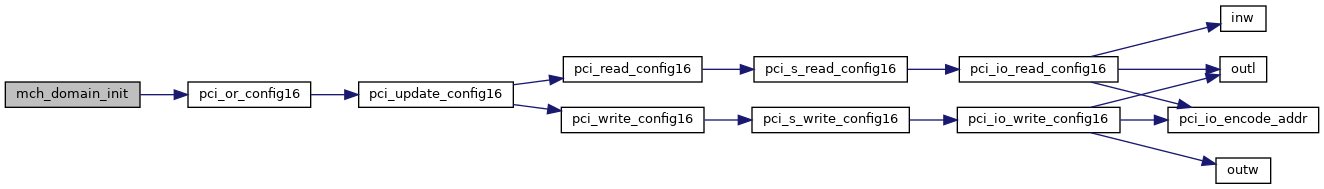

| static void | mch_domain_init (struct device *dev) |

| static const char * | northbridge_acpi_name (const struct device *dev) |

| static void | enable_dev (struct device *dev) |

Variables | |

| static const int | legacy_hole_base_k = 0xa0000 / KiB |

| static struct device_operations | pci_domain_ops |

| static struct device_operations | cpu_bus_ops |

| struct chip_operations | northbridge_intel_pineview_ops |

Definition at line 25 of file northbridge.c.

References resource::base, resource::flags, HPET_BASE_ADDRESS, resource::index, IORESOURCE_ASSIGNED, IORESOURCE_FIXED, IORESOURCE_MEM, IORESOURCE_RESERVE, IORESOURCE_STORED, KiB, legacy_hole_base_k, mmio_resource, new_resource(), reserved_ram_resource, and resource::size.

Referenced by mch_domain_read_resources().

Definition at line 181 of file northbridge.c.

References cpu_bus_ops, DEVICE_PATH_CPU_CLUSTER, DEVICE_PATH_DOMAIN, device::ops, device::path, pci_domain_ops, and device_path::type.

Definition at line 144 of file northbridge.c.

References PCI_COMMAND, PCI_COMMAND_SERR, and pci_or_config16().

Definition at line 42 of file northbridge.c.

References add_fixed_resources(), BGSM, BIOS_DEBUG, BIOS_INFO, cbmem_top(), decode_igd_gtt_size(), decode_igd_memory_size(), GBSM, GGC, GiB, resource::index, KiB, MiB, mmconf_resource(), mmio_resource, pci_domain_read_resources(), pci_read_config16(), pci_read_config32(), pcidev_on_root(), printk, ram_resource, reserved_ram_resource, TOLUD, TOM, TOUUD, and TSEG.

Definition at line 134 of file northbridge.c.

References assign_resources(), device::link_list, resource::next, report_resource_stored(), and device::resource_list.

|

static |

Definition at line 150 of file northbridge.c.

Definition at line 124 of file northbridge.c.

References die(), NULL, pci_write_config8(), pcidev_on_root(), and SMRAM.

|

static |

Definition at line 150 of file northbridge.c.

Referenced by enable_dev().

|

static |

Definition at line 23 of file northbridge.c.

Referenced by add_fixed_resources().

| struct chip_operations northbridge_intel_pineview_ops |

Definition at line 181 of file northbridge.c.

|

static |

Definition at line 150 of file northbridge.c.

Referenced by enable_dev().