|

coreboot

coreboot is an Open Source project aimed at replacing the proprietary BIOS found in most computers.

|

|

coreboot

coreboot is an Open Source project aimed at replacing the proprietary BIOS found in most computers.

|

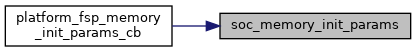

#include <assert.h>#include <console/console.h>#include <fsp/util.h>#include <intelblocks/cpulib.h>#include <soc/iomap.h>#include <soc/pci_devs.h>#include <soc/romstage.h>#include <soc/soc_chip.h>

Go to the source code of this file.

Functions | |

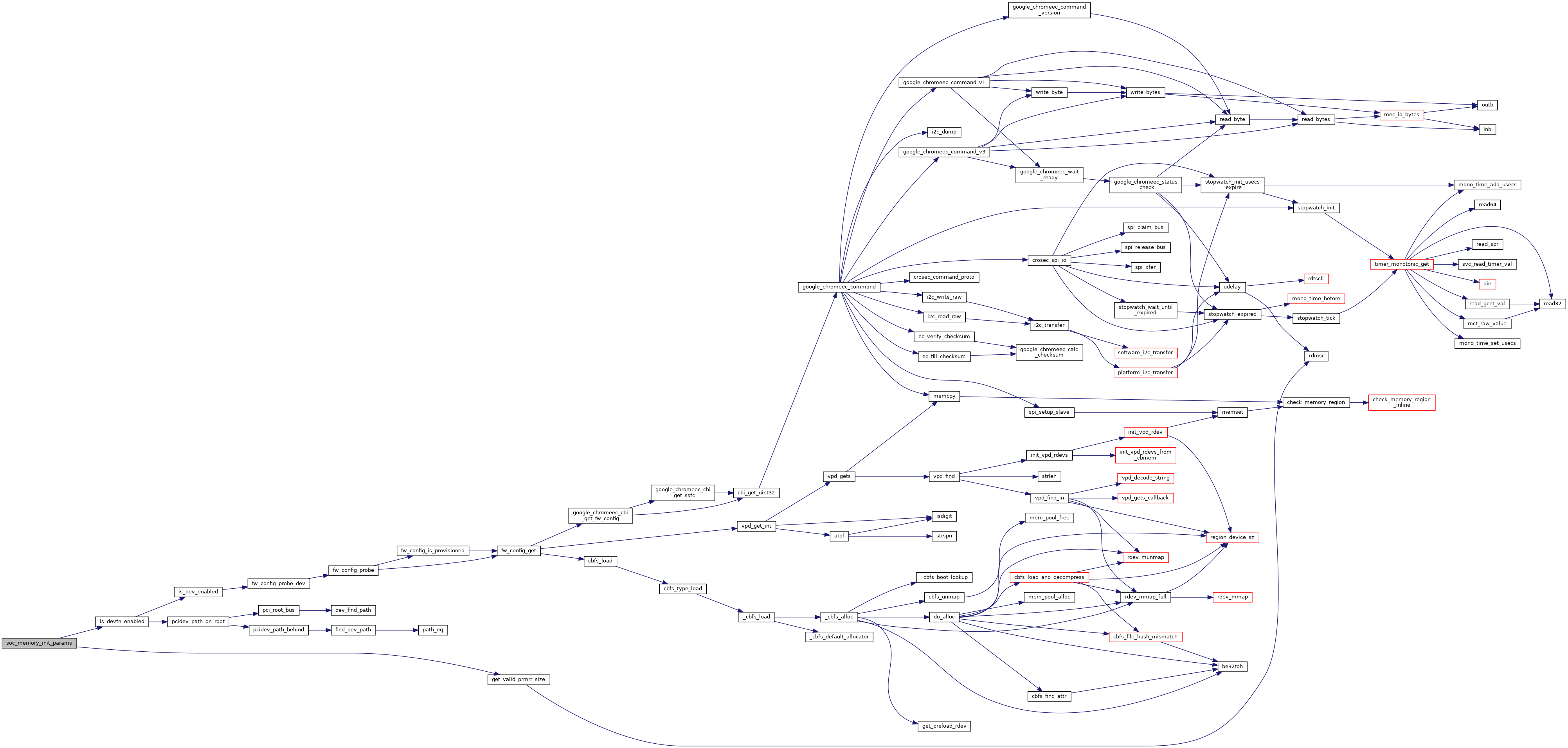

| static void | soc_memory_init_params (FSP_M_CONFIG *m_cfg, const struct soc_intel_icelake_config *config) |

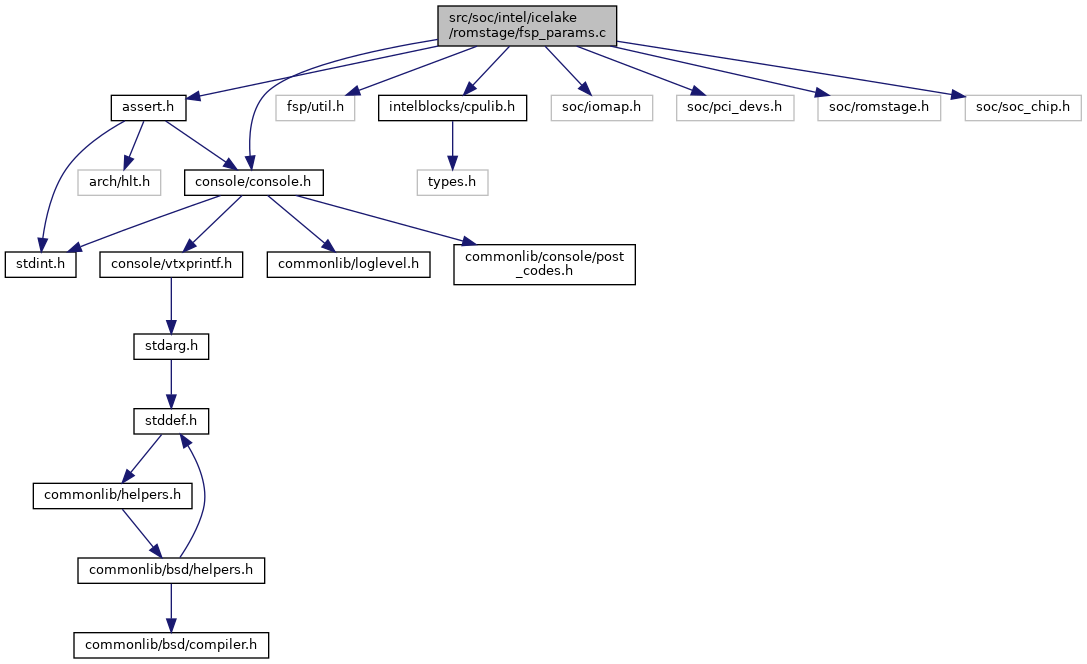

| void | platform_fsp_memory_init_params_cb (FSPM_UPD *mupd, uint32_t version) |

| __weak void | mainboard_memory_init_params (FSPM_UPD *mupd) |

Definition at line 74 of file fsp_params.c.

References BIOS_DEBUG, and printk.

Definition at line 54 of file fsp_params.c.

References config, config_of_soc, FSP_M_CONFIG, mainboard_memory_init_params(), and soc_memory_init_params().

|

static |

Definition at line 12 of file fsp_params.c.

References ARRAY_SIZE, BOARD_TYPE_ULT_ULX, config, CONFIG, get_valid_prmrr_size(), is_devfn_enabled(), mask, PCH_DEVFN_HDA, and SA_DEVFN_IGD.

Referenced by platform_fsp_memory_init_params_cb().