|

coreboot

coreboot is an Open Source project aimed at replacing the proprietary BIOS found in most computers.

|

|

coreboot

coreboot is an Open Source project aimed at replacing the proprietary BIOS found in most computers.

|

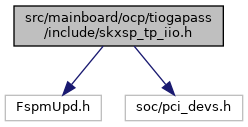

#include <FspmUpd.h>#include <soc/pci_devs.h>

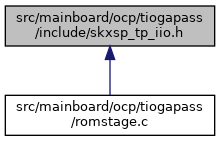

Go to the source code of this file.

Macros | |

| #define | CFG_UPD_PORT(port, hide) |

Enumerations | |

| enum | tp_iio_bifur_table_index { Skt0_Iou0 = 0 , Skt0_Iou1 , Skt0_Iou2 , Skt0_Mcp0 , Skt0_Mcp1 , Skt1_Iou0 , Skt1_Iou1 , Skt1_Iou2 , Skt1_Mcp0 , Skt1_Mcp1 } |

Variables | |

| static const UPD_IIO_BIFURCATION_DATA_ENTRY | tp_iio_bifur_table [] |

| static const UPD_PCI_PORT_CONFIG | tp_iio_pci_port_skt0 [] |

| static const UPD_PCH_PCIE_PORT | tp_pch_pci_port_skt0 [] |

| #define CFG_UPD_PORT | ( | port, | |

| hide | |||

| ) |

Definition at line 42 of file skxsp_tp_iio.h.

| Enumerator | |

|---|---|

| Skt0_Iou0 | |

| Skt0_Iou1 | |

| Skt0_Iou2 | |

| Skt0_Mcp0 | |

| Skt0_Mcp1 | |

| Skt1_Iou0 | |

| Skt1_Iou1 | |

| Skt1_Iou2 | |

| Skt1_Mcp0 | |

| Skt1_Mcp1 | |

Definition at line 9 of file skxsp_tp_iio.h.

|

static |

Definition at line 29 of file skxsp_tp_iio.h.

Referenced by mainboard_config_iio().

|

static |

Definition at line 71 of file skxsp_tp_iio.h.

Referenced by mainboard_config_iio().

|

static |

Definition at line 89 of file skxsp_tp_iio.h.

Referenced by mainboard_config_iio().