|

coreboot

coreboot is an Open Source project aimed at replacing the proprietary BIOS found in most computers.

|

|

coreboot

coreboot is an Open Source project aimed at replacing the proprietary BIOS found in most computers.

|

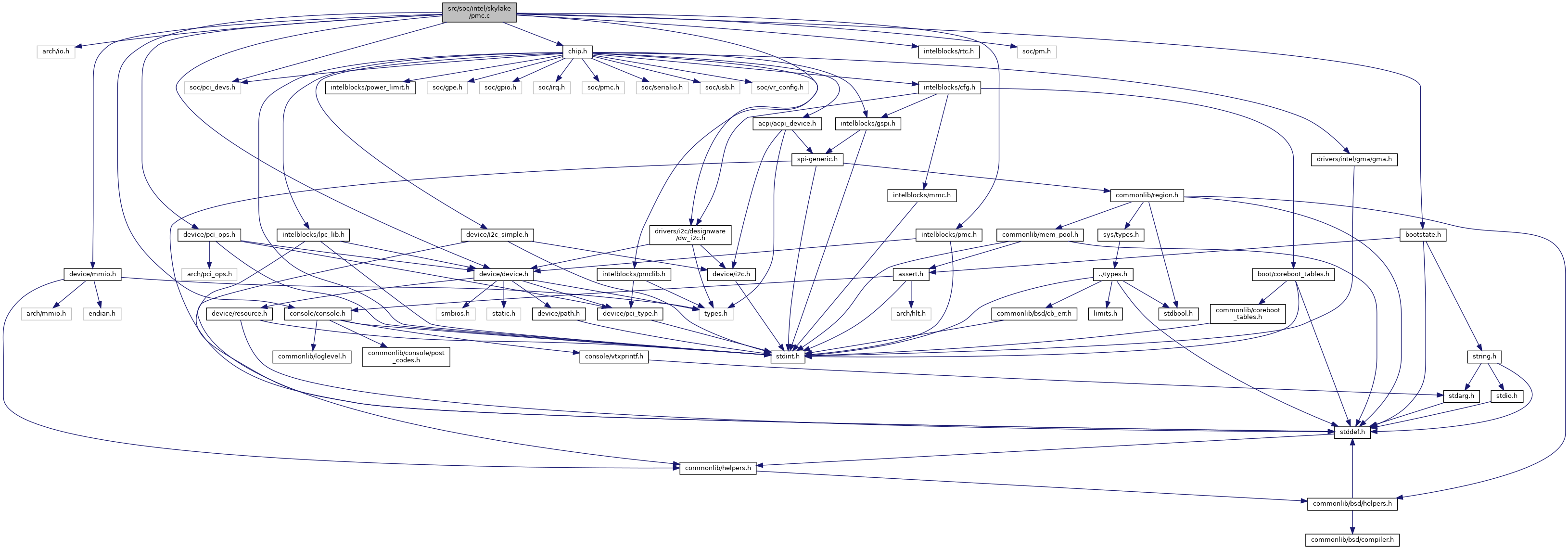

#include <arch/io.h>#include <bootstate.h>#include <console/console.h>#include <device/mmio.h>#include <device/device.h>#include <device/pci_ops.h>#include <intelblocks/pmc.h>#include <intelblocks/pmclib.h>#include <intelblocks/rtc.h>#include <soc/pci_devs.h>#include <soc/pm.h>#include "chip.h"

Go to the source code of this file.

Functions | |

| int | pmc_soc_get_resources (struct pmc_resource_config *cfg) |

| static void | config_deep_sX (uint32_t offset, uint32_t mask, int sx, int enable) |

| static void | config_deep_s5 (int on_ac, int on_dc) |

| static void | config_deep_s3 (int on_ac, int on_dc) |

| static void | config_deep_sx (uint32_t deepsx_config) |

| void | pmc_soc_init (struct device *dev) |

| static void | pm1_enable_pwrbtn_smi (void *unused) |

| BOOT_STATE_INIT_ENTRY (BS_PAYLOAD_LOAD, BS_ON_EXIT, pm1_enable_pwrbtn_smi, NULL) | |

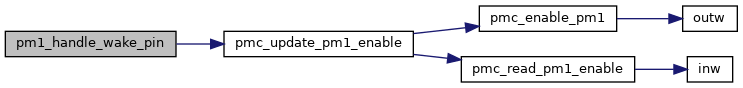

| static void | pm1_handle_wake_pin (void *unused) |

| BOOT_STATE_INIT_ENTRY (BS_PAYLOAD_LOAD, BS_ON_EXIT, pm1_handle_wake_pin, NULL) | |

| BOOT_STATE_INIT_ENTRY (BS_OS_RESUME, BS_ON_EXIT, pm1_handle_wake_pin, NULL) | |

| BOOT_STATE_INIT_ENTRY | ( | BS_OS_RESUME | , |

| BS_ON_EXIT | , | ||

| pm1_handle_wake_pin | , | ||

| NULL | |||

| ) |

| BOOT_STATE_INIT_ENTRY | ( | BS_PAYLOAD_LOAD | , |

| BS_ON_EXIT | , | ||

| pm1_enable_pwrbtn_smi | , | ||

| NULL | |||

| ) |

| BOOT_STATE_INIT_ENTRY | ( | BS_PAYLOAD_LOAD | , |

| BS_ON_EXIT | , | ||

| pm1_handle_wake_pin | , | ||

| NULL | |||

| ) |

|

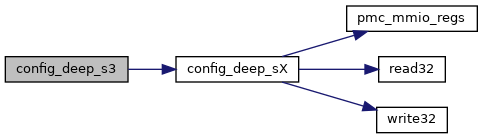

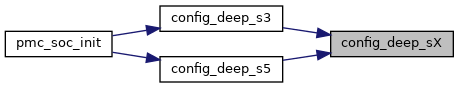

static |

Definition at line 54 of file pmc.c.

References config_deep_sX(), S3_PWRGATE_POL, S3AC_GATE_SUS, and S3DC_GATE_SUS.

Referenced by pmc_soc_init().

|

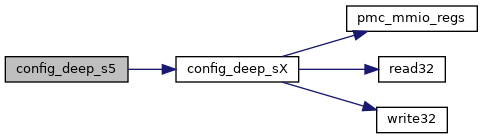

static |

Definition at line 45 of file pmc.c.

References config_deep_sX(), S4_PWRGATE_POL, S4AC_GATE_SUS, S4DC_GATE_SUS, S5_PWRGATE_POL, S5AC_GATE_SUS, and S5DC_GATE_SUS.

Referenced by pmc_soc_init().

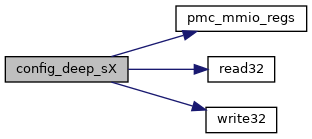

Definition at line 60 of file pmc.c.

References DSX_CFG, DSX_CFG_MASK, pmc_mmio_regs(), read32(), and write32().

Referenced by pmc_soc_init().

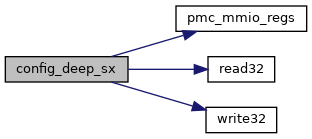

Definition at line 30 of file pmc.c.

References BIOS_DEBUG, mask, offset, pmc_mmio_regs(), printk, read32(), and write32().

Referenced by config_deep_s3(), and config_deep_s5().

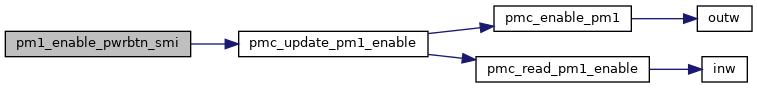

Definition at line 114 of file pmc.c.

References pmc_update_pm1_enable(), and PWRBTN_EN.

Definition at line 135 of file pmc.c.

References config_of_soc, DSX_EN_WAKE_PIN, PCIEXPWAK_DIS, and pmc_update_pm1_enable().

| int pmc_soc_get_resources | ( | struct pmc_resource_config * | cfg | ) |

Definition at line 18 of file pmc.c.

References ABASE, pmc_resource_config::abase_addr, pmc_resource_config::abase_offset, pmc_resource_config::abase_size, ACPI_BASE_ADDRESS, ACPI_BASE_SIZE, PCH_PWRM_BASE_ADDRESS, PCH_PWRM_BASE_SIZE, PWRMBASE, pmc_resource_config::pwrmbase_addr, pmc_resource_config::pwrmbase_offset, and pmc_resource_config::pwrmbase_size.

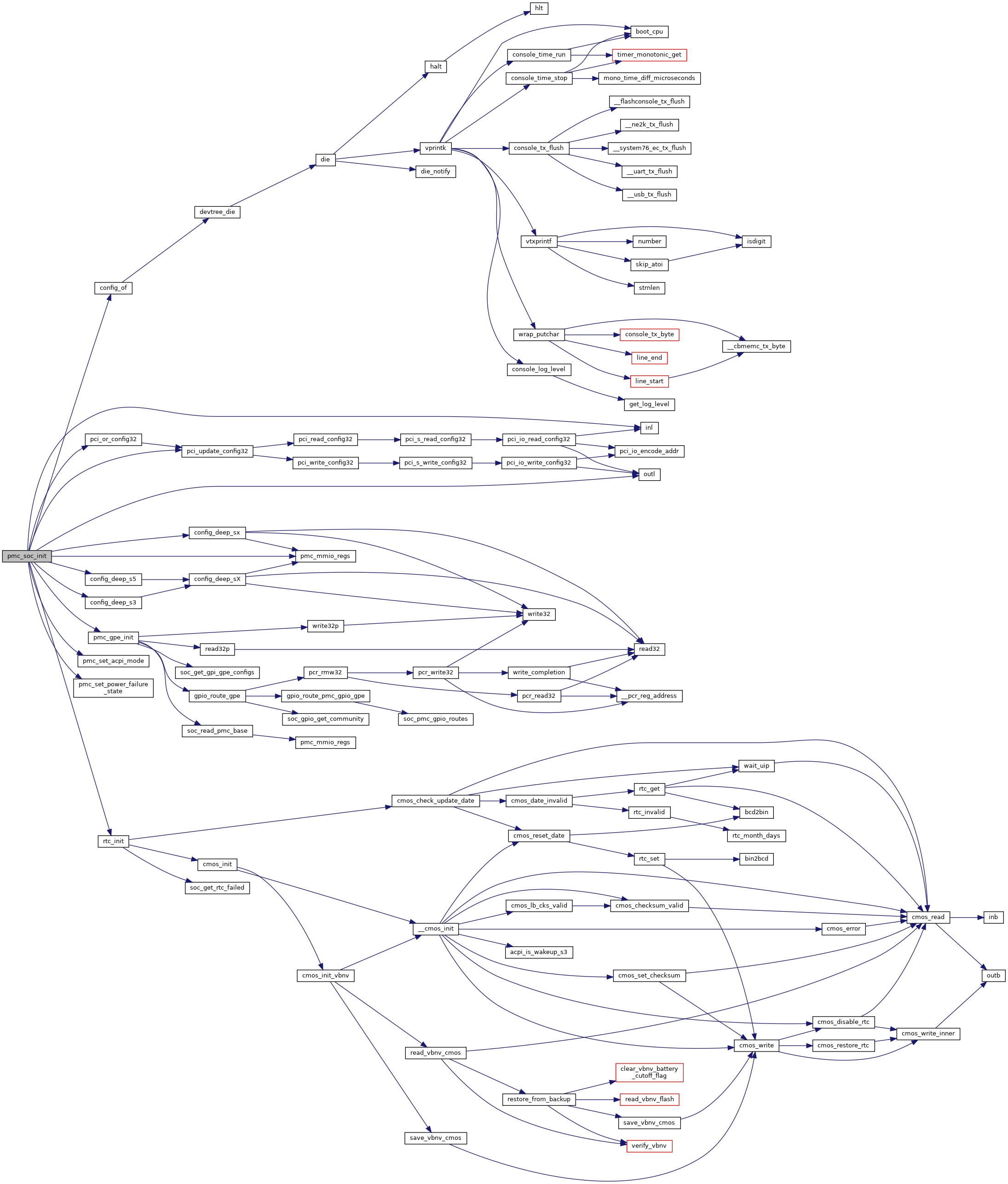

Definition at line 71 of file pmc.c.

References ACPI_BASE_ADDRESS, ACPI_TIM_DIS, config, CONFIG, config_deep_s3(), config_deep_s5(), config_deep_sx(), config_of(), DIS_SLP_X_STRCH_SUS_UP, GBLRST_CAUSE0, GBLRST_CAUSE1, GEN_PMCON_B, inl(), outl(), PCH_PWRM_ACPI_TMR_CTL, pci_or_config32(), pci_update_config32(), PM1_CNT, pmc_gpe_init(), pmc_mmio_regs(), pmc_set_acpi_mode(), pmc_set_power_failure_state(), rtc_init(), S4MAW_4S, S4MAW_MASK, SCI_EN, setbits32, setbits8, SLP_S3_MIN_ASST_WDTH_50MS, SLP_S3_MIN_ASST_WDTH_MASK, and SLP_TYP.