|

coreboot

coreboot is an Open Source project aimed at replacing the proprietary BIOS found in most computers.

|

|

coreboot

coreboot is an Open Source project aimed at replacing the proprietary BIOS found in most computers.

|

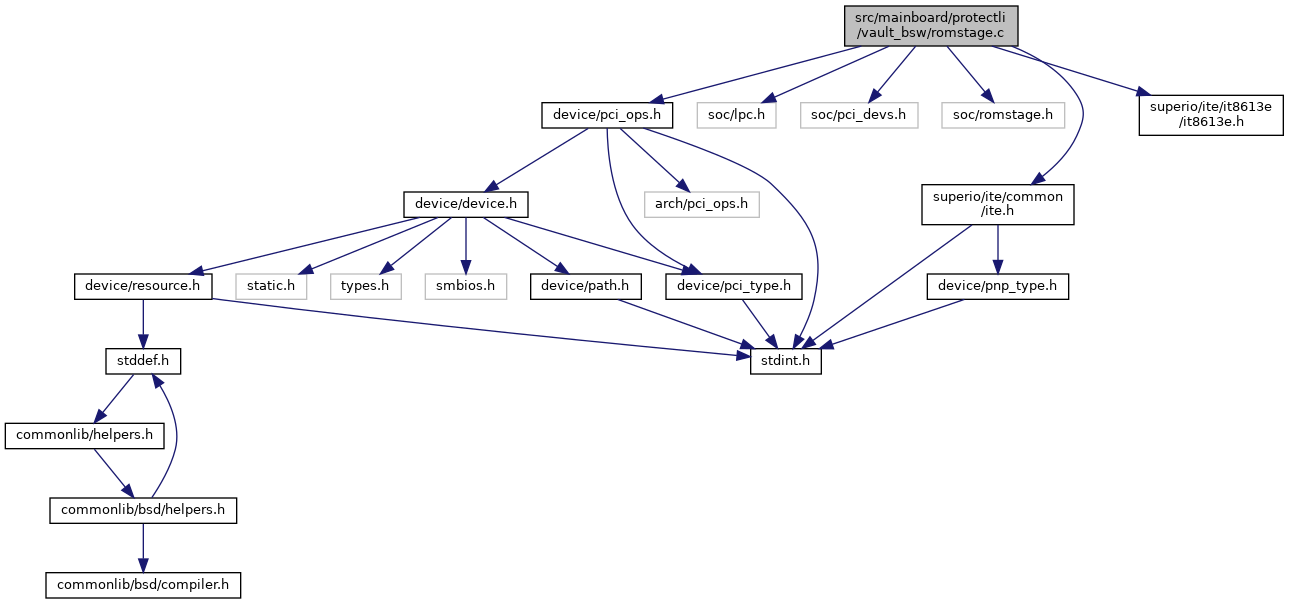

#include <device/pci_ops.h>#include <soc/lpc.h>#include <soc/pci_devs.h>#include <soc/romstage.h>#include <superio/ite/common/ite.h>#include <superio/ite/it8613e/it8613e.h>

Go to the source code of this file.

Macros | |

| #define | SERIAL1_DEV PNP_DEV(0x2e, IT8613E_SP1) |

Functions | |

| void | mainboard_after_memory_init (void) |

| void | mainboard_memory_init_params (struct romstage_params *params, MEMORY_INIT_UPD *memory_params) |

| #define SERIAL1_DEV PNP_DEV(0x2e, IT8613E_SP1) |

Definition at line 10 of file romstage.c.

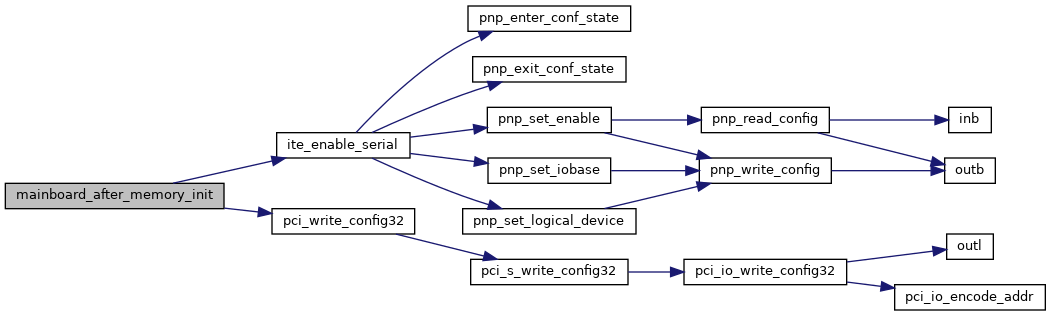

Definition at line 12 of file romstage.c.

References BIOS_DEBUG, ite_enable_serial(), LPC_DEV, PCI_DEV, pci_write_config32(), printk, SERIAL1_DEV, and UART_CONT.

| void mainboard_memory_init_params | ( | struct romstage_params * | params, |

| MEMORY_INIT_UPD * | memory_params | ||

| ) |

Definition at line 22 of file romstage.c.

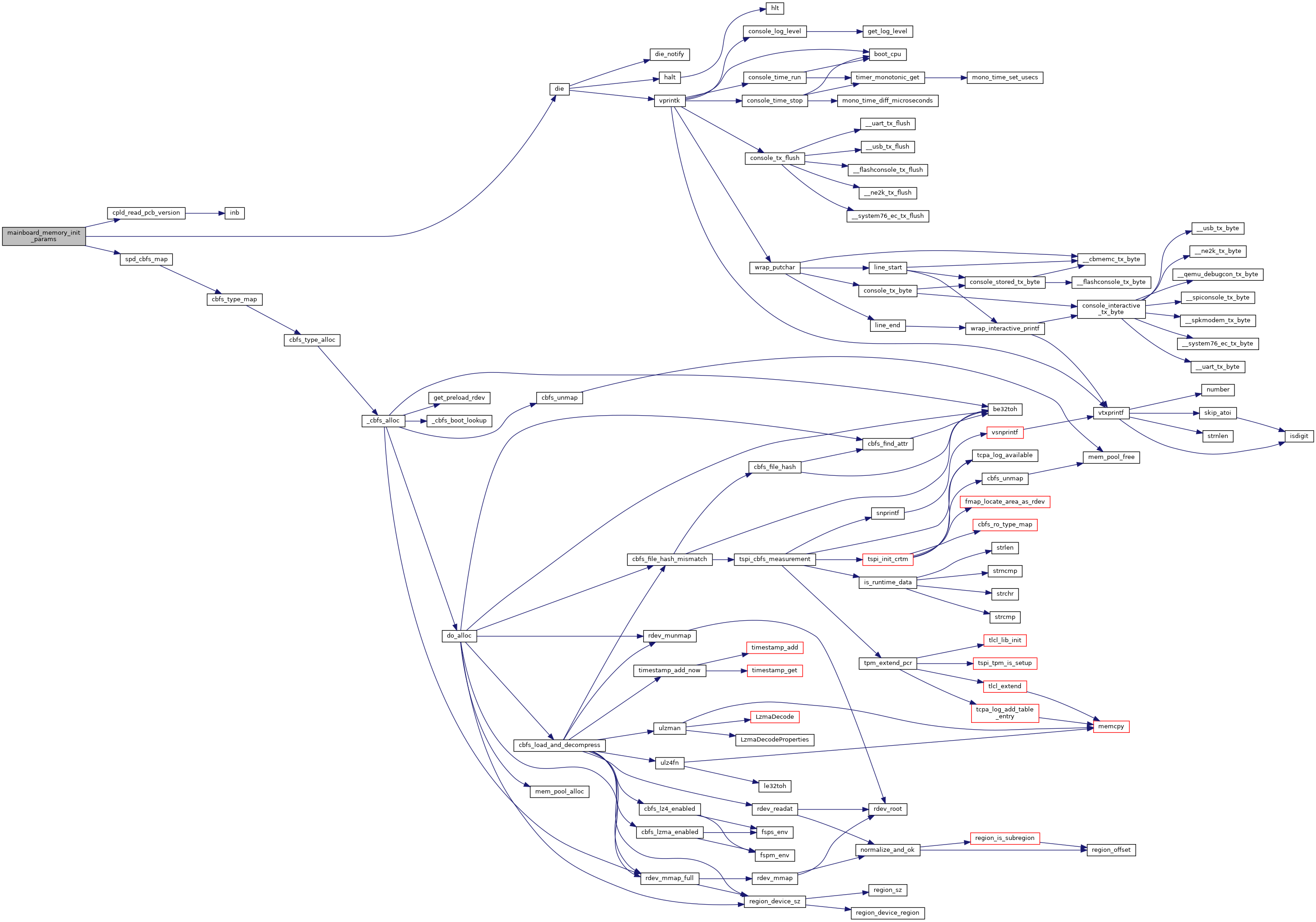

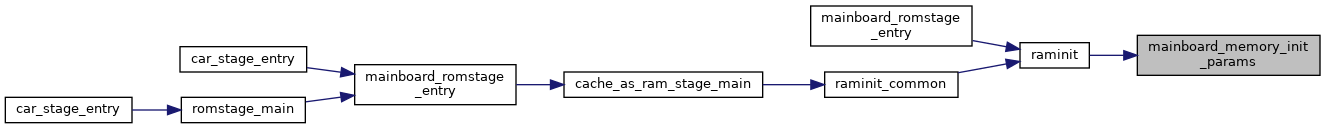

References cpld_read_pcb_version(), die(), MEM_DDR3, spd_cbfs_map(), and spd_index.

Referenced by raminit().