|

coreboot

coreboot is an Open Source project aimed at replacing the proprietary BIOS found in most computers.

|

|

coreboot

coreboot is an Open Source project aimed at replacing the proprietary BIOS found in most computers.

|

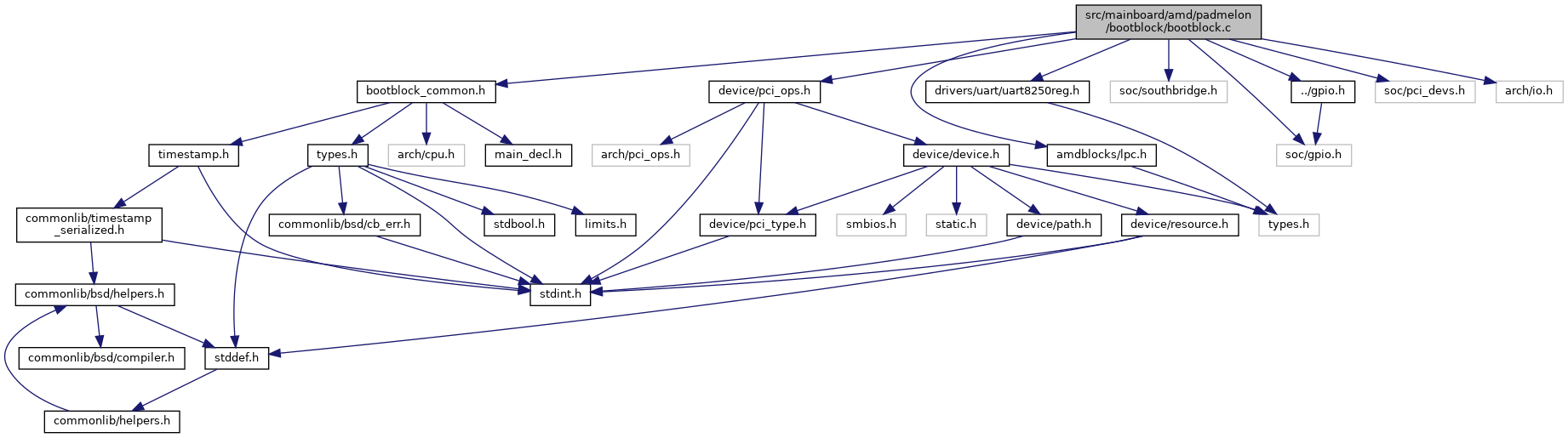

#include <bootblock_common.h>#include <soc/southbridge.h>#include <amdblocks/lpc.h>#include <device/pci_ops.h>#include <soc/gpio.h>#include <soc/pci_devs.h>#include <drivers/uart/uart8250reg.h>#include <arch/io.h>#include "../gpio.h"

Go to the source code of this file.

Functions | |

| static void | enable_serial (unsigned int base_port, unsigned int io_enable) |

| void | bootblock_mainboard_early_init (void) |

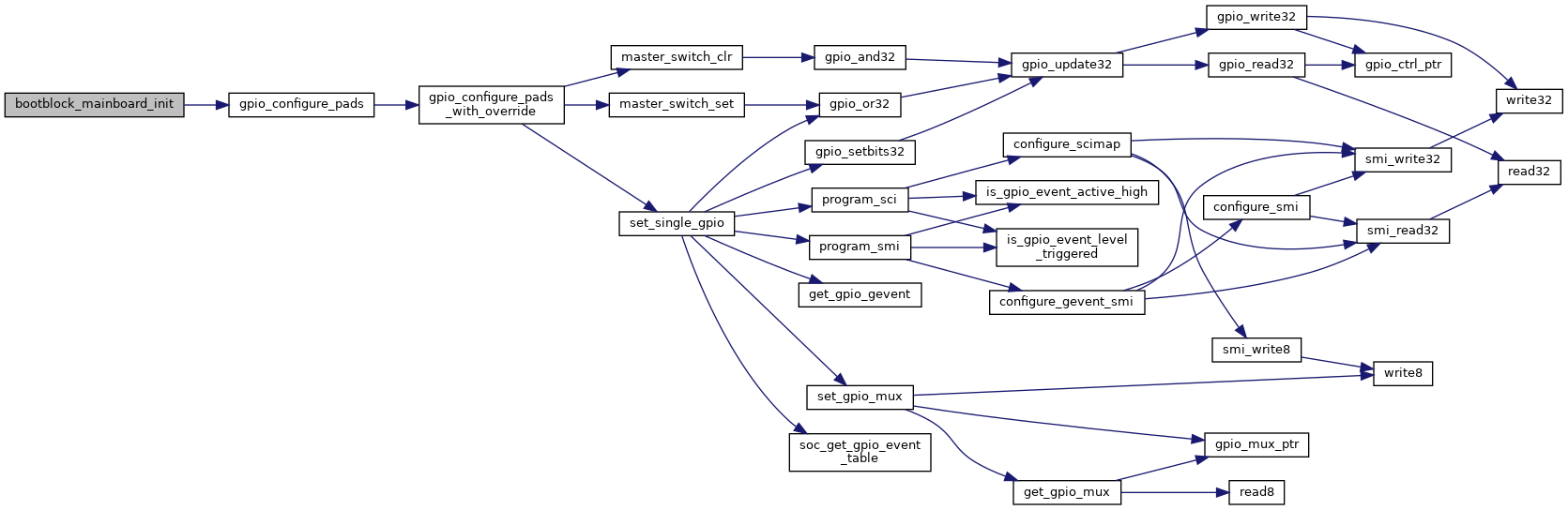

| void | bootblock_mainboard_init (void) |

Definition at line 33 of file bootblock.c.

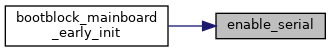

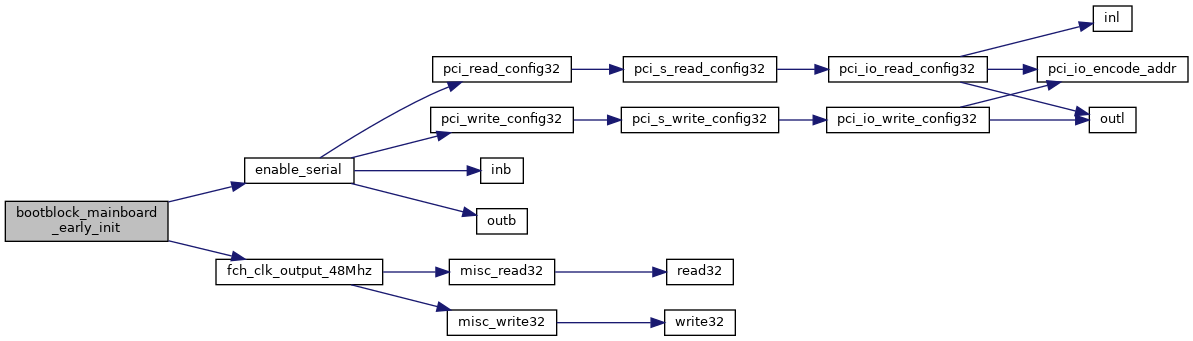

References DECODE_ENABLE_SERIAL_PORT0, DECODE_ENABLE_SERIAL_PORT1, enable_serial(), and fch_clk_output_48Mhz().

Definition at line 44 of file bootblock.c.

References early_gpio_table, and gpio_configure_pads().

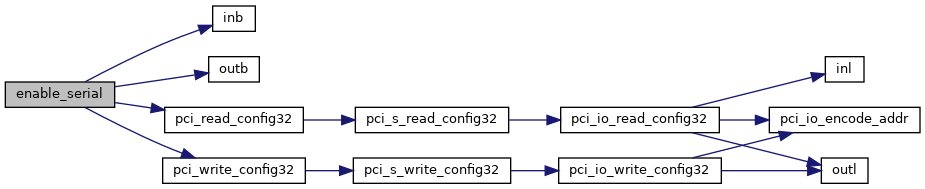

Definition at line 14 of file bootblock.c.

References inb(), LPC_IO_PORT_DECODE_ENABLE, outb(), pci_read_config32(), pci_write_config32(), SOC_LPC_DEV, UART8250_MCR, UART8250_MCR_DTR, and UART8250_MCR_RTS.

Referenced by bootblock_mainboard_early_init().