|

coreboot

coreboot is an Open Source project aimed at replacing the proprietary BIOS found in most computers.

|

|

coreboot

coreboot is an Open Source project aimed at replacing the proprietary BIOS found in most computers.

|

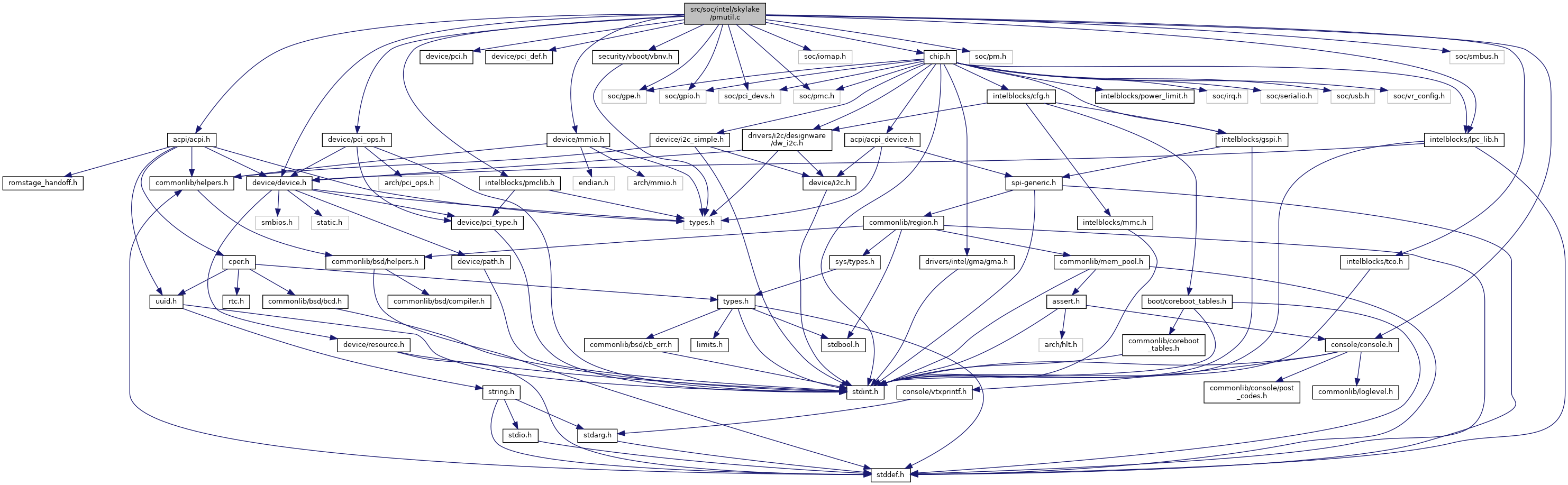

#include <acpi/acpi.h>#include <device/mmio.h>#include <device/pci_ops.h>#include <device/device.h>#include <device/pci.h>#include <device/pci_def.h>#include <console/console.h>#include <intelblocks/pmclib.h>#include <intelblocks/lpc_lib.h>#include <intelblocks/tco.h>#include <soc/gpe.h>#include <soc/gpio.h>#include <soc/iomap.h>#include <soc/pci_devs.h>#include <soc/pm.h>#include <soc/pmc.h>#include <soc/smbus.h>#include <security/vboot/vbnv.h>#include "chip.h"

Go to the source code of this file.

Macros | |

| #define | __SIMPLE_DEVICE__ |

Functions | |

| const char *const * | soc_smi_sts_array (size_t *smi_arr) |

| const char *const * | soc_tco_sts_array (size_t *tco_arr) |

| const char *const * | soc_std_gpe_sts_array (size_t *gpe_arr) |

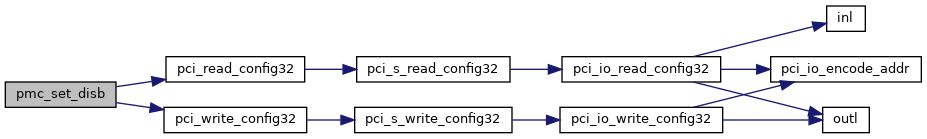

| void | pmc_set_disb (void) |

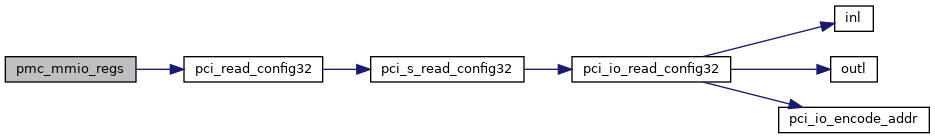

| uint8_t * | pmc_mmio_regs (void) |

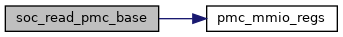

| uintptr_t | soc_read_pmc_base (void) |

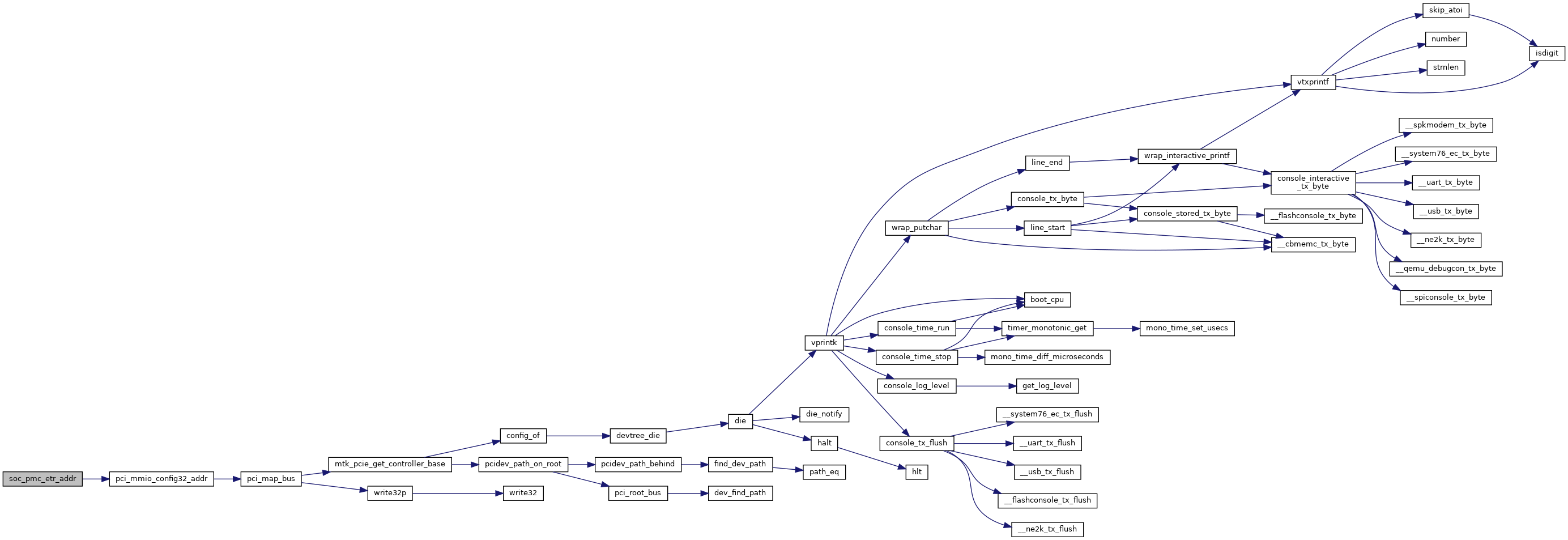

| uint32_t * | soc_pmc_etr_addr (void) |

| void | soc_get_gpi_gpe_configs (uint8_t *dw0, uint8_t *dw1, uint8_t *dw2) |

| int | rtc_failure (void) |

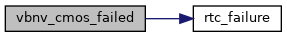

| int | vbnv_cmos_failed (void) |

| int | soc_prev_sleep_state (const struct chipset_power_state *ps, int prev_sleep_state) |

| void | soc_fill_power_state (struct chipset_power_state *ps) |

| uint16_t | get_pmbase (void) |

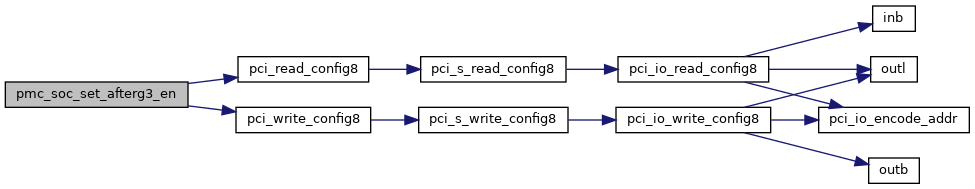

| void | pmc_soc_set_afterg3_en (const bool on) |

Definition at line 247 of file pmutil.c.

References ACPI_BASE_ADDRESS.

Definition at line 130 of file pmutil.c.

References PCH_DEV_PMC, pci_read_config32(), and PWRMBASE.

Definition at line 116 of file pmutil.c.

References DISB, GBL_RST_STS, GEN_PMCON_A, MS4V, PCH_DEV_PMC, pci_read_config32(), and pci_write_config32().

Definition at line 256 of file pmutil.c.

References GEN_PMCON_B, PCH_DEV_PMC, pci_read_config8(), pci_write_config8(), and SLEEP_AFTER_POWER_FAIL.

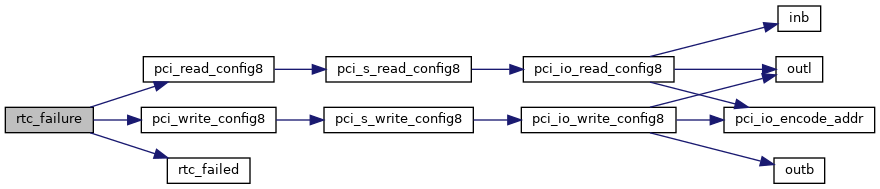

| int rtc_failure | ( | void | ) |

Definition at line 169 of file pmutil.c.

References BIOS_DEBUG, GEN_PMCON_B, PCH_DEV_PMC, pci_read_config8(), pci_write_config8(), printk, RTC_BATTERY_DEAD, and rtc_failed().

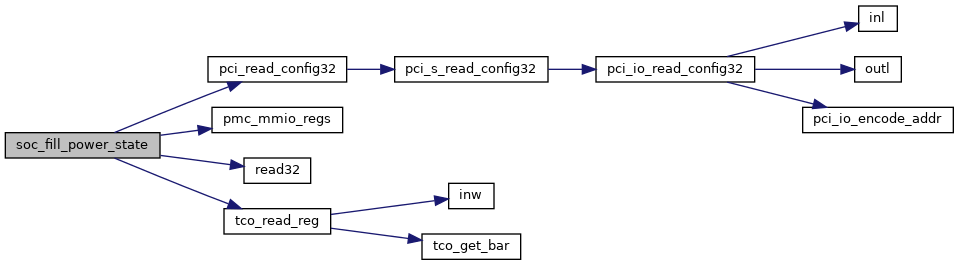

| void soc_fill_power_state | ( | struct chipset_power_state * | ps | ) |

Definition at line 223 of file pmutil.c.

References BIOS_DEBUG, chipset_power_state::gblrst_cause, GBLRST_CAUSE0, GBLRST_CAUSE1, chipset_power_state::gen_pmcon_a, GEN_PMCON_A, chipset_power_state::gen_pmcon_b, GEN_PMCON_B, PCH_DEV_PMC, pci_read_config32(), pmc, pmc_mmio_regs(), printk, read32(), chipset_power_state::tco1_sts, TCO1_STS, chipset_power_state::tco2_sts, TCO2_STS, and tco_read_reg().

Definition at line 157 of file pmutil.c.

References config, config_of_soc, and DEVTREE_CONST.

Definition at line 147 of file pmutil.c.

References ETR, PCH_DEVFN_PMC, and pci_mmio_config32_addr().

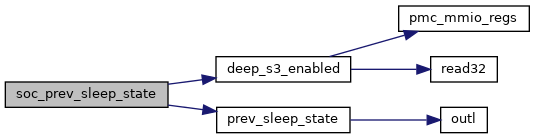

| int soc_prev_sleep_state | ( | const struct chipset_power_state * | ps, |

| int | prev_sleep_state | ||

| ) |

Definition at line 193 of file pmutil.c.

References ACPI_S3, ACPI_S5, deep_s3_enabled(), chipset_power_state::gen_pmcon_b, mask, chipset_power_state::pm1_sts, prev_sleep_state(), PWR_FLR, SUS_PWR_FLR, and WAK_STS.

Definition at line 142 of file pmutil.c.

References pmc_mmio_regs().

| const char* const* soc_smi_sts_array | ( | size_t * | smi_arr | ) |

Definition at line 35 of file pmutil.c.

References APM_STS_BIT, ARRAY_SIZE, BIOS_STS_BIT, DEVMON_STS_BIT, ESPI_SMI_STS_BIT, GPE0_STS_BIT, GPIO_STS_BIT, GPIO_UNLOCK_SMI_STS_BIT, LEGACY_USB_STS_BIT, MCSMI_STS_BIT, MONITOR_STS_BIT, PCI_EXP_SMI_STS_BIT, PERIODIC_STS_BIT, PM1_STS_BIT, SERIRQ_SMI_STS_BIT, SMBUS_SMI_STS_BIT, SMI_ON_SLP_EN_STS_BIT, SPI_SMI_STS_BIT, SWSMI_TMR_STS_BIT, and TCO_STS_BIT.

| const char* const* soc_std_gpe_sts_array | ( | size_t * | gpe_arr | ) |

Definition at line 94 of file pmutil.c.

References ARRAY_SIZE.

| const char* const* soc_tco_sts_array | ( | size_t * | tco_arr | ) |

Definition at line 67 of file pmutil.c.

References ARRAY_SIZE.

| int vbnv_cmos_failed | ( | void | ) |

Definition at line 187 of file pmutil.c.

References rtc_failure().