|

coreboot

coreboot is an Open Source project aimed at replacing the proprietary BIOS found in most computers.

|

|

coreboot

coreboot is an Open Source project aimed at replacing the proprietary BIOS found in most computers.

|

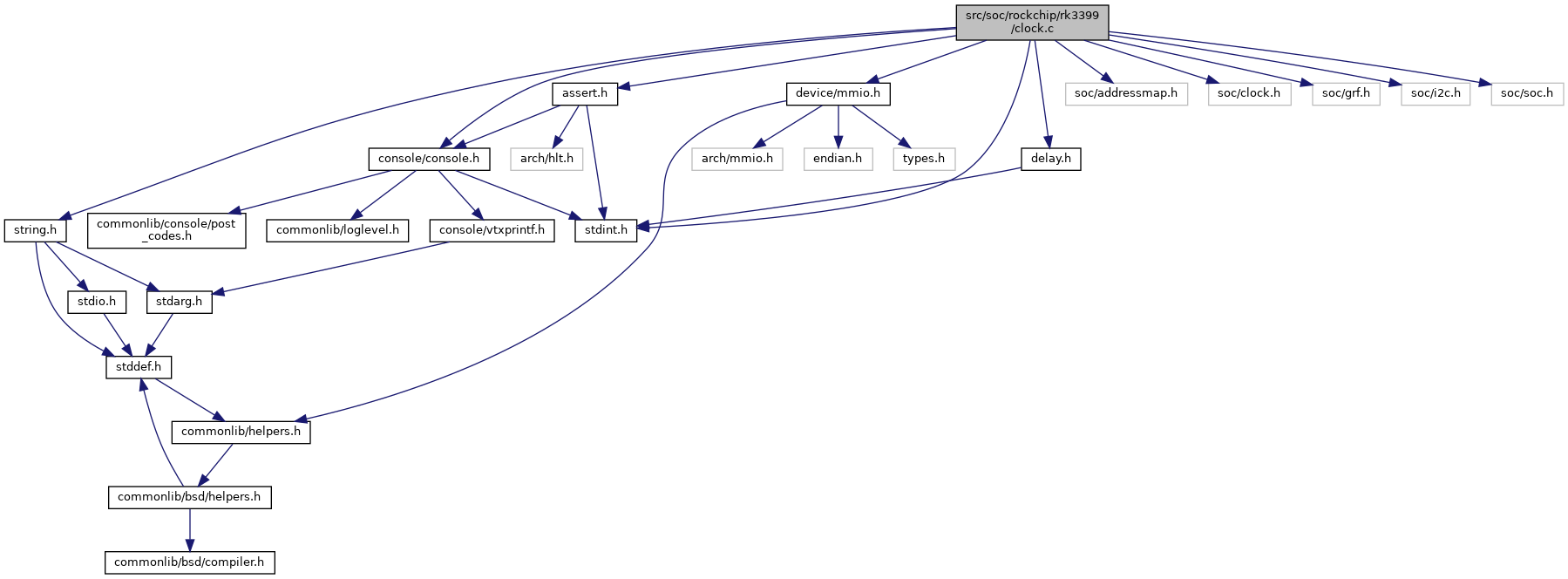

#include <assert.h>#include <console/console.h>#include <device/mmio.h>#include <delay.h>#include <soc/addressmap.h>#include <soc/clock.h>#include <soc/grf.h>#include <soc/i2c.h>#include <soc/soc.h>#include <stdint.h>#include <string.h>

Go to the source code of this file.

Data Structures | |

| struct | pll_div |

Macros | |

| #define | PLL_DIVISORS(hz, _refdiv, _postdiv1, _postdiv2) |

| #define | RESETN_DDR_REQ_SHIFT(ch) (8 + (ch) * 4) |

| #define | RESETN_DDRPHY_REQ_SHIFT(ch) (9 + (ch) * 4) |

| #define | VCO_MAX_KHZ (3200 * (MHz / KHz)) |

| #define | VCO_MIN_KHZ (800 * (MHz / KHz)) |

| #define | OUTPUT_MAX_KHZ (3200 * (MHz / KHz)) |

| #define | OUTPUT_MIN_KHZ (16 * (MHz / KHz)) |

| #define | PLL_DIV_MIN 16 |

| #define | PLL_DIV_MAX 3200 |

| #define | SPI_CLK_REG_VALUE(bus, clk_div) |

| #define | I2C_CLK_REG_VALUE(bus, clk_div) |

| #define | PMU_I2C_CLK_REG_VALUE(bus, clk_div) |

Functions | |

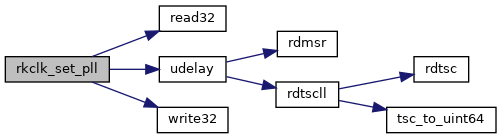

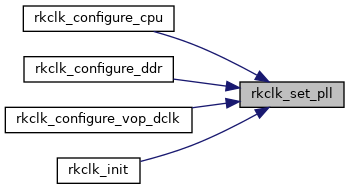

| static void | rkclk_set_pll (u32 *pll_con, const struct pll_div *div) |

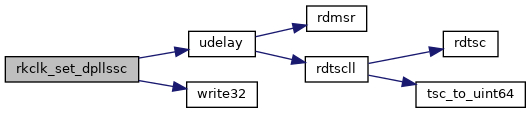

| static void | rkclk_set_dpllssc (struct pll_div *dpll_cfg) |

| static int | pll_para_config (u32 freq_hz, struct pll_div *div) |

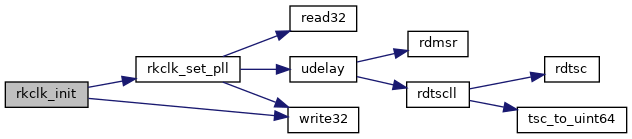

| void | rkclk_init (void) |

| void | rkclk_configure_cpu (enum apll_frequencies freq, enum cpu_cluster cluster) |

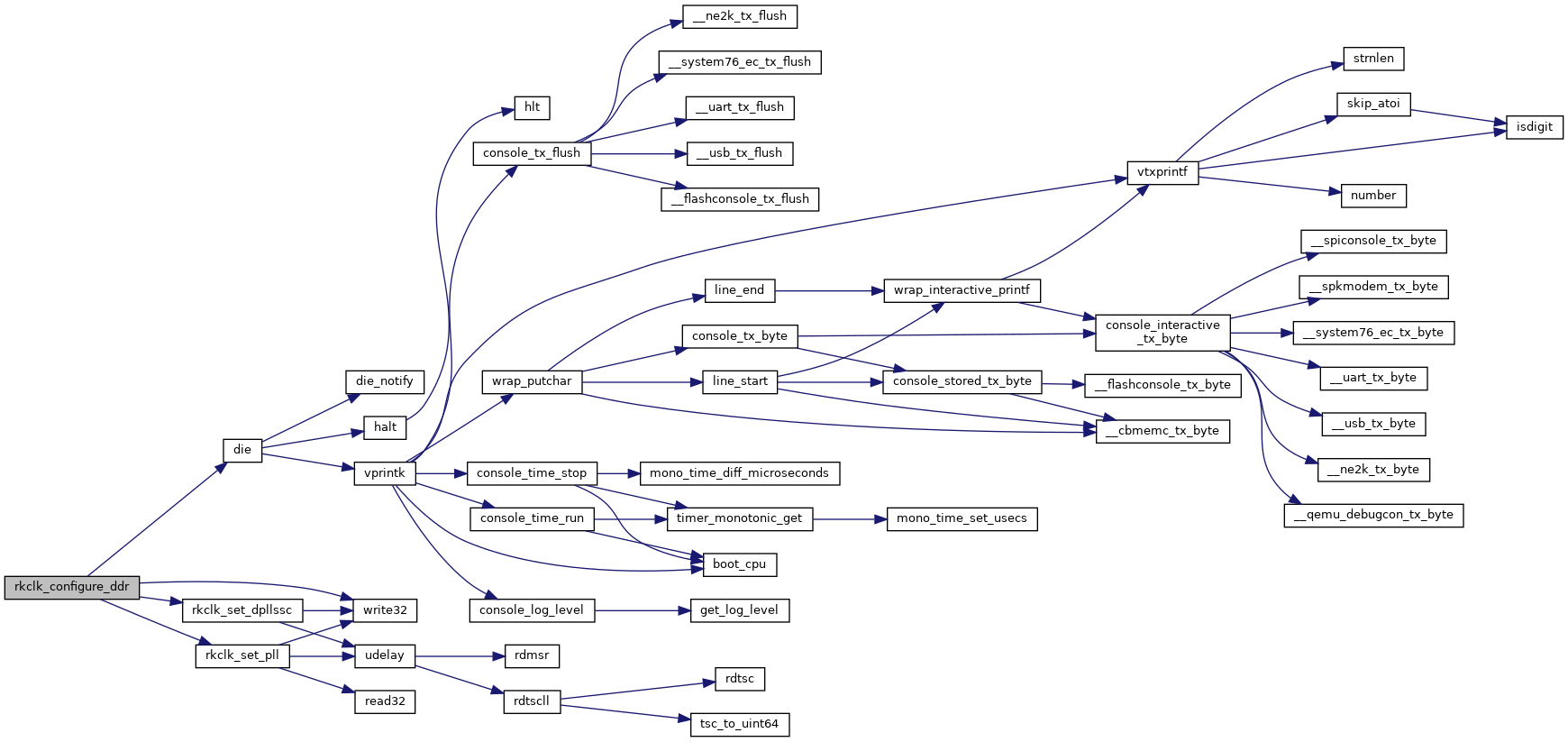

| void | rkclk_configure_ddr (unsigned int hz) |

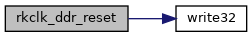

| void | rkclk_ddr_reset (u32 ch, u32 ctl, u32 phy) |

| void | rkclk_configure_spi (unsigned int bus, unsigned int hz) |

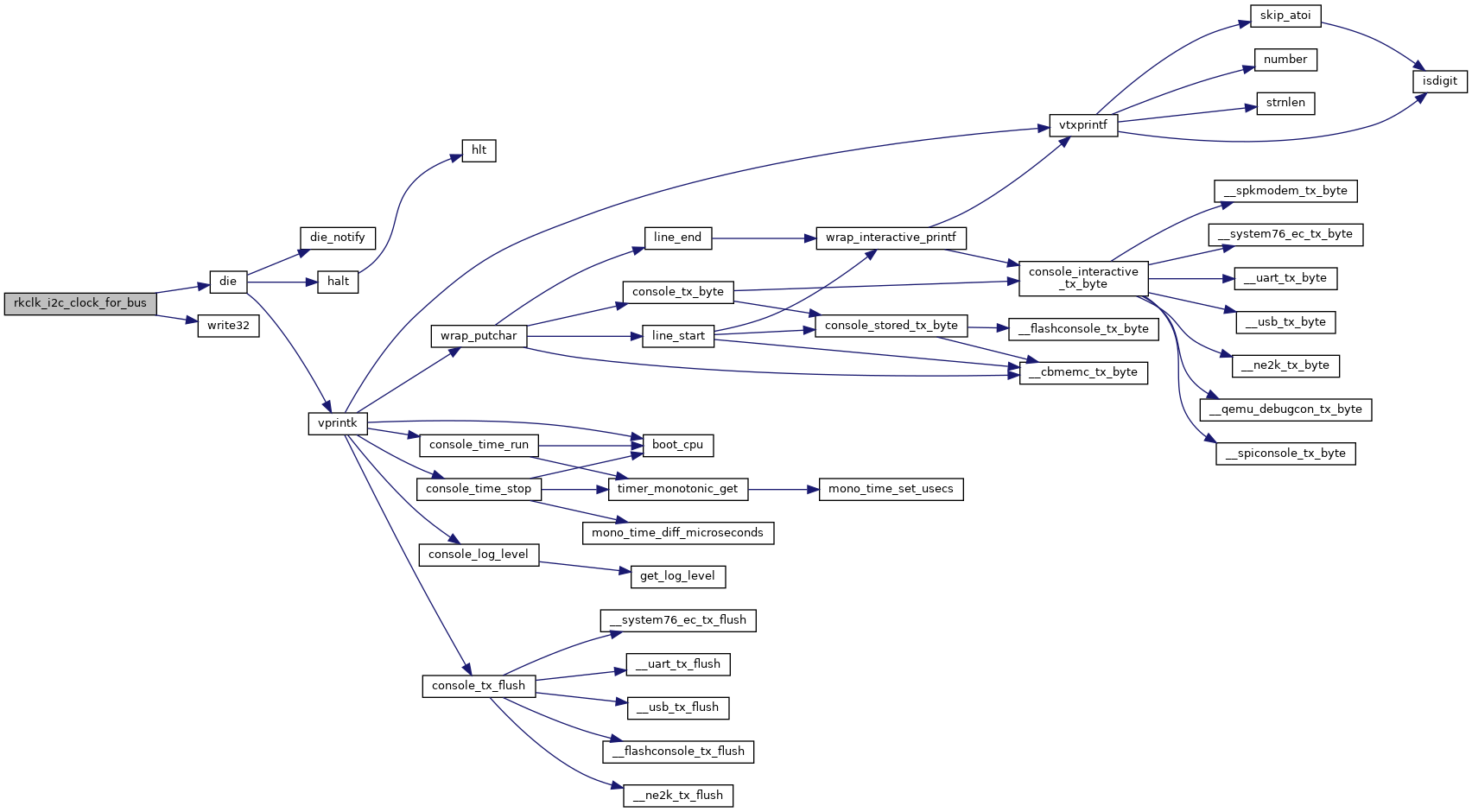

| uint32_t | rkclk_i2c_clock_for_bus (unsigned int bus) |

| static u32 | clk_gcd (u32 a, u32 b) |

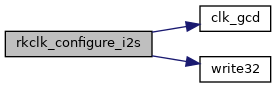

| void | rkclk_configure_i2s (unsigned int hz) |

| void | rkclk_configure_saradc (unsigned int hz) |

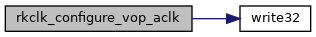

| void | rkclk_configure_vop_aclk (u32 vop_id, u32 aclk_hz) |

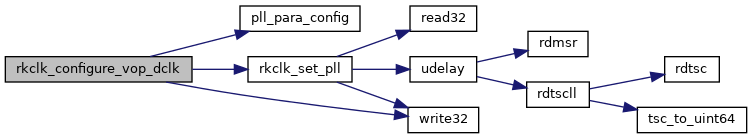

| int | rkclk_configure_vop_dclk (u32 vop_id, u32 dclk_hz) |

| void | rkclk_configure_tsadc (unsigned int hz) |

| void | rkclk_configure_emmc (void) |

| int | rkclk_was_watchdog_reset (void) |

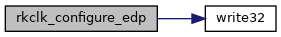

| void | rkclk_configure_edp (unsigned int hz) |

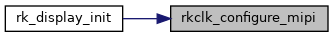

| void | rkclk_configure_mipi (void) |

Variables | |

| static const struct pll_div | gpll_init_cfg = PLL_DIVISORS(GPLL_HZ, 1, 4, 1) |

| static const struct pll_div | cpll_init_cfg = PLL_DIVISORS(CPLL_HZ, 1, 3, 1) |

| static const struct pll_div | ppll_init_cfg = PLL_DIVISORS(PPLL_HZ, 3, 2, 1) |

| static const struct pll_div | apll_1512_cfg = PLL_DIVISORS(1512*MHz, 1, 1, 1) |

| static const struct pll_div | apll_600_cfg = PLL_DIVISORS(600*MHz, 1, 3, 1) |

| static const struct pll_div * | apll_cfgs [] |

| #define I2C_CLK_REG_VALUE | ( | bus, | |

| clk_div | |||

| ) |

| #define PLL_DIVISORS | ( | hz, | |

| _refdiv, | |||

| _postdiv1, | |||

| _postdiv2 | |||

| ) |

| #define SPI_CLK_REG_VALUE | ( | bus, | |

| clk_div | |||

| ) |

| anonymous enum |

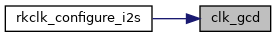

Definition at line 779 of file clock.c.

Referenced by rkclk_configure_i2s().

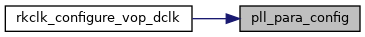

Definition at line 397 of file clock.c.

References BIOS_ERR, DIV_ROUND_UP, pll_div::fbdiv, KHz, MHz, OSC_HZ, pll_div::postdiv1, pll_div::postdiv2, printk, pll_div::refdiv, VCO_MAX_KHZ, and VCO_MIN_KHZ.

Referenced by rkclk_configure_vop_dclk().

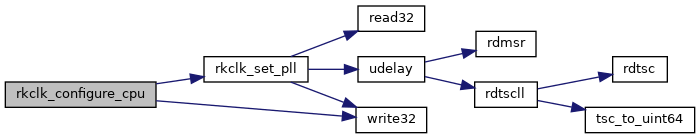

| void rkclk_configure_cpu | ( | enum apll_frequencies | freq, |

| enum cpu_cluster | cluster | ||

| ) |

Definition at line 566 of file clock.c.

References ACLKM_CORE_DIV_CON_MASK, ACLKM_CORE_DIV_CON_SHIFT, ACLKM_CORE_HZ, apll_cfgs, ATCLK_CORE_DIV_MASK, ATCLK_CORE_DIV_SHIFT, ATCLK_CORE_HZ, CLK_CORE_DIV_MASK, CLK_CORE_DIV_SHIFT, CLK_CORE_PLL_SEL_ABPLL, CLK_CORE_PLL_SEL_ALPLL, CLK_CORE_PLL_SEL_MASK, CLK_CORE_PLL_SEL_SHIFT, CPU_CLUSTER_BIG, CPU_CLUSTER_LITTLE, cru_ptr, DIV_ROUND_UP, pll_div::freq, PCLK_DBG_DIV_MASK, PCLK_DBG_DIV_SHIFT, PCLK_DBG_HZ, RK_CLRSETBITS, rkclk_set_pll(), and write32().

Definition at line 609 of file clock.c.

References CONFIG, cru_ptr, rk3399_pmusgrf_regs::ddr_rgn_con, die(), MHz, pll_div::refdiv, rk3399_pmusgrf, rkclk_set_dpllssc(), rkclk_set_pll(), and write32().

Definition at line 927 of file clock.c.

References assert, CLK_PCLK_EDP_DIV_CON_MASK, CLK_PCLK_EDP_DIV_CON_SHIFT, CLK_PCLK_EDP_PLL_SEL_CPLL, CLK_PCLK_EDP_PLL_SEL_MASK, CLK_PCLK_EDP_PLL_SEL_SHIFT, CPLL_HZ, cru_ptr, RK_CLRSETBITS, and write32().

Definition at line 892 of file clock.c.

References ACLK_EMMC_DIV_CON_MASK, ACLK_EMMC_DIV_CON_SHIFT, ACLK_EMMC_PLL_SEL_GPLL, ACLK_EMMC_PLL_SEL_MASK, ACLK_EMMC_PLL_SEL_SHIFT, assert, CLK_EMMC_DIV_CON_MASK, CLK_EMMC_DIV_CON_SHIFT, CLK_EMMC_PLL_MASK, CLK_EMMC_PLL_SEL_GPLL, CLK_EMMC_PLL_SHIFT, cru_ptr, GPLL_HZ, KHz, RK_CLRSETBITS, and write32().

Referenced by configure_emmc().

clk_i2s0_sel: divider output from fraction clk_i2s0_pll_sel source clock: cpll clk_i2s0_div_con: 1 (div+1)

clk_i2sout_sel clk_i2s clk_i2s_ch_sel: clk_i2s0

Definition at line 789 of file clock.c.

References assert, clk_gcd(), CPLL_HZ, cru_ptr, RK_CLRBITS, RK_CLRSETBITS, and write32().

Definition at line 945 of file clock.c.

References cru_ptr, RK_CLRBITS, and write32().

Referenced by rk_display_init().

Definition at line 823 of file clock.c.

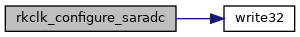

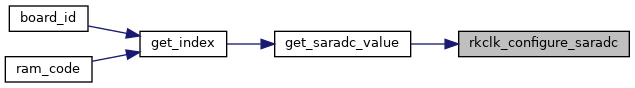

References assert, CLK_SARADC_DIV_CON_MASK, CLK_SARADC_DIV_CON_SHIFT, cru_ptr, MHz, RK_CLRSETBITS, and write32().

Referenced by get_saradc_value().

Definition at line 664 of file clock.c.

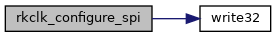

References assert, BIOS_ERR, cru_ptr, GPLL_HZ, rk3399_pmucru_reg::pmucru_clksel, pmucru_ptr, PPLL_HZ, printk, RK_CLRSETBITS, SPI3_DIV_CON_MASK, SPI3_DIV_CON_SHIFT, SPI3_PLL_SEL_MASK, SPI3_PLL_SEL_PPLL, SPI3_PLL_SEL_SHIFT, SPI_CLK_REG_VALUE, and write32().

Definition at line 877 of file clock.c.

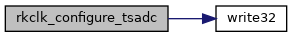

References assert, CLK_TSADC_DIV_CON_MASK, CLK_TSADC_DIV_CON_SHIFT, CLK_TSADC_SEL_MASK, CLK_TSADC_SEL_SHIFT, CLK_TSADC_SEL_X24M, cru_ptr, OSC_HZ, RK_CLRSETBITS, and write32().

Definition at line 837 of file clock.c.

References ACLK_VOP_DIV_CON_MASK, ACLK_VOP_DIV_CON_SHIFT, ACLK_VOP_PLL_SEL_CPLL, ACLK_VOP_PLL_SEL_MASK, ACLK_VOP_PLL_SEL_SHIFT, assert, CPLL_HZ, cru_ptr, RK_CLRSETBITS, and write32().

Definition at line 854 of file clock.c.

References cru_ptr, DCLK_VOP_DCLK_SEL_DIVOUT, DCLK_VOP_DCLK_SEL_MASK, DCLK_VOP_DCLK_SEL_SHIFT, DCLK_VOP_DIV_CON_MASK, DCLK_VOP_DIV_CON_SHIFT, DCLK_VOP_PLL_SEL_MASK, DCLK_VOP_PLL_SEL_SHIFT, DCLK_VOP_PLL_SEL_VPLL, pll_para_config(), RK_CLRSETBITS, rkclk_set_pll(), and write32().

Definition at line 647 of file clock.c.

References ch, cru_ptr, RESETN_DDR_REQ_SHIFT, RESETN_DDRPHY_REQ_SHIFT, RK_CLRSETBITS, and write32().

Definition at line 720 of file clock.c.

References assert, cru_ptr, die(), GPLL_HZ, I2C_CLK_REG_VALUE, MHz, PMU_I2C_CLK_REG_VALUE, rk3399_pmucru_reg::pmucru_clksel, pmucru_ptr, PPLL_HZ, and write32().

Definition at line 461 of file clock.c.

References ACLK_PERIHP_DIV_CON_MASK, ACLK_PERIHP_DIV_CON_SHIFT, ACLK_PERIHP_PLL_SEL_GPLL, ACLK_PERIHP_PLL_SEL_MASK, ACLK_PERIHP_PLL_SEL_SHIFT, ACLK_PERILP0_DIV_CON_MASK, ACLK_PERILP0_DIV_CON_SHIFT, ACLK_PERILP0_PLL_SEL_GPLL, ACLK_PERILP0_PLL_SEL_MASK, ACLK_PERILP0_PLL_SEL_SHIFT, assert, cpll_init_cfg, cru_ptr, GPLL_HZ, gpll_init_cfg, HCLK_PERIHP_DIV_CON_MASK, HCLK_PERIHP_DIV_CON_SHIFT, HCLK_PERILP0_DIV_CON_MASK, HCLK_PERILP0_DIV_CON_SHIFT, HCLK_PERILP1_DIV_CON_MASK, HCLK_PERILP1_DIV_CON_SHIFT, HCLK_PERILP1_PLL_SEL_GPLL, HCLK_PERILP1_PLL_SEL_MASK, HCLK_PERILP1_PLL_SEL_SHIFT, PCLK_PERIHP_DIV_CON_MASK, PCLK_PERIHP_DIV_CON_SHIFT, PCLK_PERILP0_DIV_CON_MASK, PCLK_PERILP0_DIV_CON_SHIFT, PCLK_PERILP1_DIV_CON_MASK, PCLK_PERILP1_DIV_CON_SHIFT, PERIHP_ACLK_HZ, PERIHP_HCLK_HZ, PERIHP_PCLK_HZ, PERILP0_ACLK_HZ, PERILP0_HCLK_HZ, PERILP0_PCLK_HZ, PERILP1_HCLK_HZ, PERILP1_PCLK_HZ, PMU_PCLK_DIV_CON_MASK, PMU_PCLK_DIV_CON_SHIFT, PMU_PCLK_HZ, rk3399_pmucru_reg::pmucru_clksel, pmucru_ptr, rk3399_pmucru_reg::ppll_con, PPLL_HZ, ppll_init_cfg, RK_CLRSETBITS, rkclk_set_pll(), and write32().

Definition at line 336 of file clock.c.

References assert, clrsetbits32, cru_ptr, KHz, OSC_HZ, PLL_DSMPD_MASK, PLL_DSMPD_SHIFT, PLL_FRAC_MODE, PLL_FRACDIV_MASK, PLL_FRACDIV_SHIFT, PLL_SSMOD_BP_MASK, PLL_SSMOD_BP_SHIFT, PLL_SSMOD_DIS_SSCG_MASK, PLL_SSMOD_DIS_SSCG_SHIFT, PLL_SSMOD_DIVVAL_MASK, PLL_SSMOD_DIVVAL_SHIFT, PLL_SSMOD_RESET_MASK, PLL_SSMOD_RESET_SHIFT, PLL_SSMOD_SPREADAMP_MASK, PLL_SSMOD_SPREADAMP_SHIFT, pll_div::refdiv, RK_CLRBITS, RK_CLRSETBITS, udelay(), and write32().

Referenced by rkclk_configure_ddr().

Definition at line 281 of file clock.c.

References assert, BIOS_DEBUG, pll_div::fbdiv, OSC_HZ, OUTPUT_MAX_KHZ, OUTPUT_MIN_KHZ, PLL_DIV_MAX, PLL_DIV_MIN, PLL_DSMPD_MASK, PLL_DSMPD_SHIFT, PLL_FBDIV_MASK, PLL_FBDIV_SHIFT, PLL_INTEGER_MODE, PLL_LOCK_STATUS_SHIFT, PLL_MODE_MASK, PLL_MODE_NORM, PLL_MODE_SHIFT, PLL_MODE_SLOW, PLL_POSTDIV1_MASK, PLL_POSTDIV1_SHIFT, PLL_POSTDIV2_MASK, PLL_POSTDIV2_SHIFT, PLL_REFDIV_MASK, PLL_REFDIV_SHIFT, pll_div::postdiv1, pll_div::postdiv2, printk, read32(), pll_div::refdiv, RK_CLRSETBITS, udelay(), VCO_MAX_KHZ, VCO_MIN_KHZ, and write32().

Referenced by rkclk_configure_cpu(), rkclk_configure_ddr(), rkclk_configure_vop_dclk(), and rkclk_init().

| int rkclk_was_watchdog_reset | ( | void | ) |

|

static |

|

static |

|

static |

Definition at line 40 of file clock.c.

Referenced by rkclk_configure_cpu().

|

static |

Definition at line 1 of file clock.c.

Referenced by rkclk_init().

|

static |

Definition at line 1 of file clock.c.

Referenced by rkclk_init().

|

static |

Definition at line 1 of file clock.c.

Referenced by rkclk_init().