|

coreboot

coreboot is an Open Source project aimed at replacing the proprietary BIOS found in most computers.

|

|

coreboot

coreboot is an Open Source project aimed at replacing the proprietary BIOS found in most computers.

|

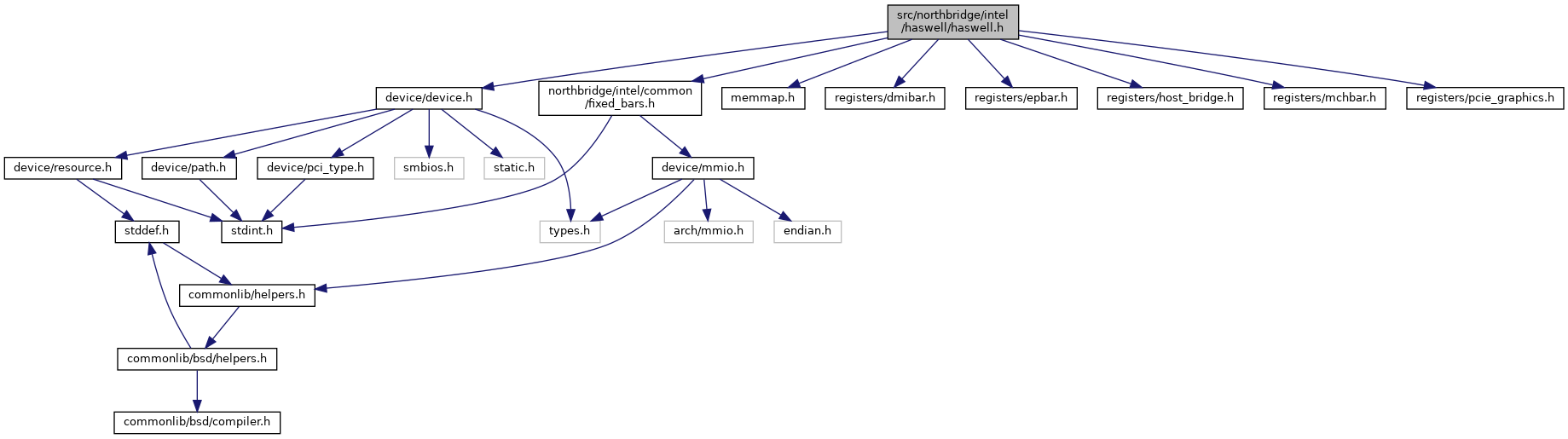

#include <device/device.h>#include <northbridge/intel/common/fixed_bars.h>#include "memmap.h"#include "registers/dmibar.h"#include "registers/epbar.h"#include "registers/host_bridge.h"#include "registers/mchbar.h"#include "registers/pcie_graphics.h"

Go to the source code of this file.

Macros | |

| #define | HOST_BRIDGE PCI_DEV(0, 0, 0) |

| #define | MSAC 0x62 /* Multi Size Aperture Control */ |

| #define | ARCHDIS 0xff0 /* DMA Remap Engine Policy Control */ |

| #define | DMAR_LCKDN (1 << 31) |

| #define | SPCAPCTRL (1 << 25) |

| #define | L3HIT2PEND_DIS (1 << 20) |

| #define | PRSCAPDIS (1 << 2) |

| #define | GLBIOTLBINV (1 << 1) |

| #define | GLBCTXTINV (1 << 0) |

Functions | |

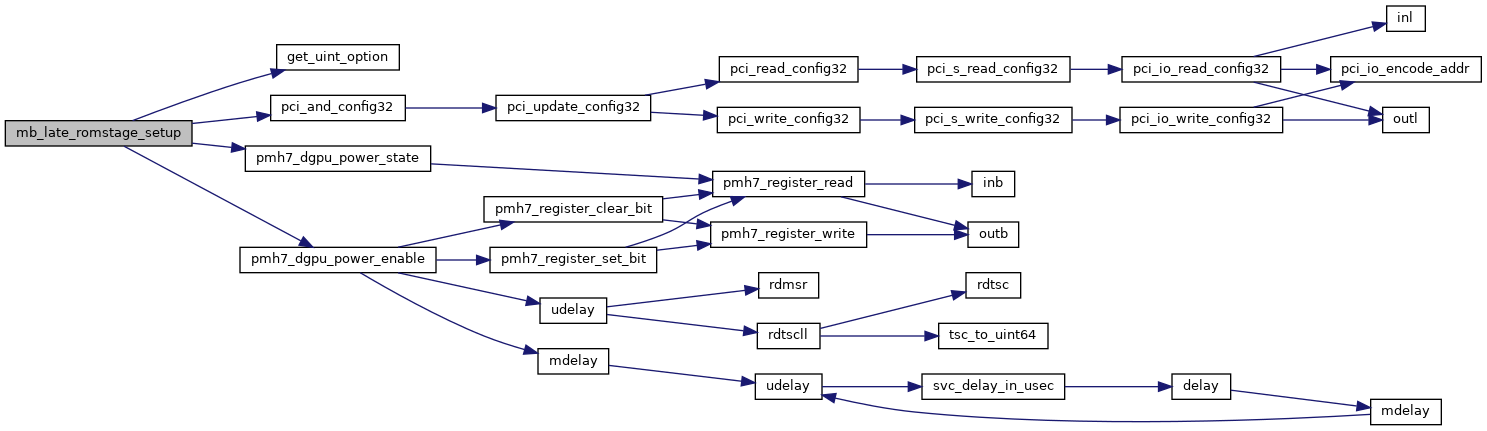

| void | mb_late_romstage_setup (void) |

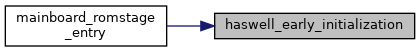

| void | haswell_early_initialization (void) |

| void | haswell_late_initialization (void) |

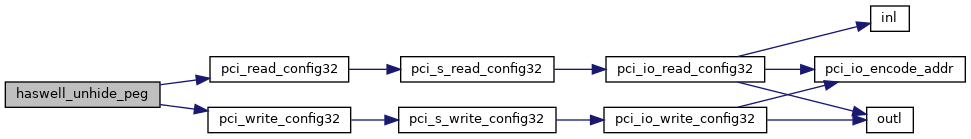

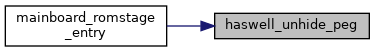

| void | haswell_unhide_peg (void) |

| void | report_platform_info (void) |

| unsigned long | northbridge_write_acpi_tables (const struct device *device, unsigned long start, struct acpi_rsdp *rsdp) |

| #define ARCHDIS 0xff0 /* DMA Remap Engine Policy Control */ |

Definition at line 183 of file early_init.c.

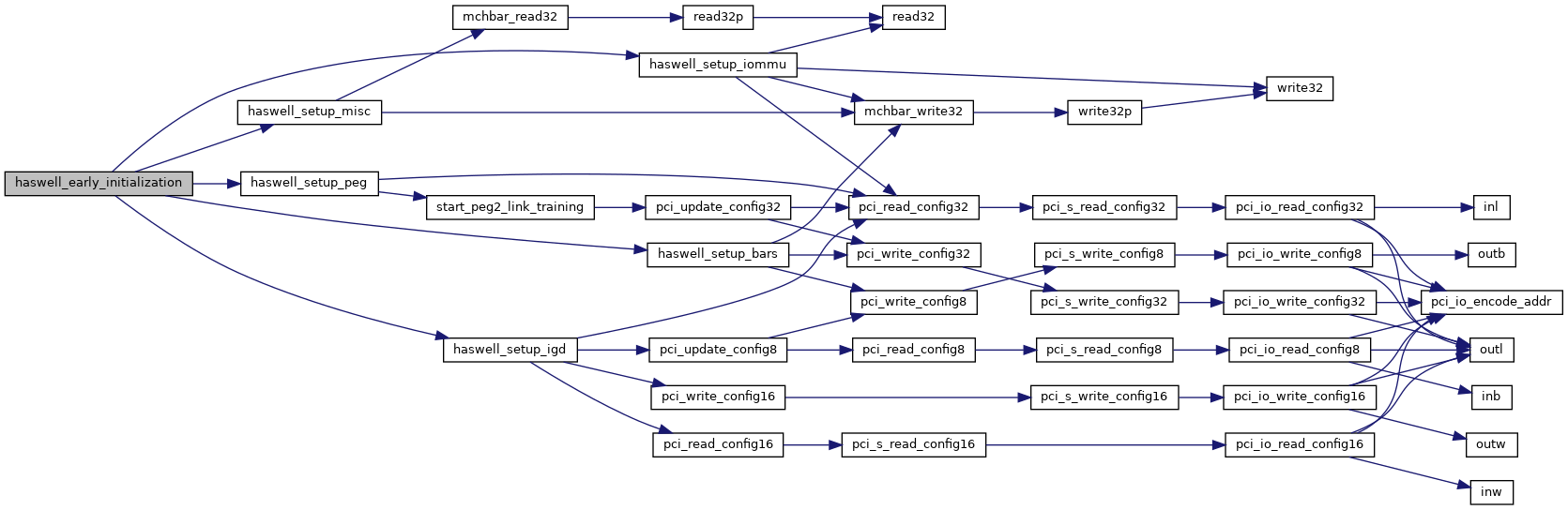

References haswell_setup_bars(), haswell_setup_igd(), haswell_setup_iommu(), haswell_setup_misc(), and haswell_setup_peg().

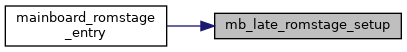

Referenced by mainboard_romstage_entry().

Definition at line 110 of file early_init.c.

References BIOS_DEBUG, DEVEN, DEVEN_D1F0EN, HOST_BRIDGE, pci_read_config32(), pci_write_config32(), peg_hidden, and printk.

Referenced by mainboard_romstage_entry().

Definition at line 23 of file romstage.c.

References DEVEN, DEVEN_D1F0EN, get_uint_option(), HOST_BRIDGE, pci_and_config32(), pmh7_dgpu_power_enable(), and pmh7_dgpu_power_state().

Referenced by mainboard_romstage_entry().

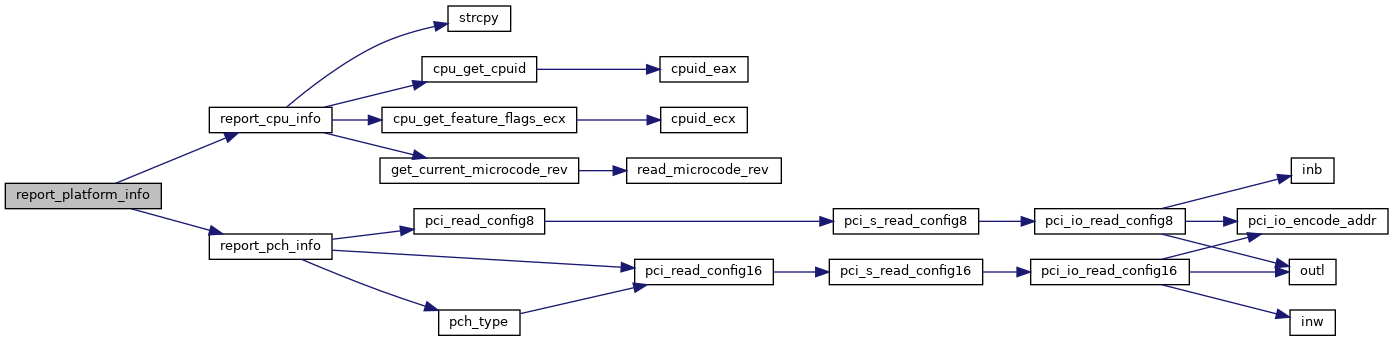

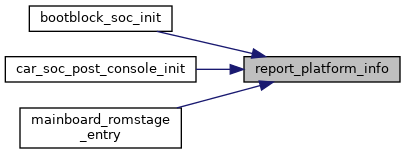

Definition at line 92 of file report_platform.c.

References report_cpu_info(), and report_pch_info().

Referenced by bootblock_soc_init(), car_soc_post_console_init(), and mainboard_romstage_entry().