|

coreboot

coreboot is an Open Source project aimed at replacing the proprietary BIOS found in most computers.

|

|

coreboot

coreboot is an Open Source project aimed at replacing the proprietary BIOS found in most computers.

|

#include <types.h>

Go to the source code of this file.

Data Structures | |

| struct | cpuid_result |

| struct | cpu_device_id |

| struct | cpu_driver |

| struct | cpu_info |

| struct | per_cpu_segment_data |

| struct | cpuinfo_x86 |

| struct | cpu_cache_info |

Macros | |

| #define | X86_EFLAGS_CF 0x00000001 /* Carry Flag */ |

| #define | X86_EFLAGS_PF 0x00000004 /* Parity Flag */ |

| #define | X86_EFLAGS_AF 0x00000010 /* Auxiliary carry Flag */ |

| #define | X86_EFLAGS_ZF 0x00000040 /* Zero Flag */ |

| #define | X86_EFLAGS_SF 0x00000080 /* Sign Flag */ |

| #define | X86_EFLAGS_TF 0x00000100 /* Trap Flag */ |

| #define | X86_EFLAGS_IF 0x00000200 /* Interrupt Flag */ |

| #define | X86_EFLAGS_DF 0x00000400 /* Direction Flag */ |

| #define | X86_EFLAGS_OF 0x00000800 /* Overflow Flag */ |

| #define | X86_EFLAGS_IOPL 0x00003000 /* IOPL mask */ |

| #define | X86_EFLAGS_NT 0x00004000 /* Nested Task */ |

| #define | X86_EFLAGS_RF 0x00010000 /* Resume Flag */ |

| #define | X86_EFLAGS_VM 0x00020000 /* Virtual Mode */ |

| #define | X86_EFLAGS_AC 0x00040000 /* Alignment Check */ |

| #define | X86_EFLAGS_VIF 0x00080000 /* Virtual Interrupt Flag */ |

| #define | X86_EFLAGS_VIP 0x00100000 /* Virtual Interrupt Pending */ |

| #define | X86_EFLAGS_ID 0x00200000 /* CPUID detection flag */ |

| #define | X86_VENDOR_INVALID 0 |

| #define | X86_VENDOR_INTEL 1 |

| #define | X86_VENDOR_CYRIX 2 |

| #define | X86_VENDOR_AMD 3 |

| #define | X86_VENDOR_UMC 4 |

| #define | X86_VENDOR_NEXGEN 5 |

| #define | X86_VENDOR_CENTAUR 6 |

| #define | X86_VENDOR_RISE 7 |

| #define | X86_VENDOR_TRANSMETA 8 |

| #define | X86_VENDOR_NSC 9 |

| #define | X86_VENDOR_SIS 10 |

| #define | X86_VENDOR_HYGON 11 |

| #define | X86_VENDOR_ANY 0xfe |

| #define | X86_VENDOR_UNKNOWN 0xff |

| #define | CPUID_FEATURE_PAE (1 << 6) |

| #define | CPUID_FEATURE_PSE36 (1 << 17) |

| #define | CPUID_FEAURE_HTT (1 << 28) |

| #define | CPUID_CACHE(x, res) (((res) >> CPUID_CACHE_##x##_SHIFT) & CPUID_CACHE_##x##_MASK) |

| #define | CPUID_CACHE_SHARING_CACHE_SHIFT 14 |

| #define | CPUID_CACHE_SHARING_CACHE_MASK 0xfff |

| #define | CPUID_CACHE_SHARING_CACHE(res) CPUID_CACHE(SHARING_CACHE, (res).eax) |

| #define | CPUID_CACHE_FULL_ASSOC_SHIFT 9 |

| #define | CPUID_CACHE_FULL_ASSOC_MASK 0x1 |

| #define | CPUID_CACHE_FULL_ASSOC(res) CPUID_CACHE(FULL_ASSOC, (res).eax) |

| #define | CPUID_CACHE_SELF_INIT_SHIFT 8 |

| #define | CPUID_CACHE_SELF_INIT_MASK 0x1 |

| #define | CPUID_CACHE_SELF_INIT(res) CPUID_CACHE(SELF_INIT, (res).eax) |

| #define | CPUID_CACHE_LEVEL_SHIFT 5 |

| #define | CPUID_CACHE_LEVEL_MASK 0x7 |

| #define | CPUID_CACHE_LEVEL(res) CPUID_CACHE(LEVEL, (res).eax) |

| #define | CPUID_CACHE_TYPE_SHIFT 0 |

| #define | CPUID_CACHE_TYPE_MASK 0x1f |

| #define | CPUID_CACHE_TYPE(res) CPUID_CACHE(TYPE, (res).eax) |

| #define | CPUID_CACHE_WAYS_OF_ASSOC_SHIFT 22 |

| #define | CPUID_CACHE_WAYS_OF_ASSOC_MASK 0x3ff |

| #define | CPUID_CACHE_WAYS_OF_ASSOC(res) CPUID_CACHE(WAYS_OF_ASSOC, (res).ebx) |

| #define | CPUID_CACHE_PHYS_LINE_SHIFT 12 |

| #define | CPUID_CACHE_PHYS_LINE_MASK 0x3ff |

| #define | CPUID_CACHE_PHYS_LINE(res) CPUID_CACHE(PHYS_LINE, (res).ebx) |

| #define | CPUID_CACHE_COHER_LINE_SHIFT 0 |

| #define | CPUID_CACHE_COHER_LINE_MASK 0xfff |

| #define | CPUID_CACHE_COHER_LINE(res) CPUID_CACHE(COHER_LINE, (res).ebx) |

| #define | CPUID_CACHE_NO_OF_SETS_SHIFT 0 |

| #define | CPUID_CACHE_NO_OF_SETS_MASK 0xffffffff |

| #define | CPUID_CACHE_NO_OF_SETS(res) CPUID_CACHE(NO_OF_SETS, (res).ecx) |

| #define | asmlinkage __attribute__((regparm(0))) |

| #define | DETERMINISTIC_CACHE_PARAMETERS_CPUID_IA 0x04 |

| #define | DETERMINISTIC_CACHE_PARAMETERS_CPUID_AMD 0x8000001d |

Enumerations | |

| enum | cache_level { CACHE_L1D = 0 , CACHE_L1I = 1 , CACHE_L2 = 2 , CACHE_L3 = 3 , CACHE_LINV = 0xFF } |

| enum | cpu_type { CPUID_COMMAND_UNSUPPORTED = 0 , CPUID_TYPE_AMD = 1 , CPUID_TYPE_INTEL = 2 , CPUID_TYPE_INVALID = 0xFF } |

| #define CPUID_CACHE_COHER_LINE | ( | res | ) | CPUID_CACHE(COHER_LINE, (res).ebx) |

| #define CPUID_CACHE_FULL_ASSOC | ( | res | ) | CPUID_CACHE(FULL_ASSOC, (res).eax) |

| #define CPUID_CACHE_LEVEL | ( | res | ) | CPUID_CACHE(LEVEL, (res).eax) |

| #define CPUID_CACHE_NO_OF_SETS | ( | res | ) | CPUID_CACHE(NO_OF_SETS, (res).ecx) |

| #define CPUID_CACHE_PHYS_LINE | ( | res | ) | CPUID_CACHE(PHYS_LINE, (res).ebx) |

| #define CPUID_CACHE_SELF_INIT | ( | res | ) | CPUID_CACHE(SELF_INIT, (res).eax) |

| #define CPUID_CACHE_SHARING_CACHE | ( | res | ) | CPUID_CACHE(SHARING_CACHE, (res).eax) |

| #define CPUID_CACHE_TYPE | ( | res | ) | CPUID_CACHE(TYPE, (res).eax) |

| #define CPUID_CACHE_WAYS_OF_ASSOC | ( | res | ) | CPUID_CACHE(WAYS_OF_ASSOC, (res).ebx) |

| #define X86_EFLAGS_VIP 0x00100000 /* Virtual Interrupt Pending */ |

| enum cache_level |

| enum cpu_type |

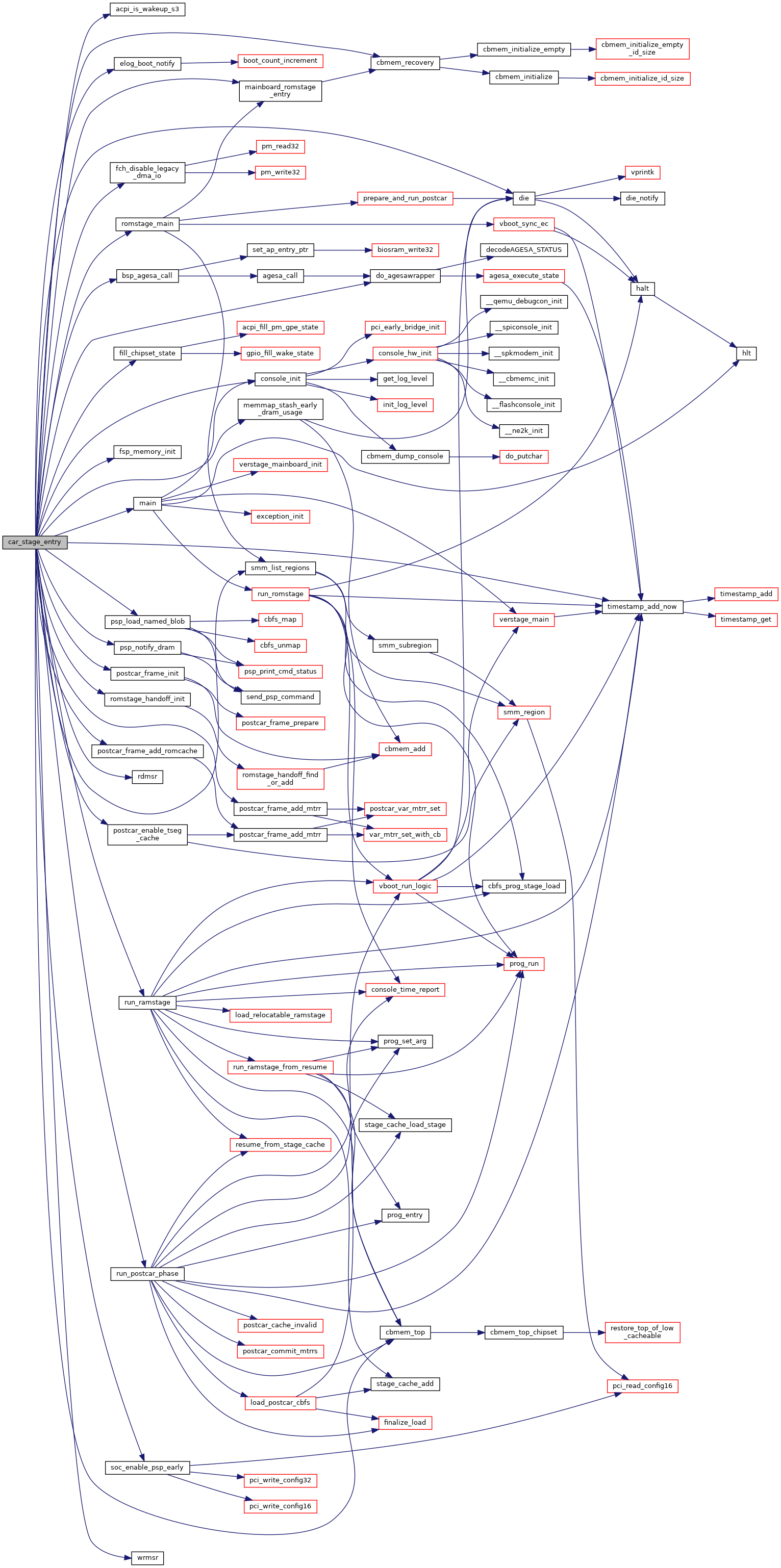

| asmlinkage void car_stage_entry | ( | void | ) |

Definition at line 7 of file verstage.c.

References acpi_is_wakeup_s3(), base, BIOS_CRIT, BIOS_ERR, BIOS_INFO, BLOB_SMU_FW, bsp_agesa_call(), cbmem_recovery(), cbmem_top(), CONFIG, console_init(), die(), do_agesawrapper(), elog_boot_notify(), fch_disable_legacy_dma_io(), fill_chipset_state(), fsp_memory_init(), msr_struct::lo, main(), mainboard_romstage_entry(), mask, memmap_stash_early_dram_usage(), MiB, MTRR_CAP_MSR, MTRR_CAP_VCNT, MTRR_PHYS_BASE, MTRR_PHYS_MASK, MTRR_PHYS_MASK_VALID, MTRR_TYPE_UNCACHEABLE, MTRR_TYPE_WRBACK, MTRR_TYPE_WRPROT, post_code, postcar_enable_tseg_cache(), postcar_frame_add_mtrr(), postcar_frame_add_romcache(), postcar_frame_init(), printk, psp_load_named_blob(), psp_notify_dram(), rdmsr(), romstage_handoff_init(), romstage_main(), run_postcar_phase(), run_ramstage(), smm_list_regions(), soc_enable_psp_early(), SYSCFG_MSR, SYSCFG_MSR_TOM2WB, timestamp_add_now(), TS_ROMSTAGE_START, and wrmsr().

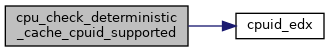

Definition at line 81 of file cpu_common.c.

References cpuid_edx().

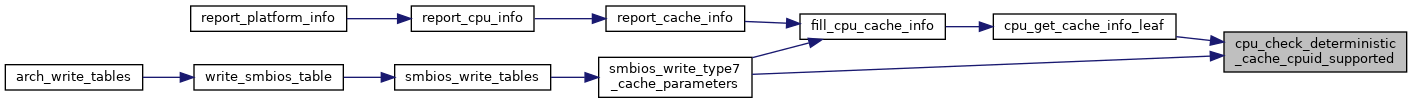

Referenced by cpu_get_cache_info_leaf(), and smbios_write_type7_cache_parameters().

Definition at line 41 of file cpu_common.c.

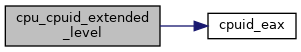

References cpuid_eax().

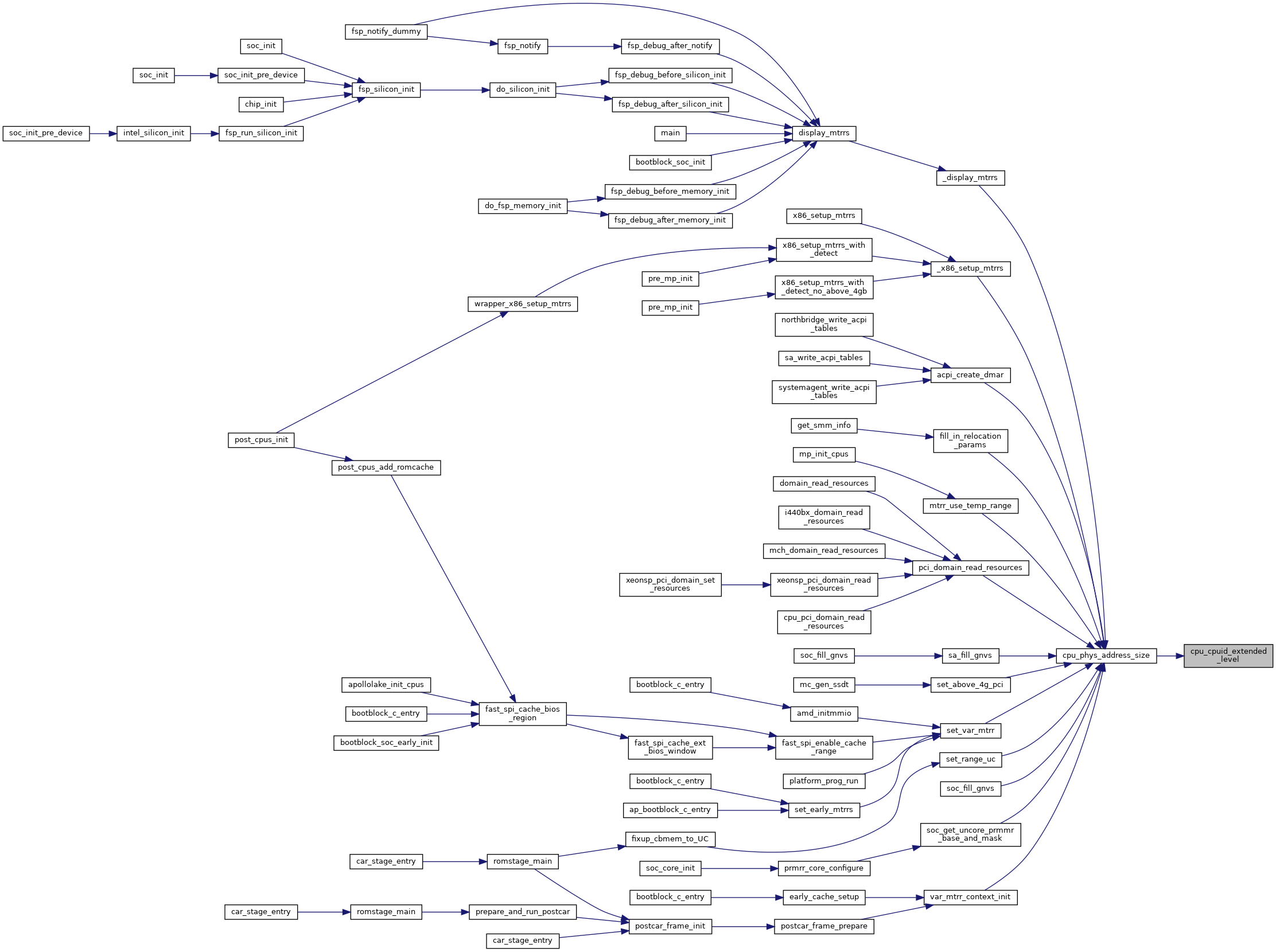

Referenced by cpu_phys_address_size().

| uint8_t cpu_get_cache_level | ( | const struct cpu_cache_info * | info | ) |

Definition at line 135 of file cpu_common.c.

References info.

| size_t cpu_get_cache_line_size | ( | const struct cpu_cache_info * | info | ) |

Definition at line 151 of file cpu_common.c.

References info.

| size_t cpu_get_cache_phy_partition_info | ( | const struct cpu_cache_info * | info | ) |

Definition at line 143 of file cpu_common.c.

References info.

| size_t cpu_get_cache_sets | ( | const struct cpu_cache_info * | info | ) |

Definition at line 159 of file cpu_common.c.

References info.

| uint8_t cpu_get_cache_type | ( | const struct cpu_cache_info * | info | ) |

Definition at line 127 of file cpu_common.c.

References info.

| size_t cpu_get_cache_ways_assoc_info | ( | const struct cpu_cache_info * | info | ) |

Definition at line 119 of file cpu_common.c.

References info.

Definition at line 63 of file cpu_common.c.

References cpuid_eax().

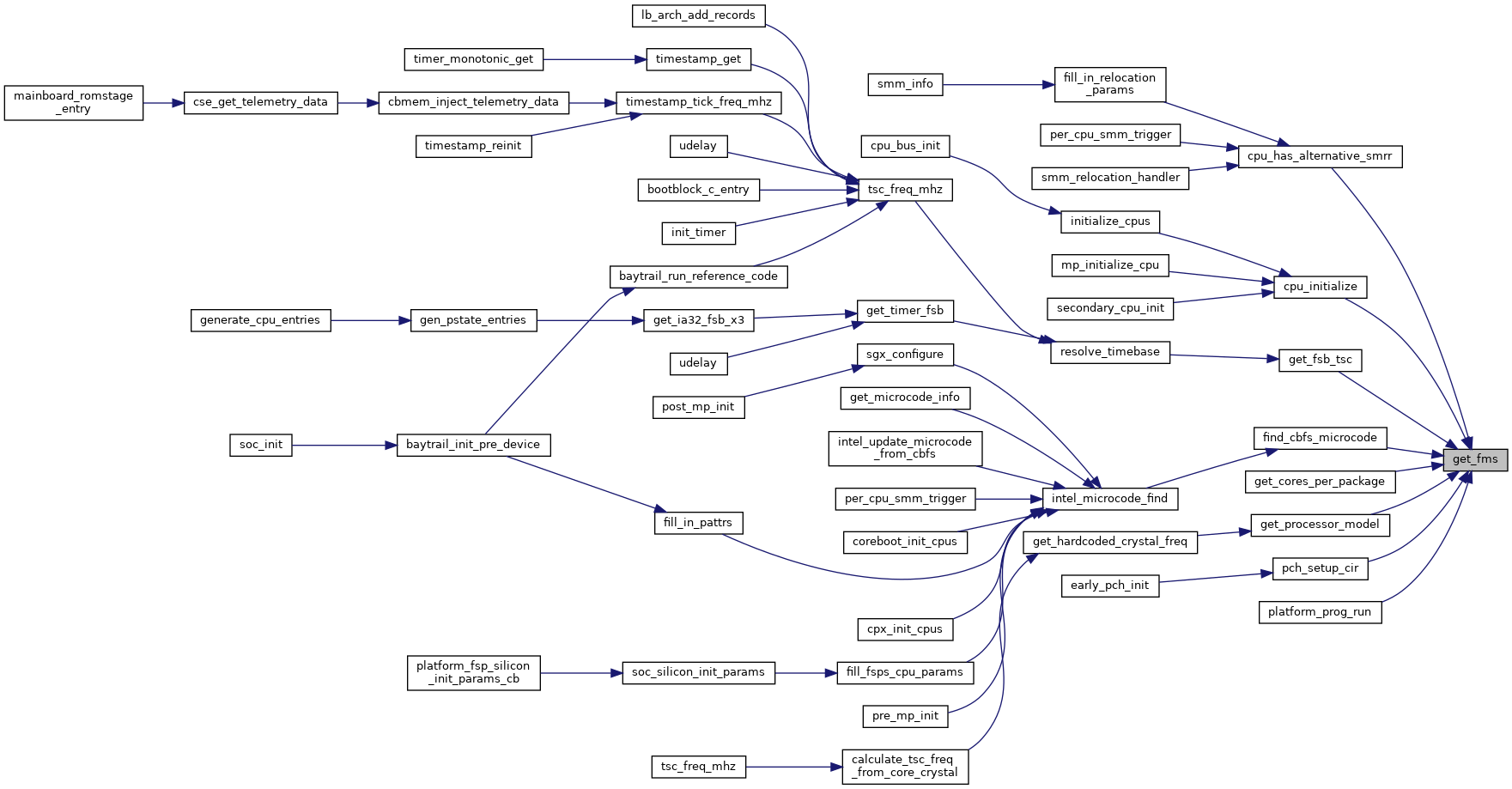

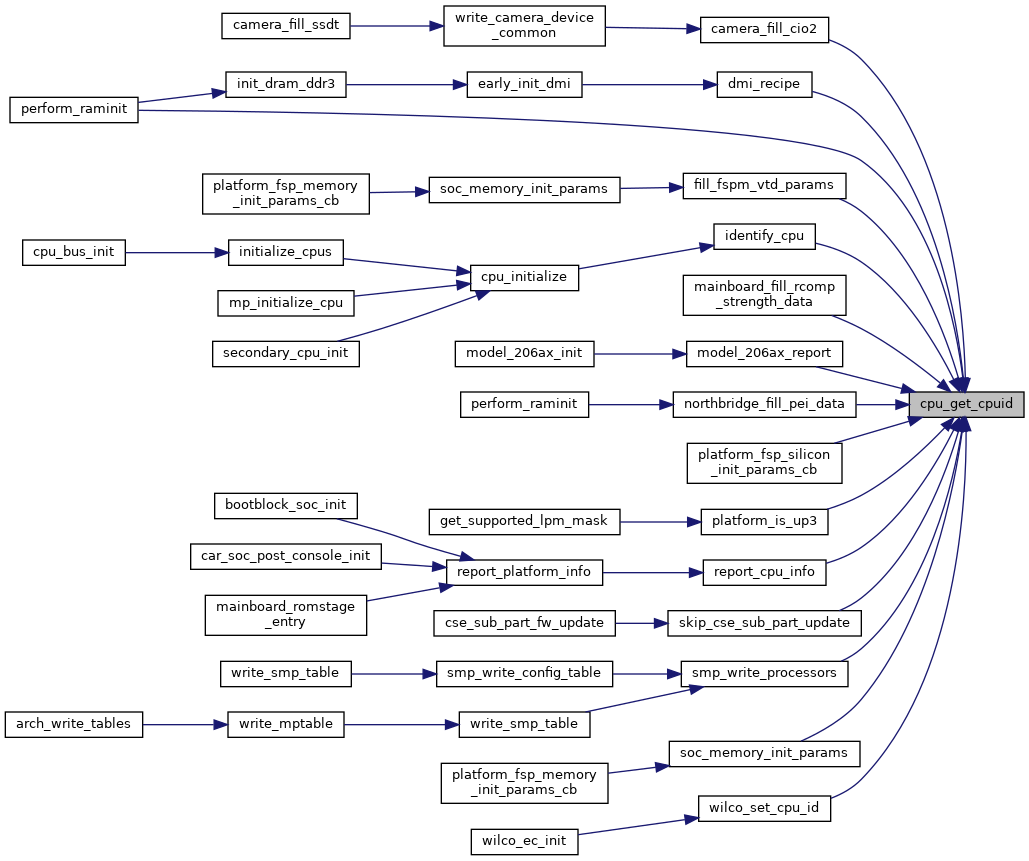

Referenced by camera_fill_cio2(), dmi_recipe(), fill_fspm_vtd_params(), identify_cpu(), mainboard_fill_rcomp_strength_data(), model_206ax_report(), northbridge_fill_pei_data(), perform_raminit(), platform_fsp_silicon_init_params_cb(), platform_is_up3(), report_cpu_info(), skip_cse_sub_part_update(), smp_write_processors(), soc_memory_init_params(), and wilco_set_cpu_id().

Definition at line 72 of file cpu_common.c.

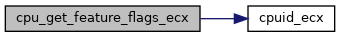

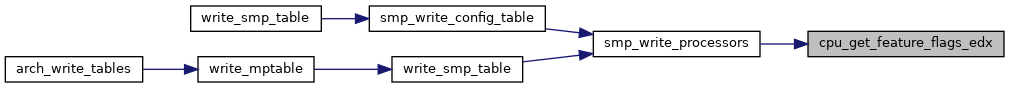

References cpuid_ecx().

Referenced by configure_dca_cap(), enable_lapic(), is_txt_cpu(), model_206ax_report(), report_cpu_info(), set_aesni_lock(), set_feature_ctrl_lock(), and set_feature_ctrl_vmx_arg().

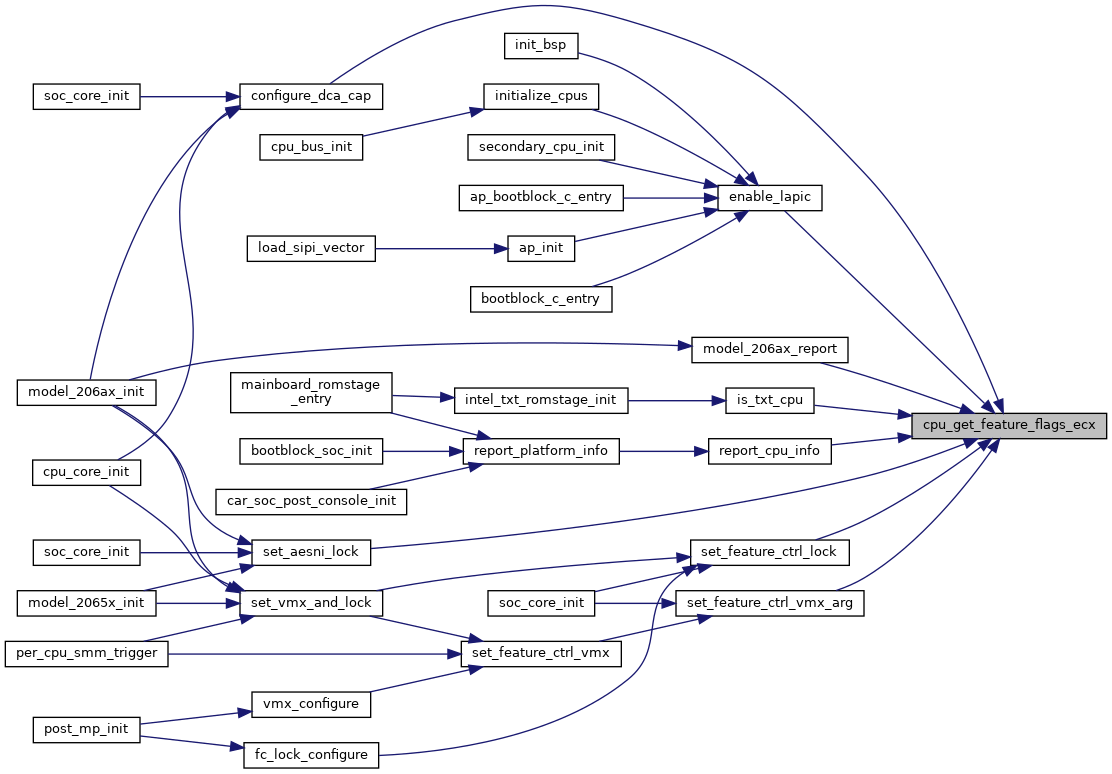

Definition at line 81 of file cpu_common.c.

Referenced by smp_write_processors().

| size_t cpu_get_max_cache_share | ( | const struct cpu_cache_info * | info | ) |

Definition at line 175 of file cpu_common.c.

References info.

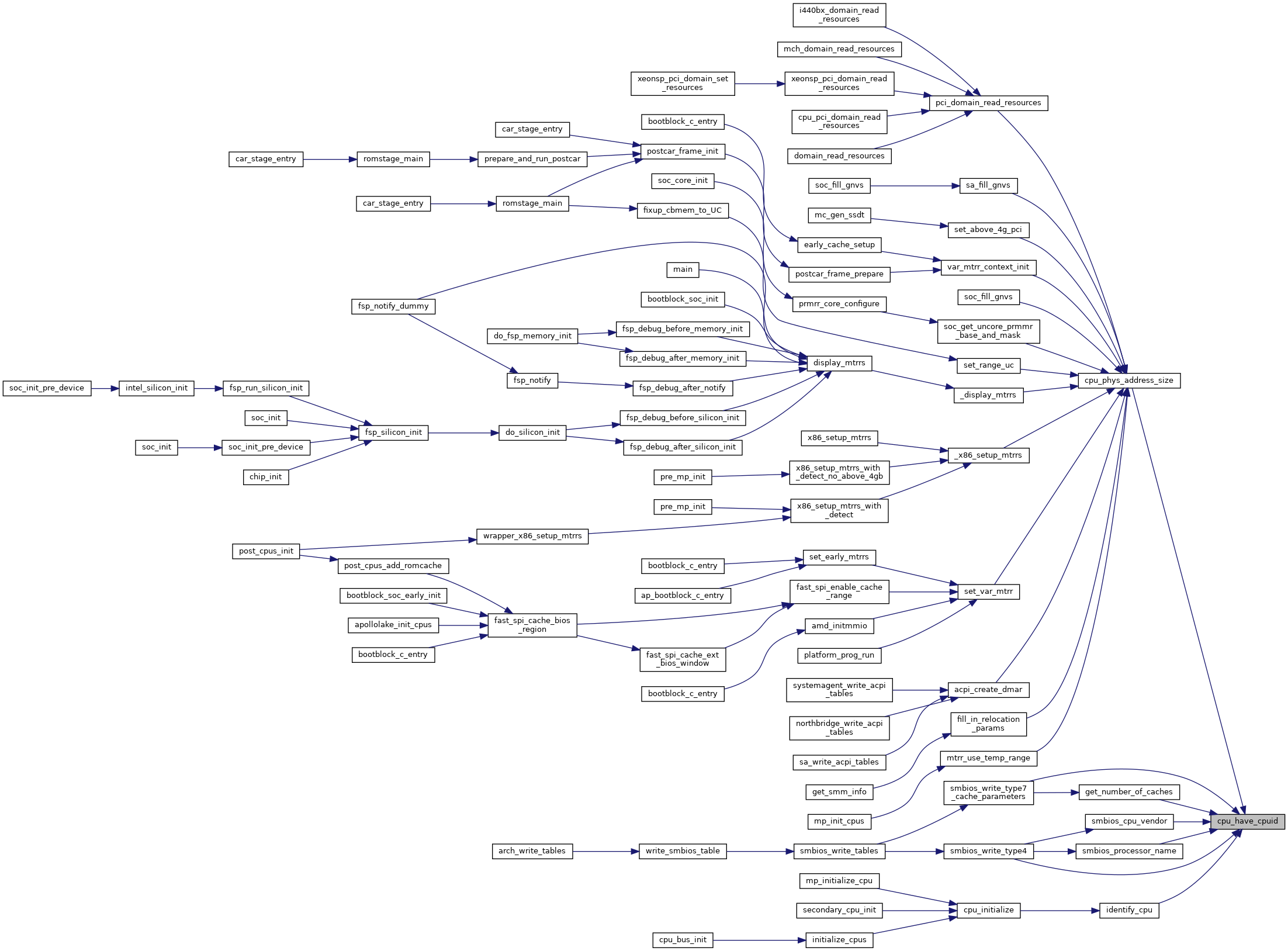

| int cpu_have_cpuid | ( | void | ) |

Definition at line 35 of file cpu_common.c.

Referenced by cpu_phys_address_size(), get_number_of_caches(), identify_cpu(), smbios_cpu_vendor(), smbios_processor_name(), smbios_write_type4(), and smbios_write_type7_cache_parameters().

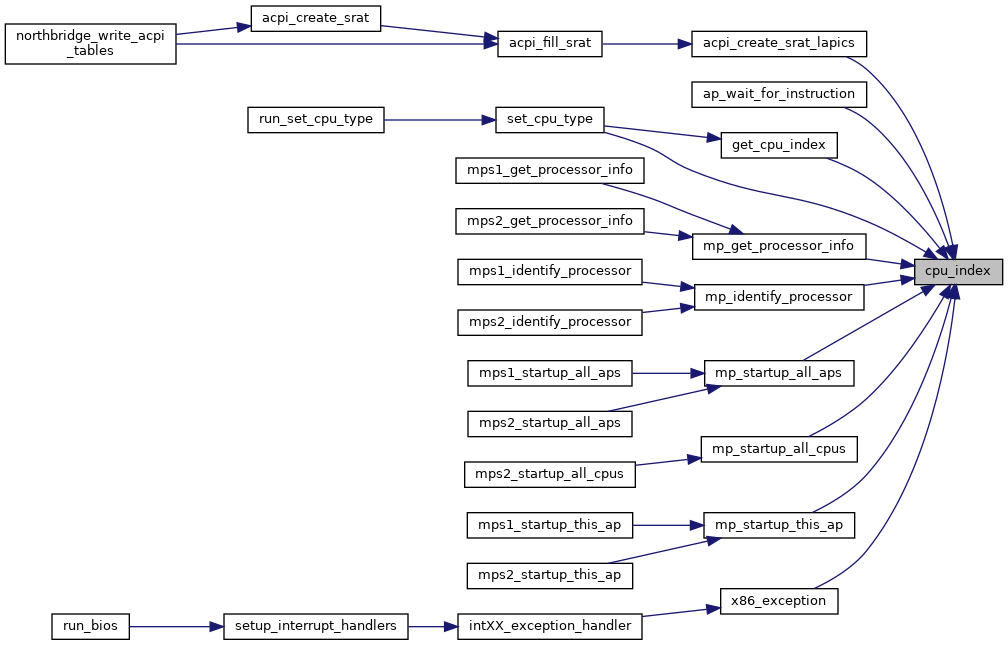

| int cpu_index | ( | void | ) |

Definition at line 332 of file cpu.c.

References cpu_get_apic_id(), and initial_lapicid().

Referenced by acpi_create_srat_lapics(), ap_wait_for_instruction(), get_cpu_index(), mp_get_processor_info(), mp_identify_processor(), mp_startup_all_aps(), mp_startup_all_cpus(), mp_startup_this_ap(), set_cpu_type(), and x86_exception().

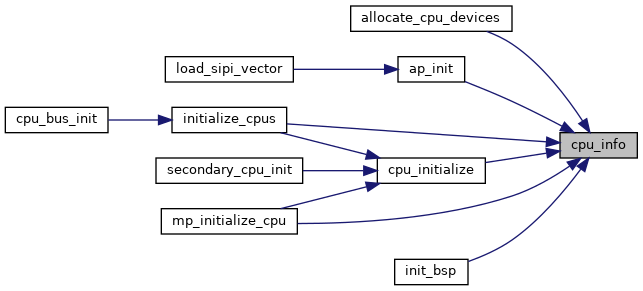

Definition at line 252 of file cpu.h.

References ALIGN_UP, info, NULL, offset, offsetof, and s.

Referenced by allocate_cpu_devices(), ap_init(), cpu_initialize(), init_bsp(), initialize_cpus(), and mp_initialize_cpu().

| bool cpu_is_cache_full_assoc | ( | const struct cpu_cache_info * | info | ) |

Definition at line 167 of file cpu_common.c.

References info.

|

static |

|

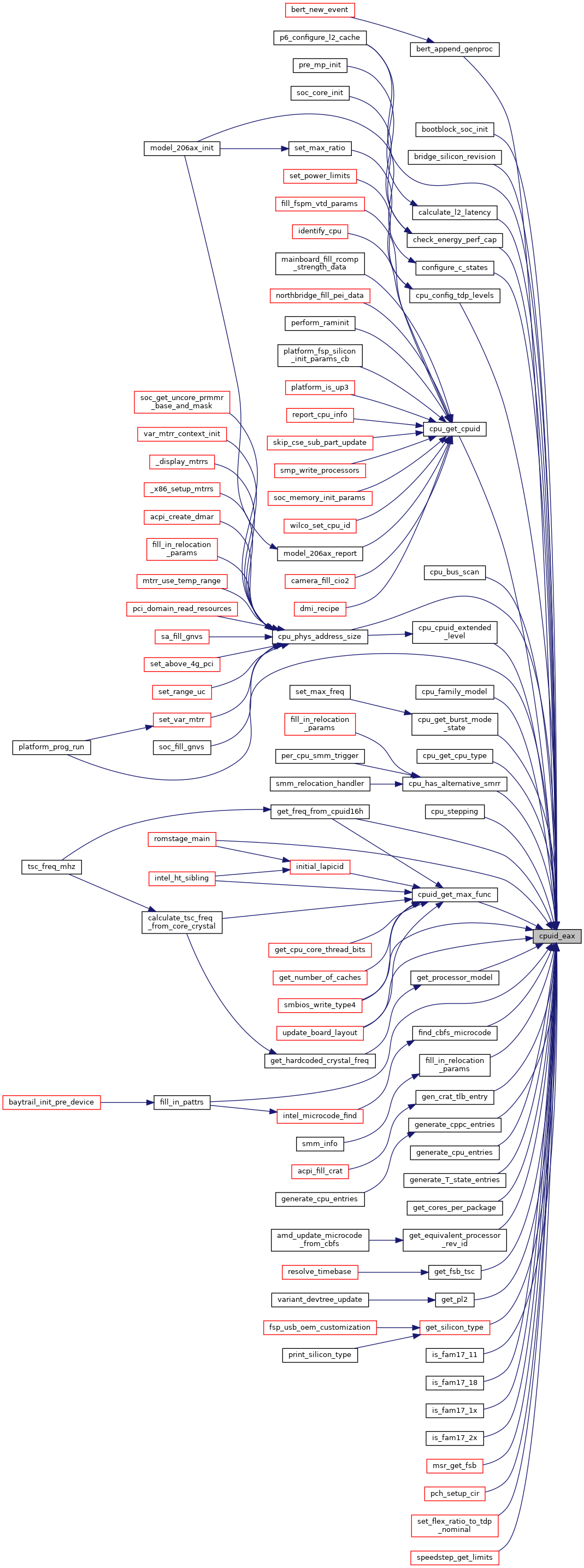

inlinestatic |

Definition at line 79 of file cpu.h.

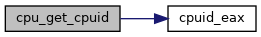

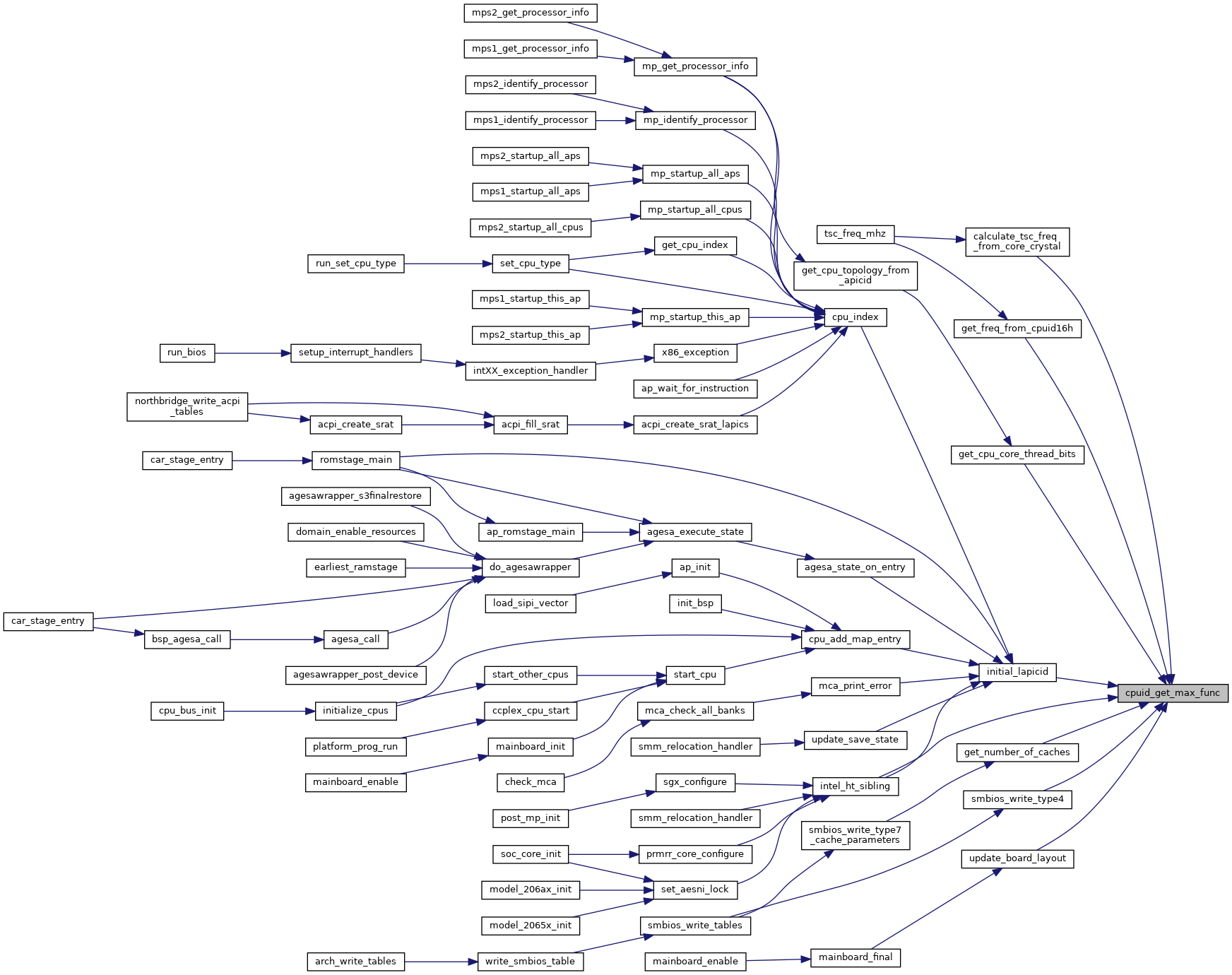

References cpuid_result::eax.

Referenced by bert_append_genproc(), bootblock_soc_init(), bridge_silicon_revision(), calculate_l2_latency(), check_energy_perf_cap(), configure_c_states(), cpu_bus_scan(), cpu_config_tdp_levels(), cpu_cpuid_extended_level(), cpu_family_model(), cpu_get_burst_mode_state(), cpu_get_cpu_type(), cpu_get_cpuid(), cpu_has_alternative_smrr(), cpu_phys_address_size(), cpu_stepping(), cpuid_get_max_func(), fill_in_pattrs(), fill_in_relocation_params(), find_cbfs_microcode(), gen_crat_tlb_entry(), generate_cppc_entries(), generate_cpu_entries(), generate_T_state_entries(), get_cores_per_package(), get_equivalent_processor_rev_id(), get_freq_from_cpuid16h(), get_fsb_tsc(), get_pl2(), get_processor_model(), get_silicon_type(), is_fam17_11(), is_fam17_18(), is_fam17_1x(), is_fam17_2x(), msr_get_fsb(), p6_configure_l2_cache(), pch_setup_cir(), platform_prog_run(), romstage_main(), set_flex_ratio_to_tdp_nominal(), smbios_write_type4(), speedstep_get_limits(), and update_board_layout().

Definition at line 92 of file cpu.h.

References cpuid_result::eax, and cpuid_result::ebx.

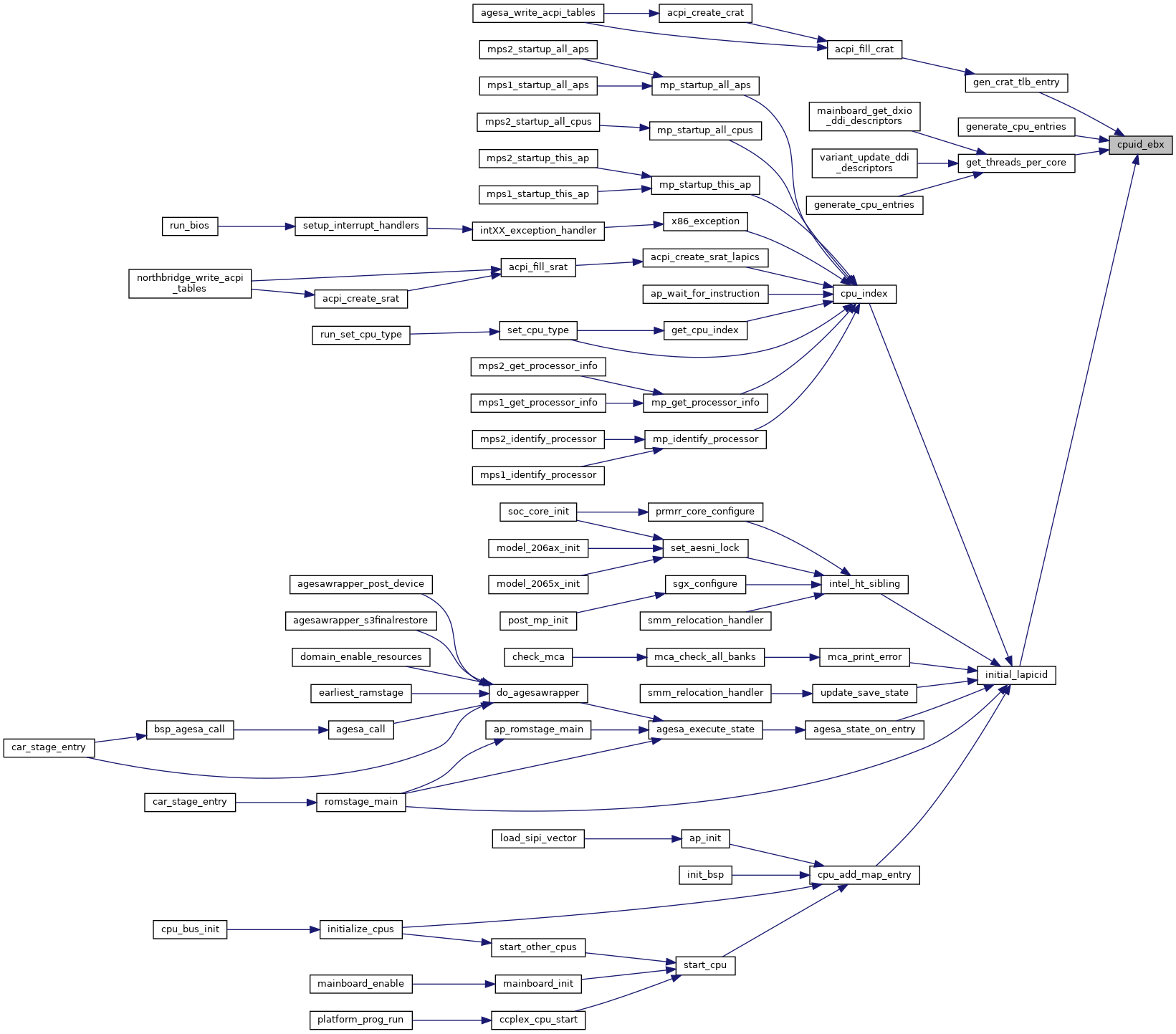

Referenced by gen_crat_tlb_entry(), generate_cpu_entries(), get_threads_per_core(), and initial_lapicid().

Definition at line 106 of file cpu.h.

References cpuid_result::eax, and cpuid_result::ecx.

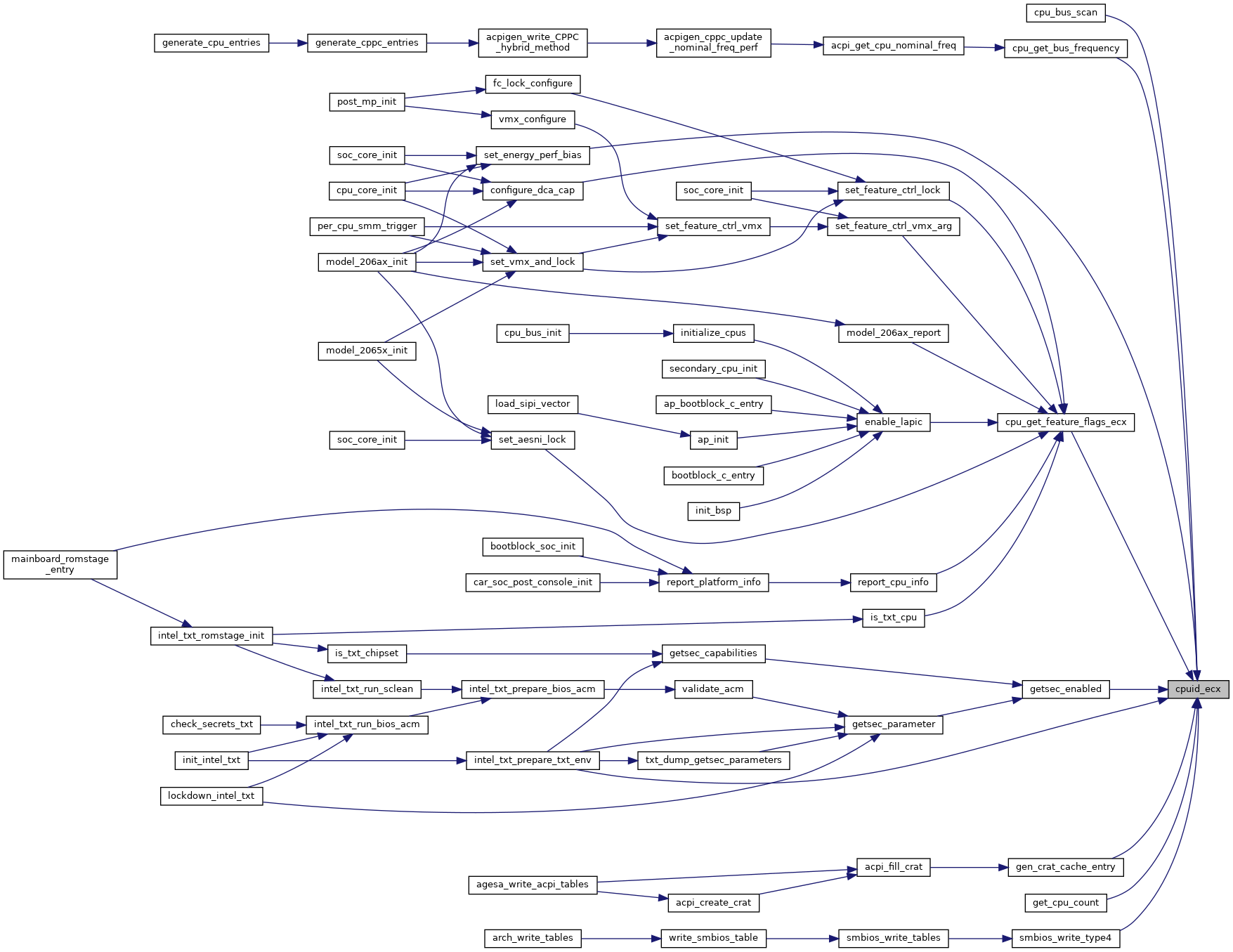

Referenced by cpu_bus_scan(), cpu_get_bus_frequency(), cpu_get_feature_flags_ecx(), gen_crat_cache_entry(), get_cpu_count(), getsec_enabled(), intel_txt_prepare_txt_env(), set_energy_perf_bias(), and smbios_write_type4().

Definition at line 119 of file cpu.h.

References cpuid_result::eax, and cpuid_result::edx.

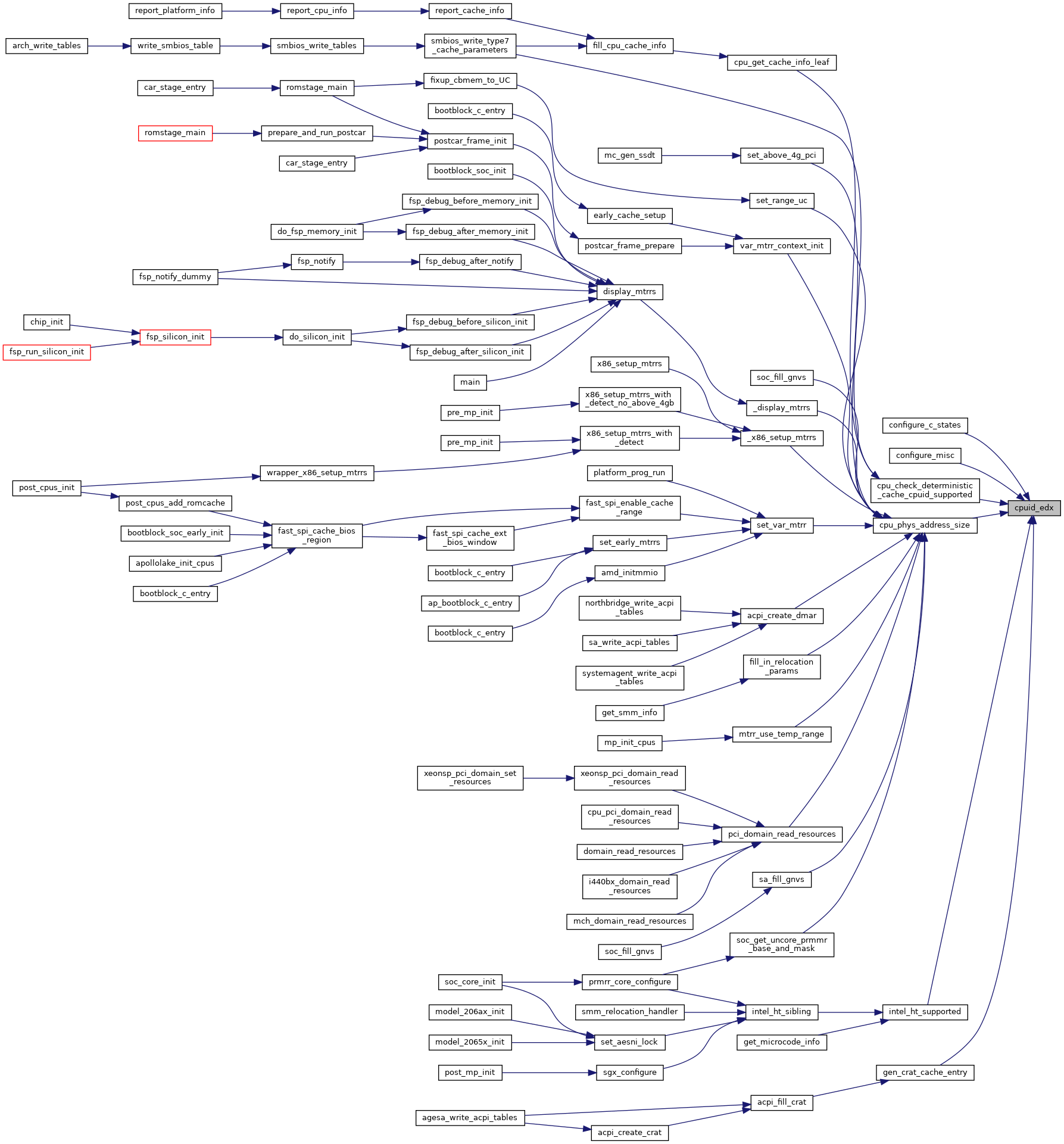

Referenced by configure_c_states(), configure_misc(), cpu_check_deterministic_cache_cpuid_supported(), cpu_phys_address_size(), gen_crat_cache_entry(), and intel_ht_supported().

|

inlinestatic |

Definition at line 1 of file cpu.h.

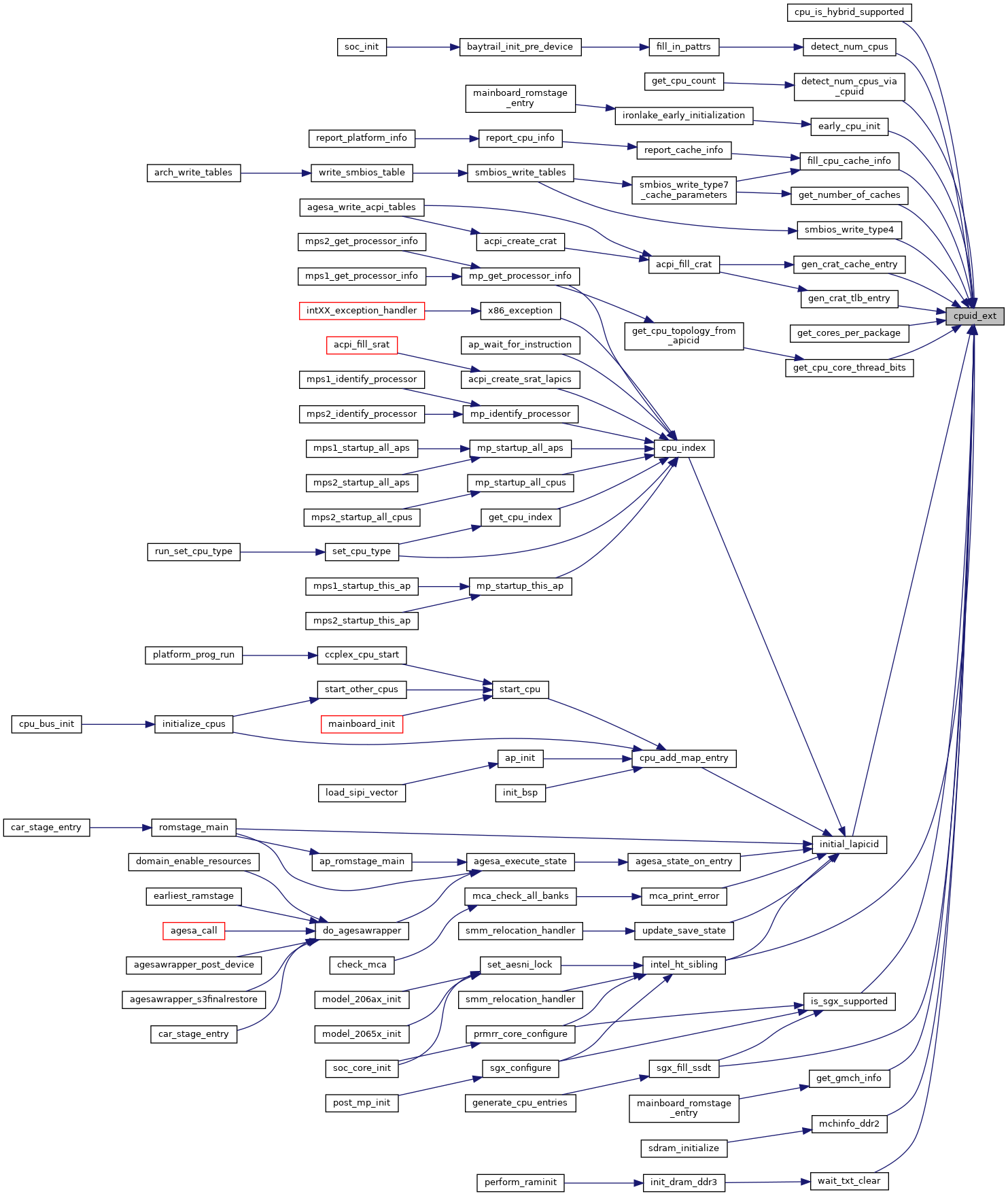

Referenced by cpu_is_hybrid_supported(), detect_num_cpus(), detect_num_cpus_via_cpuid(), early_cpu_init(), fill_cpu_cache_info(), gen_crat_cache_entry(), gen_crat_tlb_entry(), get_cores_per_package(), get_cpu_core_thread_bits(), get_gmch_info(), get_number_of_caches(), initial_lapicid(), intel_ht_sibling(), is_sgx_supported(), mchinfo_ddr2(), sgx_fill_ssdt(), smbios_write_type4(), and wait_txt_clear().

Definition at line 132 of file cpu.h.

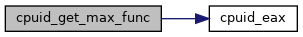

References cpuid_eax().

Referenced by calculate_tsc_freq_from_core_crystal(), get_cpu_core_thread_bits(), get_freq_from_cpuid16h(), get_number_of_caches(), initial_lapicid(), intel_ht_sibling(), smbios_write_type4(), and update_board_layout().

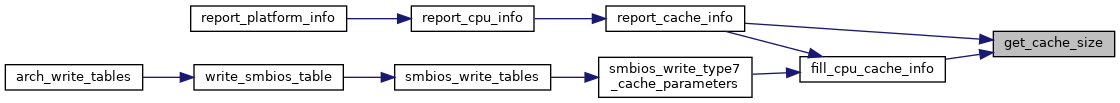

| bool fill_cpu_cache_info | ( | uint8_t | level, |

| struct cpu_cache_info * | info | ||

| ) |

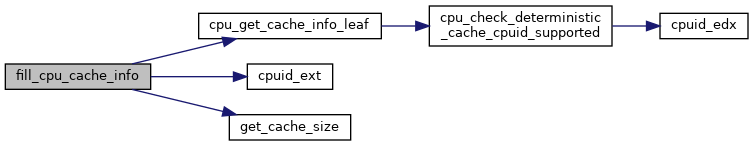

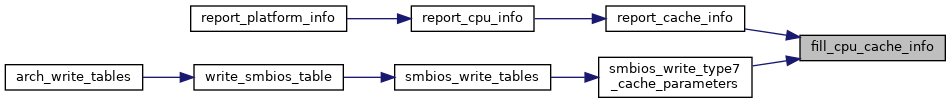

Definition at line 191 of file cpu_common.c.

References cpu_get_cache_info_leaf(), CPUID_CACHE_COHER_LINE, CPUID_CACHE_FULL_ASSOC, CPUID_CACHE_LEVEL, CPUID_CACHE_NO_OF_SETS, CPUID_CACHE_PHYS_LINE, CPUID_CACHE_SHARING_CACHE, CPUID_CACHE_TYPE, CPUID_CACHE_WAYS_OF_ASSOC, cpuid_ext(), get_cache_size(), and info.

Referenced by report_cache_info(), and smbios_write_type7_cache_parameters().

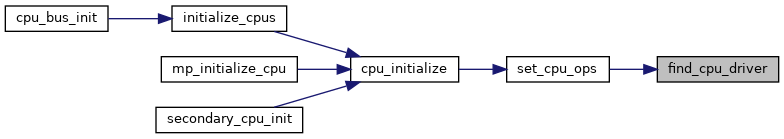

| struct cpu_driver* find_cpu_driver | ( | struct device * | cpu | ) |

Definition at line 190 of file cpu.c.

References _cpu_drivers, _ecpu_drivers, cpu_device_id::device, device::device, cpu_driver::id_table, NULL, cpu_device_id::vendor, device::vendor, X86_VENDOR_ANY, and X86_VENDOR_INVALID.

Referenced by set_cpu_ops().

| size_t get_cache_size | ( | const struct cpu_cache_info * | info | ) |

Definition at line 183 of file cpu_common.c.

References info.

Referenced by fill_cpu_cache_info(), and report_cache_info().

|

inlinestatic |

Definition at line 278 of file cpu.h.

References c.

Referenced by cpu_has_alternative_smrr(), cpu_initialize(), find_cbfs_microcode(), get_cores_per_package(), get_fsb_tsc(), get_processor_model(), pch_setup_cir(), and platform_prog_run().