|

coreboot

coreboot is an Open Source project aimed at replacing the proprietary BIOS found in most computers.

|

|

coreboot

coreboot is an Open Source project aimed at replacing the proprietary BIOS found in most computers.

|

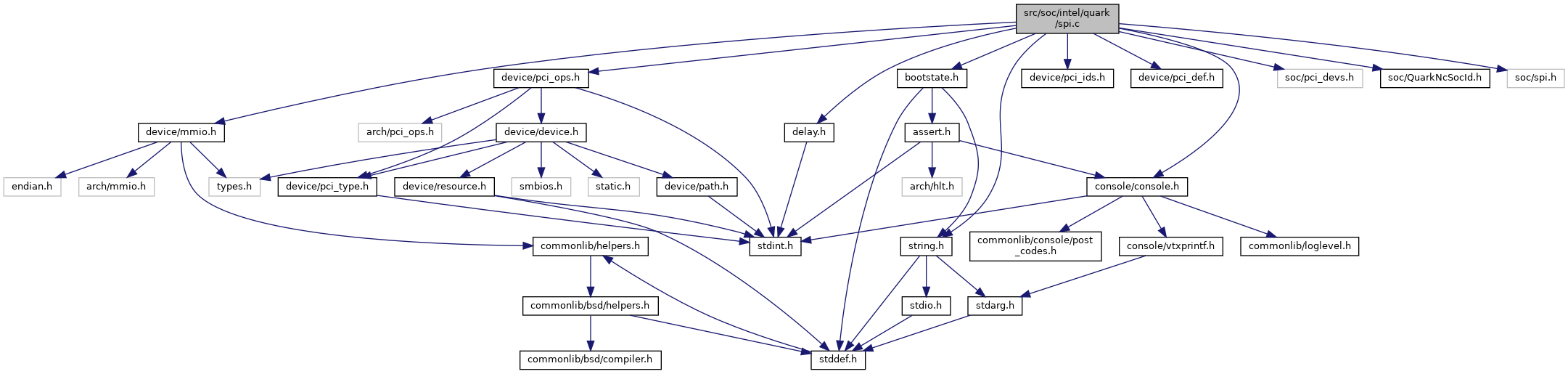

#include <device/mmio.h>#include <device/pci_ops.h>#include <bootstate.h>#include <console/console.h>#include <device/pci_ids.h>#include <device/pci_def.h>#include <delay.h>#include <soc/pci_devs.h>#include <soc/QuarkNcSocId.h>#include <soc/spi.h>#include <string.h>

Go to the source code of this file.

Functions | |

| void | spi_bios_base (uint32_t bios_base_address) |

| void | spi_controller_lock (void) |

| int | spi_protection (uint32_t address, uint32_t length) |

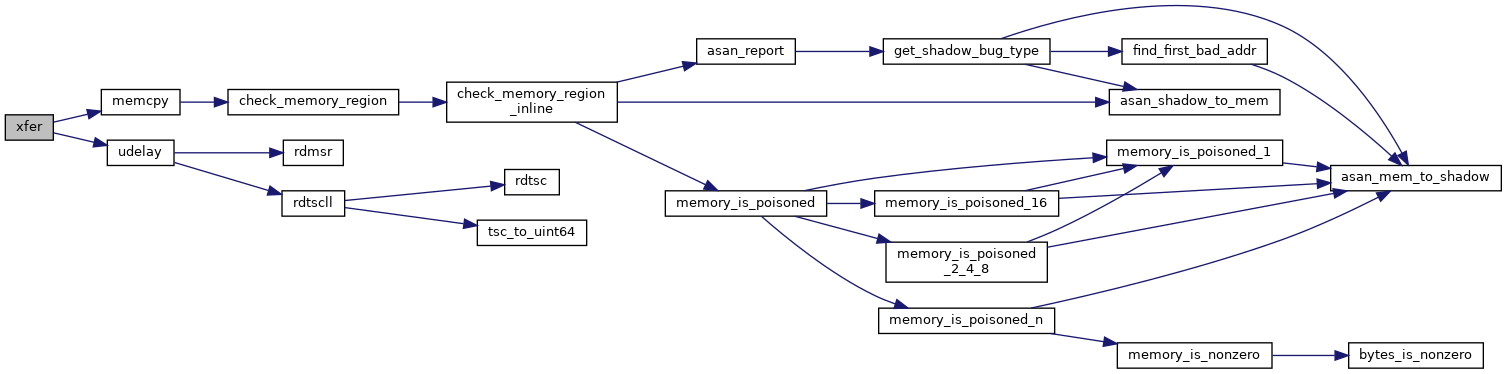

| static int | xfer (const struct spi_slave *slave, const void *dout, size_t bytesout, void *din, size_t bytesin) |

| void | spi_init (void) |

| Init all SPI controllers with default values and enable all SPI controller. More... | |

| static void | spi_init_cb (void *unused) |

| BOOT_STATE_INIT_ENTRY (BS_DEV_INIT, BS_ON_ENTRY, spi_init_cb, NULL) | |

Variables | |

| struct spi_context | spi_driver_context |

| const struct spi_ctrlr | spi_driver |

| const struct spi_ctrlr_buses | spi_ctrlr_bus_map [] |

| const size_t | spi_ctrlr_bus_map_count = ARRAY_SIZE(spi_ctrlr_bus_map) |

| BOOT_STATE_INIT_ENTRY | ( | BS_DEV_INIT | , |

| BS_ON_ENTRY | , | ||

| spi_init_cb | , | ||

| NULL | |||

| ) |

Definition at line 21 of file spi.c.

References address, flash_ctrlr::bbar, spi_context::ctrlr, and spi_driver_context.

Definition at line 31 of file spi.c.

References spi_context::ctrlr, spi_driver_context, SPISTS_CLD, and flash_ctrlr::status.

Init all SPI controllers with default values and enable all SPI controller.

Definition at line 217 of file spi.c.

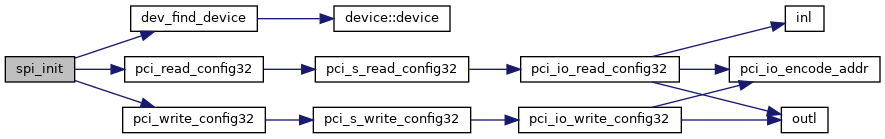

References B_QNC_LPC_BIOS_CNTL_BIOSWE, B_QNC_LPC_RCBA_EN, B_QNC_LPC_RCBA_MASK, BIOS_ERR, spi_context::ctrlr, dev_find_device(), LPC_DEVID, NULL, flash_ctrlr::opmenu, pci_read_config32(), PCI_VID_INTEL, pci_write_config32(), flash_ctrlr::prefix, printk, R_QNC_LPC_BIOS_CNTL, R_QNC_LPC_RCBA, spi_driver_context, SPITYPE_ADDRESS, SPITYPE_PREFIX, and flash_ctrlr::type.

Definition at line 263 of file spi.c.

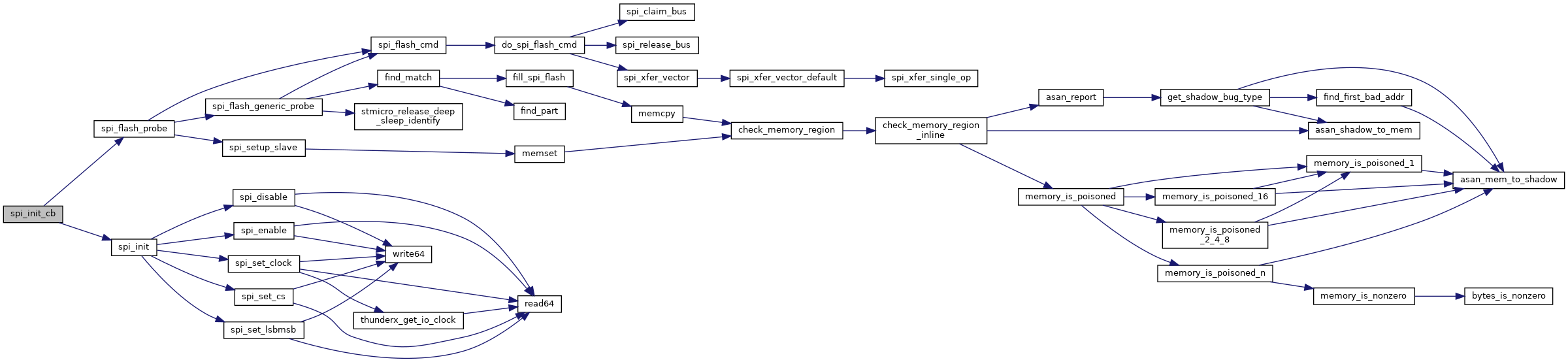

References BIOS_DEBUG, printk, spi_flash_probe(), and spi_init().

Definition at line 39 of file spi.c.

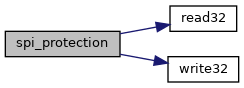

References address, ARRAY_SIZE, base, BIOS_ERR, spi_context::ctrlr, length, flash_ctrlr::pbr, printk, read32(), spi_driver_context, SPIPBR_PRB, SPIPBR_PRB_SHIFT, SPIPBR_PRL, SPIPBR_WPE, value, and write32().

|

static |

Definition at line 76 of file spi.c.

References flash_ctrlr::address, BIOS_ERR, flash_ctrlr::control, spi_context::control, spi_context::ctrlr, flash_ctrlr::data, memcpy(), NULL, flash_ctrlr::opmenu, flash_ctrlr::prefix, spi_context::prefix, printk, spi_driver_context, SPICTL_ACS, SPICTL_AR, SPICTL_CG, SPICTL_COPTR_SHIFT, SPICTL_DBCNT_SHIFT, SPICTL_DC, SPICTL_SOPTR_SHIFT, SPISTS_BA, SPISTS_CD, SPISTS_CIP, SPITYPE_ADDRESS, SPITYPE_PREFIX, flash_ctrlr::status, type, flash_ctrlr::type, and udelay().

| const struct spi_ctrlr_buses spi_ctrlr_bus_map[] |

| const size_t spi_ctrlr_bus_map_count = ARRAY_SIZE(spi_ctrlr_bus_map) |

| const struct spi_ctrlr spi_driver |

| struct spi_context spi_driver_context |

Definition at line 1 of file spi.c.

Referenced by spi_bios_base(), spi_controller_lock(), spi_init(), spi_protection(), and xfer().