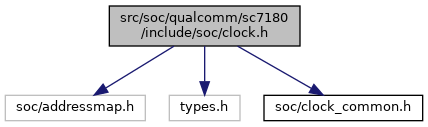

#include <soc/addressmap.h>

#include <types.h>

#include <soc/clock_common.h>

Go to the source code of this file.

|

| enum | apcs_branch_en_vote {

QUPV3_WRAP_0_M_AHB_CLK_ENA = 6

, QUPV3_WRAP_0_S_AHB_CLK_ENA = 7

, QUPV3_WRAP0_CORE_CLK_ENA = 8

, QUPV3_WRAP0_CORE_2X_CLK_ENA = 9

,

QUPV3_WRAP1_CORE_2X_CLK_ENA = 18

, QUPV3_WRAP1_CORE_CLK_ENA = 19

, QUPV3_WRAP_1_M_AHB_CLK_ENA = 20

, QUPV3_WRAP_1_S_AHB_CLK_ENA = 21

,

QUPV3_WRAP_0_M_AHB_CLK_ENA = 6

, QUPV3_WRAP_0_S_AHB_CLK_ENA = 7

, QUPV3_WRAP0_CORE_CLK_ENA = 8

, QUPV3_WRAP0_CORE_2X_CLK_ENA = 9

,

AGGRE_NOC_PCIE_1_AXI_CLK_ENA = 11

, QUPV3_WRAP1_CORE_2X_CLK_ENA = 18

, AGGRE_NOC_PCIE_TBU_CLK_ENA = 18

, QUPV3_WRAP1_CORE_CLK_ENA = 19

,

DDRSS_PCIE_SF_CLK_ENA = 19

, QUPV3_WRAP_1_M_AHB_CLK_ENA = 20

, QUPV3_WRAP_1_S_AHB_CLK_ENA = 21

, PCIE1_PHY_RCHNG_CLK_ENA = 23

,

PCIE_1_SLV_Q2A_AXI_CLK_ENA = 25

, PCIE_1_SLV_AXI_CLK_ENA = 26

, PCIE_1_MSTR_AXI_CLK_ENA = 27

, PCIE_1_CFG_AHB_CLK_ENA = 28

,

AGGRE_NOC_PCIE_CENTER_SF_AXI_CLK_ENA = 28

, PCIE_1_AUX_CLK_ENA = 29

, PCIE_1_PIPE_CLK_ENA = 30

, NO_VOTE_BIT = -1

} |

| |

| enum | clk_pll_src {

SRC_XO_19_2MHZ = 0

, SRC_GPLL0_MAIN_600MHZ = 1

, SRC_GPLL0_EVEN_300MHZ = 6

, SRC_XO_19_2MHZ = 0

,

SRC_GPLL0_MAIN_600MHZ = 1

, SRC_GPLL9_MAIN_808MHZ = 2

, SRC_GCC_DISP_GPLL0_CLK = 4

, SRC_GPLL10_MAIN_384MHZ = 5

,

SRC_GPLL0_EVEN_300MHZ = 6

} |

| |

| enum | mdss_clock {

MDSS_CLK_ESC0 = 0

, MDSS_CLK_PCLK0

, MDSS_CLK_BYTE0

, MDSS_CLK_BYTE0_INTF

,

MDSS_CLK_COUNT

} |

| |

| enum | clk_qup {

QUP_WRAP0_S0

, QUP_WRAP0_S1

, QUP_WRAP0_S2

, QUP_WRAP0_S3

,

QUP_WRAP0_S4

, QUP_WRAP0_S5

, QUP_WRAP1_S0

, QUP_WRAP1_S1

,

QUP_WRAP1_S2

, QUP_WRAP1_S3

, QUP_WRAP1_S4

, QUP_WRAP1_S5

,

QUP_WRAP0_S0

, QUP_WRAP0_S1

, QUP_WRAP0_S2

, QUP_WRAP0_S3

,

QUP_WRAP0_S4

, QUP_WRAP0_S5

, QUP_WRAP0_S6

, QUP_WRAP0_S7

,

QUP_WRAP1_S0

, QUP_WRAP1_S1

, QUP_WRAP1_S2

, QUP_WRAP1_S3

,

QUP_WRAP1_S4

, QUP_WRAP1_S5

, QUP_WRAP1_S6

, QUP_WRAP1_S7

} |

| |

| enum | pll_config_ctl_lo {

CTUNE_SHFT = 2

, K_I_SHFT = 4

, K_P_SHFT = 7

, PFA_MSB_SHFT = 10

,

REF_CONT_SHFT = 28

, CTUNE_SHFT = 2

, K_I_SHFT = 4

, K_P_SHFT = 7

,

PFA_MSB_SHFT = 10

, RES_BIT_SHFT = 14

, RON_DEGEN_MUL_SHFT = 18

, ALPHA_CAL_SHFT = 20

,

DCO_ADDER_EN_SHFT = 22

, PLL_COUNTER_EN = 27

} |

| |

| enum | pll_config_ctl_hi {

CUR_ADJ_SHFT = 0

, DMET_SHFT = 4

, RES_SHFT = 6

, CUR_TRIM_SHFT = 0

,

FREQ_DOUBLE_SHFT = 4

, ADJ_ENABLE_SHFT = 5

, ADJ_VALUE_SHFT = 6

, KLSB_SHFT = 13

,

RON_MODE_SHFT = 17

, CHP_REF_SHFT = 19

, CHP_STARTUP = 21

, ADC_KMSB_VAL = 23

} |

| |

| enum | apss_gfmux { GFMUX_SRC_SEL_BMSK = 0x3

, APCS_SRC_EARLY = 0x2

, GFMUX_SRC_SEL_BMSK = 0x3

, APCS_SRC_EARLY = 0x2

} |

| |

|

| | check_member (sc7180_gcc, usb30_prim_bcr, 0xf000) |

| |

| | check_member (sc7180_gcc, qup_wrap0_bcr, 0x17000) |

| |

| | check_member (sc7180_gcc, qup_wrap1_bcr, 0x18000) |

| |

| | check_member (sc7180_gcc, qup_wrap1_core_cdivr, 0x18994) |

| |

| | check_member (sc7180_gcc, qusb2phy_prim_bcr, 0x26000) |

| |

| | check_member (sc7180_gcc, usb3phy_phy_prim_bcr, 0x50004) |

| |

| | check_member (sc7180_gcc, usb3_phy_prim_bcr, 0x50000) |

| |

| | check_member (sc7180_gcc, apcs_clk_br_en1, 0x52008) |

| |

| | check_member (sc7180_disp_cc, byte0_cbcr, 0x2028) |

| |

| | check_member (sc7180_disp_cc, esc0_cbcr, 0x2038) |

| |

| void | clock_init (void) |

| |

| void | clock_configure_qspi (uint32_t hz) |

| |

| void | clock_configure_qup (int qup, uint32_t hz) |

| |

| void | clock_enable_qup (int qup) |

| |

| void | clock_configure_dfsr (int qup) |

| |

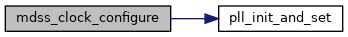

| int | mdss_clock_configure (enum mdss_clock clk_type, uint32_t source, uint32_t divider, uint32_t m, uint32_t n, uint32_t d) |

| |

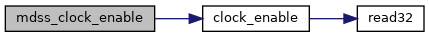

| int | mdss_clock_enable (enum mdss_clock clk_type) |

| |

◆ AOP_RESET_SHFT

◆ clock_reset_aop

◆ GPLL0_EVEN_HZ

| #define GPLL0_EVEN_HZ (300 * MHz) |

◆ GPLL0_MAIN_HZ

| #define GPLL0_MAIN_HZ (600 * MHz) |

◆ L_VAL_1209P6MHz

| #define L_VAL_1209P6MHz 0x3F |

◆ L_VAL_1516P8MHz

| #define L_VAL_1516P8MHz 0x4F |

◆ QUPV3_WRAP0_CLK_ENA_S

| #define QUPV3_WRAP0_CLK_ENA_S |

( |

|

idx | ) |

(10 + idx) |

◆ QUPV3_WRAP1_CLK_ENA_S

| #define QUPV3_WRAP1_CLK_ENA_S |

( |

|

idx | ) |

(22 + idx) |

◆ SCALE_FREQ_SHFT

| #define SCALE_FREQ_SHFT 11 |

◆ SRC_XO_HZ

| #define SRC_XO_HZ (19200 * KHz) |

◆ apcs_branch_en_vote

| Enumerator |

|---|

| QUPV3_WRAP_0_M_AHB_CLK_ENA | |

| QUPV3_WRAP_0_S_AHB_CLK_ENA | |

| QUPV3_WRAP0_CORE_CLK_ENA | |

| QUPV3_WRAP0_CORE_2X_CLK_ENA | |

| QUPV3_WRAP1_CORE_2X_CLK_ENA | |

| QUPV3_WRAP1_CORE_CLK_ENA | |

| QUPV3_WRAP_1_M_AHB_CLK_ENA | |

| QUPV3_WRAP_1_S_AHB_CLK_ENA | |

| QUPV3_WRAP_0_M_AHB_CLK_ENA | |

| QUPV3_WRAP_0_S_AHB_CLK_ENA | |

| QUPV3_WRAP0_CORE_CLK_ENA | |

| QUPV3_WRAP0_CORE_2X_CLK_ENA | |

| AGGRE_NOC_PCIE_1_AXI_CLK_ENA | |

| QUPV3_WRAP1_CORE_2X_CLK_ENA | |

| AGGRE_NOC_PCIE_TBU_CLK_ENA | |

| QUPV3_WRAP1_CORE_CLK_ENA | |

| DDRSS_PCIE_SF_CLK_ENA | |

| QUPV3_WRAP_1_M_AHB_CLK_ENA | |

| QUPV3_WRAP_1_S_AHB_CLK_ENA | |

| PCIE1_PHY_RCHNG_CLK_ENA | |

| PCIE_1_SLV_Q2A_AXI_CLK_ENA | |

| PCIE_1_SLV_AXI_CLK_ENA | |

| PCIE_1_MSTR_AXI_CLK_ENA | |

| PCIE_1_CFG_AHB_CLK_ENA | |

| AGGRE_NOC_PCIE_CENTER_SF_AXI_CLK_ENA | |

| PCIE_1_AUX_CLK_ENA | |

| PCIE_1_PIPE_CLK_ENA | |

| NO_VOTE_BIT | |

Definition at line 17 of file clock.h.

◆ apss_gfmux

| Enumerator |

|---|

| GFMUX_SRC_SEL_BMSK | |

| APCS_SRC_EARLY | |

| GFMUX_SRC_SEL_BMSK | |

| APCS_SRC_EARLY | |

Definition at line 182 of file clock.h.

◆ clk_pll_src

| Enumerator |

|---|

| SRC_XO_19_2MHZ | |

| SRC_GPLL0_MAIN_600MHZ | |

| SRC_GPLL0_EVEN_300MHZ | |

| SRC_XO_19_2MHZ | |

| SRC_GPLL0_MAIN_600MHZ | |

| SRC_GPLL9_MAIN_808MHZ | |

| SRC_GCC_DISP_GPLL0_CLK | |

| SRC_GPLL10_MAIN_384MHZ | |

| SRC_GPLL0_EVEN_300MHZ | |

Definition at line 28 of file clock.h.

◆ clk_qup

| Enumerator |

|---|

| QUP_WRAP0_S0 | |

| QUP_WRAP0_S1 | |

| QUP_WRAP0_S2 | |

| QUP_WRAP0_S3 | |

| QUP_WRAP0_S4 | |

| QUP_WRAP0_S5 | |

| QUP_WRAP1_S0 | |

| QUP_WRAP1_S1 | |

| QUP_WRAP1_S2 | |

| QUP_WRAP1_S3 | |

| QUP_WRAP1_S4 | |

| QUP_WRAP1_S5 | |

| QUP_WRAP0_S0 | |

| QUP_WRAP0_S1 | |

| QUP_WRAP0_S2 | |

| QUP_WRAP0_S3 | |

| QUP_WRAP0_S4 | |

| QUP_WRAP0_S5 | |

| QUP_WRAP0_S6 | |

| QUP_WRAP0_S7 | |

| QUP_WRAP1_S0 | |

| QUP_WRAP1_S1 | |

| QUP_WRAP1_S2 | |

| QUP_WRAP1_S3 | |

| QUP_WRAP1_S4 | |

| QUP_WRAP1_S5 | |

| QUP_WRAP1_S6 | |

| QUP_WRAP1_S7 | |

Definition at line 131 of file clock.h.

◆ mdss_clock

| Enumerator |

|---|

| MDSS_CLK_ESC0 | |

| MDSS_CLK_PCLK0 | |

| MDSS_CLK_BYTE0 | |

| MDSS_CLK_BYTE0_INTF | |

| MDSS_CLK_COUNT | |

Definition at line 123 of file clock.h.

◆ pll_config_ctl_hi

| Enumerator |

|---|

| CUR_ADJ_SHFT | |

| DMET_SHFT | |

| RES_SHFT | |

| CUR_TRIM_SHFT | |

| FREQ_DOUBLE_SHFT | |

| ADJ_ENABLE_SHFT | |

| ADJ_VALUE_SHFT | |

| KLSB_SHFT | |

| RON_MODE_SHFT | |

| CHP_REF_SHFT | |

| CHP_STARTUP | |

| ADC_KMSB_VAL | |

Definition at line 176 of file clock.h.

◆ pll_config_ctl_lo

| Enumerator |

|---|

| CTUNE_SHFT | |

| K_I_SHFT | |

| K_P_SHFT | |

| PFA_MSB_SHFT | |

| REF_CONT_SHFT | |

| CTUNE_SHFT | |

| K_I_SHFT | |

| K_P_SHFT | |

| PFA_MSB_SHFT | |

| RES_BIT_SHFT | |

| RON_DEGEN_MUL_SHFT | |

| ALPHA_CAL_SHFT | |

| DCO_ADDER_EN_SHFT | |

| PLL_COUNTER_EN | |

Definition at line 168 of file clock.h.

◆ check_member() [1/10]

◆ check_member() [2/10]

◆ check_member() [3/10]

| check_member |

( |

sc7180_gcc |

, |

|

|

apcs_clk_br_en1 |

, |

|

|

0x52008 |

|

|

) |

| |

◆ check_member() [4/10]

| check_member |

( |

sc7180_gcc |

, |

|

|

qup_wrap0_bcr |

, |

|

|

0x17000 |

|

|

) |

| |

◆ check_member() [5/10]

| check_member |

( |

sc7180_gcc |

, |

|

|

qup_wrap1_bcr |

, |

|

|

0x18000 |

|

|

) |

| |

◆ check_member() [6/10]

| check_member |

( |

sc7180_gcc |

, |

|

|

qup_wrap1_core_cdivr |

, |

|

|

0x18994 |

|

|

) |

| |

◆ check_member() [7/10]

| check_member |

( |

sc7180_gcc |

, |

|

|

qusb2phy_prim_bcr |

, |

|

|

0x26000 |

|

|

) |

| |

◆ check_member() [8/10]

| check_member |

( |

sc7180_gcc |

, |

|

|

usb30_prim_bcr |

, |

|

|

0xf000 |

|

|

) |

| |

◆ check_member() [9/10]

| check_member |

( |

sc7180_gcc |

, |

|

|

usb3_phy_prim_bcr |

, |

|

|

0x50000 |

|

|

) |

| |

◆ check_member() [10/10]

| check_member |

( |

sc7180_gcc |

, |

|

|

usb3phy_phy_prim_bcr |

, |

|

|

0x50004 |

|

|

) |

| |

◆ clock_configure_dfsr()

| void clock_configure_dfsr |

( |

int |

qup | ) |

|

◆ clock_configure_qspi()

◆ clock_configure_qup()

◆ clock_enable_qup()

| void clock_enable_qup |

( |

int |

qup | ) |

|

◆ clock_init()

◆ mdss_clock_configure()

◆ mdss_clock_enable()

◆ aoss

◆ apss_l3

◆ apss_silver

◆ gcc

◆ mdss