|

coreboot

coreboot is an Open Source project aimed at replacing the proprietary BIOS found in most computers.

|

|

coreboot

coreboot is an Open Source project aimed at replacing the proprietary BIOS found in most computers.

|

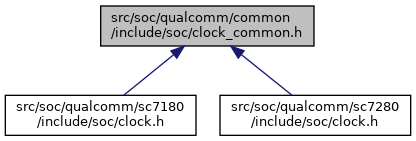

Go to the source code of this file.

Data Structures | |

| struct | clock_rcg |

| struct | clock_rcg_mnd |

| struct | clock_rcg_dfsr |

| struct | clock_freq_config |

| struct | qupv3_clock |

| struct | alpha_pll_reg_val_config |

| struct | aoss |

| struct | shrm |

Macros | |

| #define | QCOM_CLOCK_DIV(div) (2 * div - 1) |

| #define | GDSC_ENABLE_BIT 0 |

Functions | |

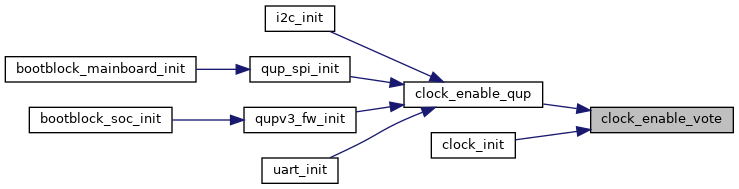

| enum cb_err | clock_enable_vote (void *cbcr_addr, void *vote_addr, uint32_t vote_bit) |

| enum cb_err | clock_enable (void *cbcr_addr) |

| enum cb_err | enable_and_poll_gdsc_status (void *gdscr_addr) |

| void | clock_reset_bcr (void *bcr_addr, bool assert) |

| enum cb_err | clock_configure (struct clock_rcg *clk, struct clock_freq_config *clk_cfg, uint32_t hz, uint32_t num_perfs) |

| void | clock_configure_dfsr_table (int qup, struct clock_freq_config *clk_cfg, uint32_t num_perfs) |

| enum cb_err | clock_configure_enable_gpll (struct alpha_pll_reg_val_config *cfg, bool enable, int br_enable) |

| enum cb_err | agera_pll_enable (struct alpha_pll_reg_val_config *cfg) |

| enum cb_err | zonda_pll_enable (struct alpha_pll_reg_val_config *cfg) |

| check_member (aoss, aoss_cc_reset_status, 0x50020) | |

| check_member (aoss, aoss_cc_apcs_misc, 0x5002c) | |

| void | clock_reset_subsystem (u32 *misc, u32 shft) |

| #define GDSC_ENABLE_BIT 0 |

Definition at line 137 of file clock_common.h.

| #define QCOM_CLOCK_DIV | ( | div | ) | (2 * div - 1) |

Definition at line 6 of file clock_common.h.

| enum clk_ctl_bcr |

| Enumerator | |

|---|---|

| CLK_CTL_BCR_BLK_SHFT | |

| CLK_CTL_BCR_BLK_BMSK | |

| CLK_CTL_BCR_BLK_ARES_BMSK | |

| CLK_CTL_BCR_BLK_ARES_SHFT | |

Definition at line 126 of file clock_common.h.

| enum clk_ctl_cbcr |

| Enumerator | |

|---|---|

| CLK_CTL_EN_SHFT | |

| CLK_CTL_OFF_SHFT | |

| CLK_CTL_EN_BMSK | |

| CLK_CTL_OFF_BMSK | |

| CLK_CTL_CBC_CLK_OFF_BMSK | |

| CLK_CTL_CBC_CLK_OFF_SHFT | |

| CLK_CTL_CBC_CLK_EN_BMSK | |

| CLK_CTL_CBC_CLK_EN_SHFT | |

Definition at line 113 of file clock_common.h.

| enum clk_ctl_cfg_rcgr |

Definition at line 103 of file clock_common.h.

| enum clk_ctl_cmd_rcgr |

| Enumerator | |

|---|---|

| CLK_CTL_CMD_UPDATE_SHFT | |

| CLK_CTL_CMD_ROOT_OFF_BMSK | |

| CLK_CTL_CMD_ROOT_OFF_SHFT | |

| CLK_CTL_CMD_ROOT_EN_BMSK | |

| CLK_CTL_CMD_ROOT_EN_SHFT | |

| CLK_CTL_CMD_UPDATE_BMSK | |

| CLK_CTL_CMD_UPDATE_SHFT | |

Definition at line 109 of file clock_common.h.

| enum clk_ctl_dfsr |

| Enumerator | |

|---|---|

| CLK_CTL_CMD_DFSR_SHFT | |

| CLK_CTL_CMD_RCG_SW_CTL_SHFT | |

| CLK_CTL_CMD_DFSR_BMSK | |

Definition at line 131 of file clock_common.h.

Definition at line 79 of file clock_common.h.

| enum clk_ctl_rcg_mnd |

| Enumerator | |

|---|---|

| RCG_MODE_DUAL_EDGE | |

| CLK_CTL_RCG_MND_SHFT | |

| CLK_CTL_RCG_MND_BMSK | |

| CLK_CTL_RCG_MND_BMSK | |

| CLK_CTL_RCG_MND_SHFT | |

Definition at line 120 of file clock_common.h.

| enum gpll_mode |

Definition at line 88 of file clock_common.h.

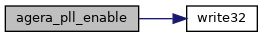

| enum cb_err agera_pll_enable | ( | struct alpha_pll_reg_val_config * | cfg | ) |

Definition at line 124 of file clock.c.

References BIT, CLK_CTL_CFG_MODE_SHFT, CLK_CTL_CFG_SRC_DIV_SHFT, CLK_CTL_CFG_SRC_SEL_SHFT, CLK_CTL_CMD_DFSR_SHFT, CLK_CTL_CMD_RCG_SW_CTL_SHFT, CLK_CTL_RCG_MND_BMSK, clrsetbits32, clock_rcg_dfsr::cmd_dfsr, clock_freq_config::d_2, qupv3_clock::dfsr_clk, gcc, m, clock_freq_config::m, clock_freq_config::n, clock_rcg_dfsr::perf_d_dfsr, clock_rcg_dfsr::perf_dfsr, clock_rcg_dfsr::perf_m_dfsr, clock_rcg_dfsr::perf_n_dfsr, QUP_WRAP1_S0, RCG_MODE_DUAL_EDGE, s, setbits32, clock_freq_config::src, and write32().

| check_member | ( | aoss | , |

| aoss_cc_apcs_misc | , | ||

| 0x5002c | |||

| ) |

| check_member | ( | aoss | , |

| aoss_cc_reset_status | , | ||

| 0x50020 | |||

| ) |

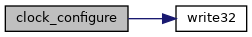

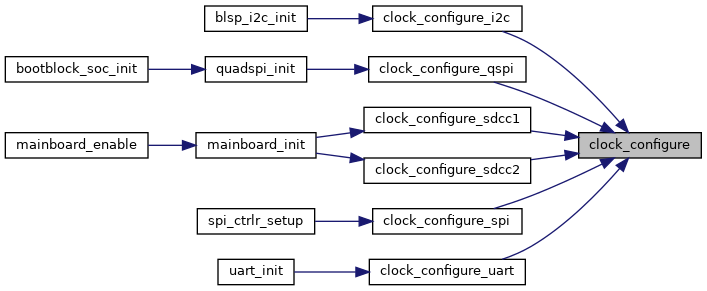

| enum cb_err clock_configure | ( | struct clock_rcg * | clk, |

| struct clock_freq_config * | clk_cfg, | ||

| uint32_t | hz, | ||

| uint32_t | num_perfs | ||

| ) |

Definition at line 78 of file clock.c.

References CLK_CTL_CFG_MODE_SHFT, CLK_CTL_RCG_MND_BMSK, clock_rcg_mnd::d_2, m, clock_rcg_mnd::m, clock_rcg_mnd::n, clock_rcg::rcg_cfg, RCG_MODE_DUAL_EDGE, setbits32, and write32().

Referenced by clock_configure_i2c(), clock_configure_qspi(), clock_configure_sdcc1(), clock_configure_sdcc2(), clock_configure_spi(), and clock_configure_uart().

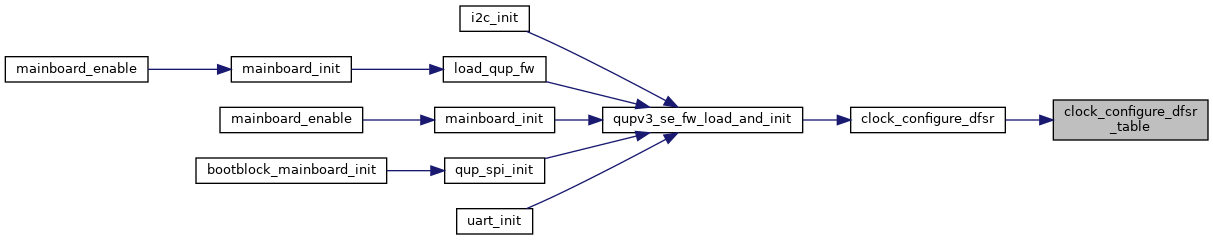

| void clock_configure_dfsr_table | ( | int | qup, |

| struct clock_freq_config * | clk_cfg, | ||

| uint32_t | num_perfs | ||

| ) |

Definition at line 124 of file clock.c.

Referenced by clock_configure_dfsr().

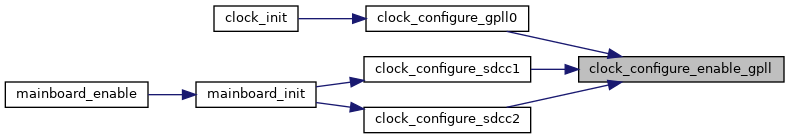

| enum cb_err clock_configure_enable_gpll | ( | struct alpha_pll_reg_val_config * | cfg, |

| bool | enable, | ||

| int | br_enable | ||

| ) |

Definition at line 124 of file clock.c.

Referenced by clock_configure_gpll0(), clock_configure_sdcc1(), and clock_configure_sdcc2().

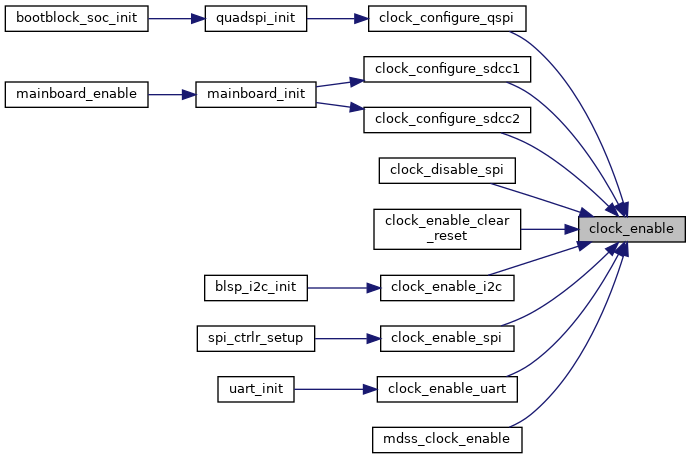

Definition at line 12 of file clock.c.

References CLK_CTL_OFF_BMSK, and read32().

Referenced by clock_configure_qspi(), clock_configure_sdcc1(), clock_configure_sdcc2(), clock_disable_spi(), clock_enable_clear_reset(), clock_enable_i2c(), clock_enable_spi(), clock_enable_uart(), and mdss_clock_enable().

Definition at line 12 of file clock.c.

Referenced by clock_enable_qup(), and clock_init().

| enum cb_err zonda_pll_enable | ( | struct alpha_pll_reg_val_config * | cfg | ) |