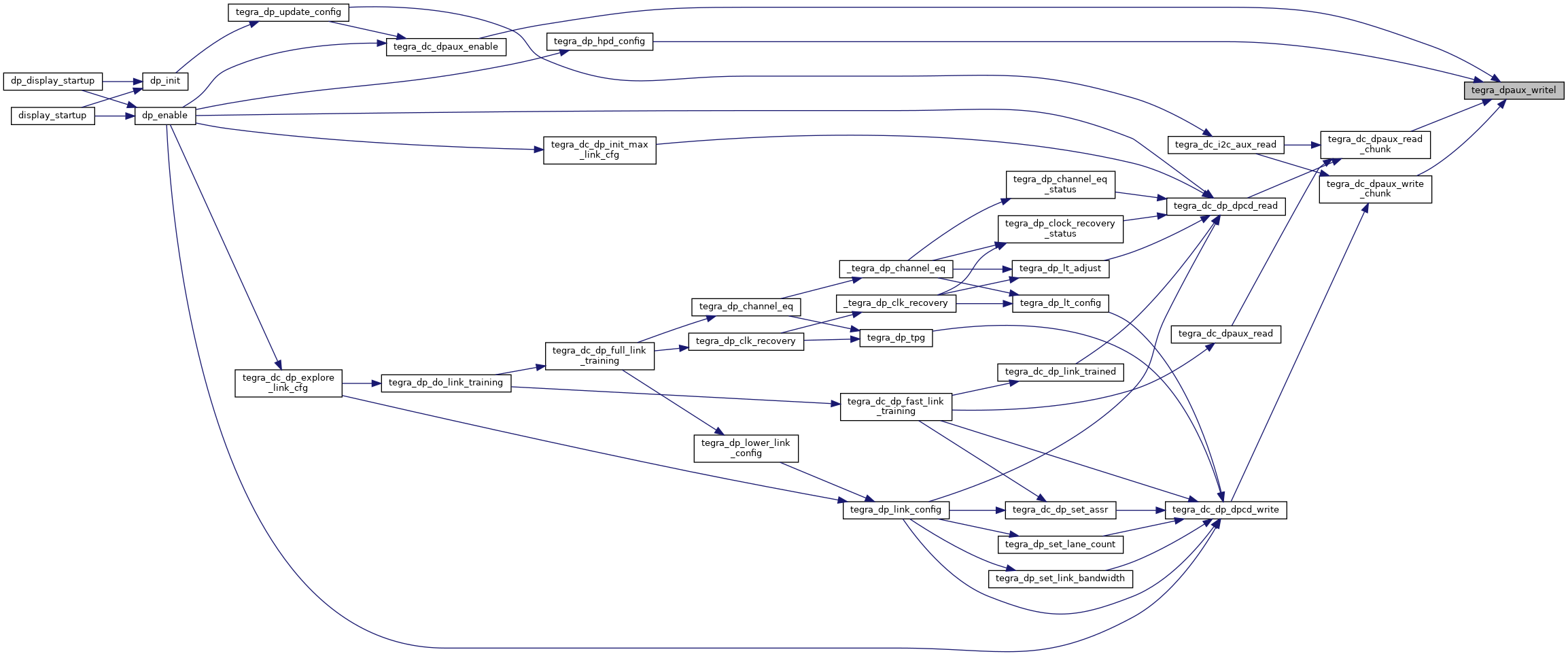

|

coreboot

coreboot is an Open Source project aimed at replacing the proprietary BIOS found in most computers.

|

|

coreboot

coreboot is an Open Source project aimed at replacing the proprietary BIOS found in most computers.

|

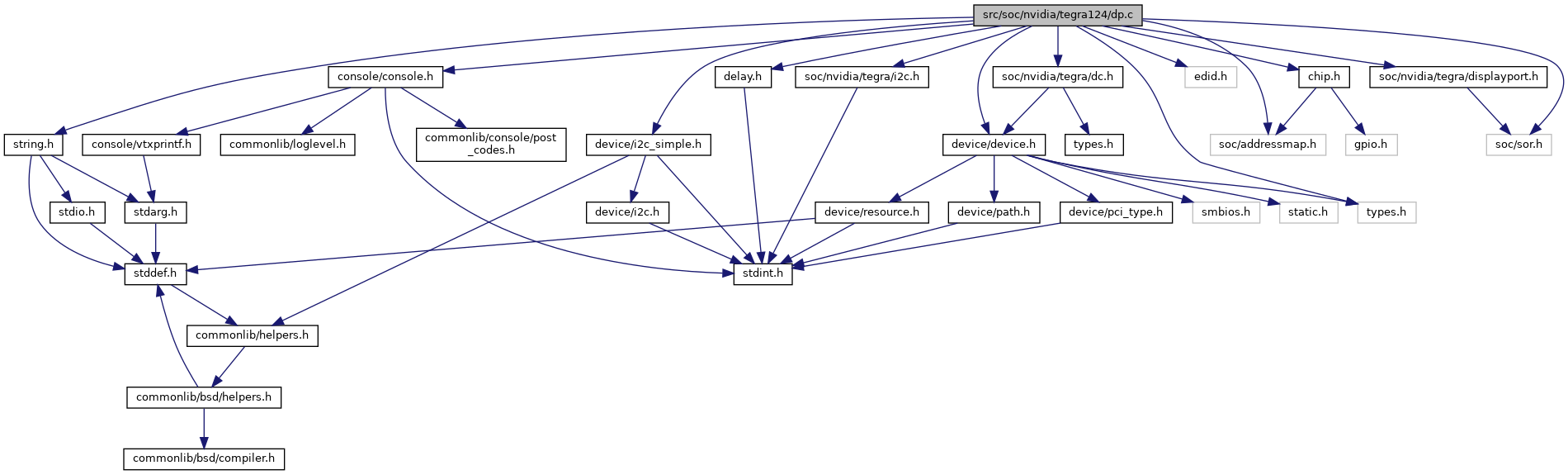

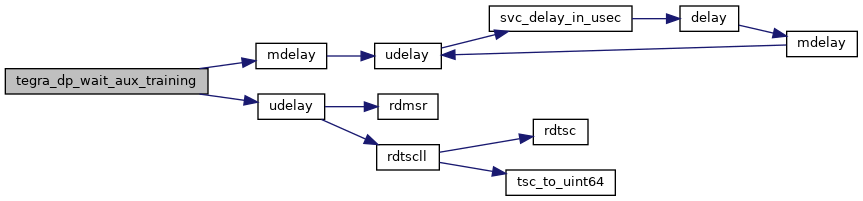

#include <console/console.h>#include <delay.h>#include <device/device.h>#include <device/i2c_simple.h>#include <edid.h>#include <soc/addressmap.h>#include <soc/nvidia/tegra/i2c.h>#include <soc/nvidia/tegra/dc.h>#include <soc/nvidia/tegra/displayport.h>#include <soc/sor.h>#include <string.h>#include <types.h>#include "chip.h"

Go to the source code of this file.

Enumerations | |

| enum | { DP_LT_SUCCESS = 0 , DP_LT_FAILED = -1 } |

Variables | |

| struct tegra_dc_dp_data | dp_data |

|

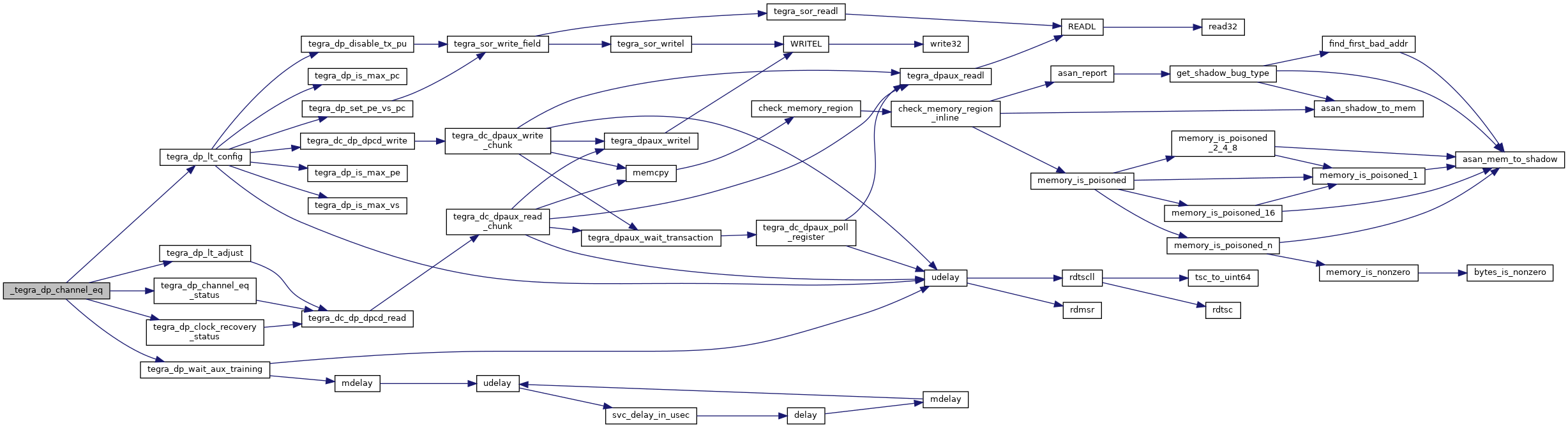

static |

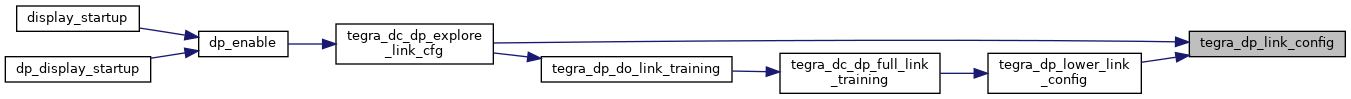

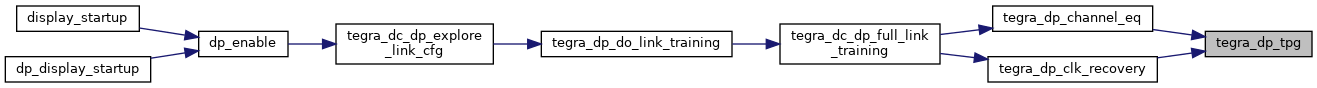

Definition at line 1020 of file dp.c.

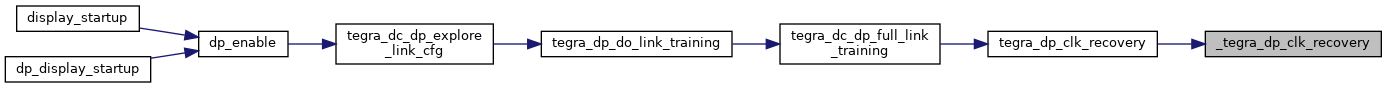

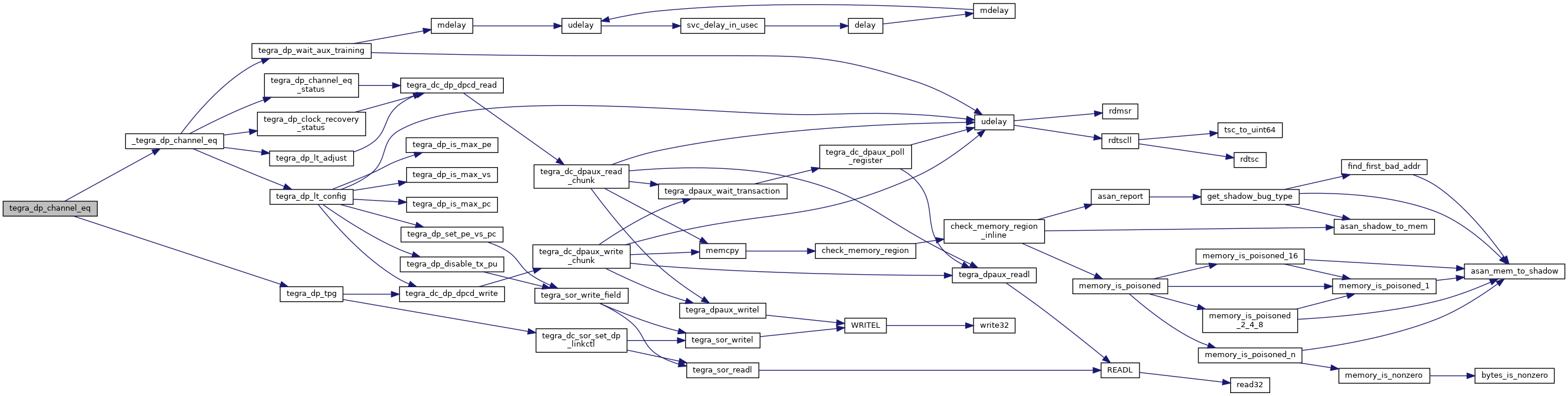

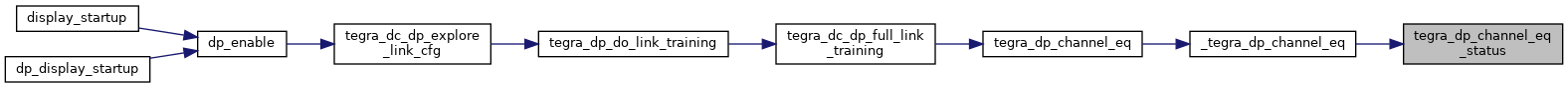

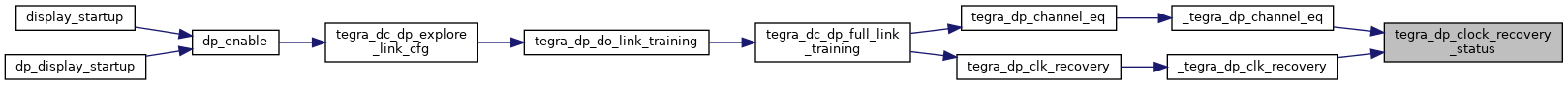

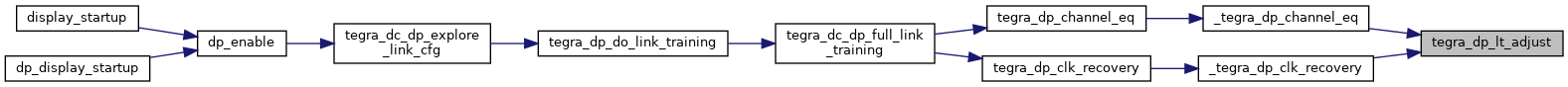

References BIOS_ERR, DP_LT_FAILED, DP_LT_SUCCESS, printk, tegra_dp_channel_eq_status(), tegra_dp_clock_recovery_status(), tegra_dp_lt_adjust(), tegra_dp_lt_config(), and tegra_dp_wait_aux_training().

Referenced by tegra_dp_channel_eq().

|

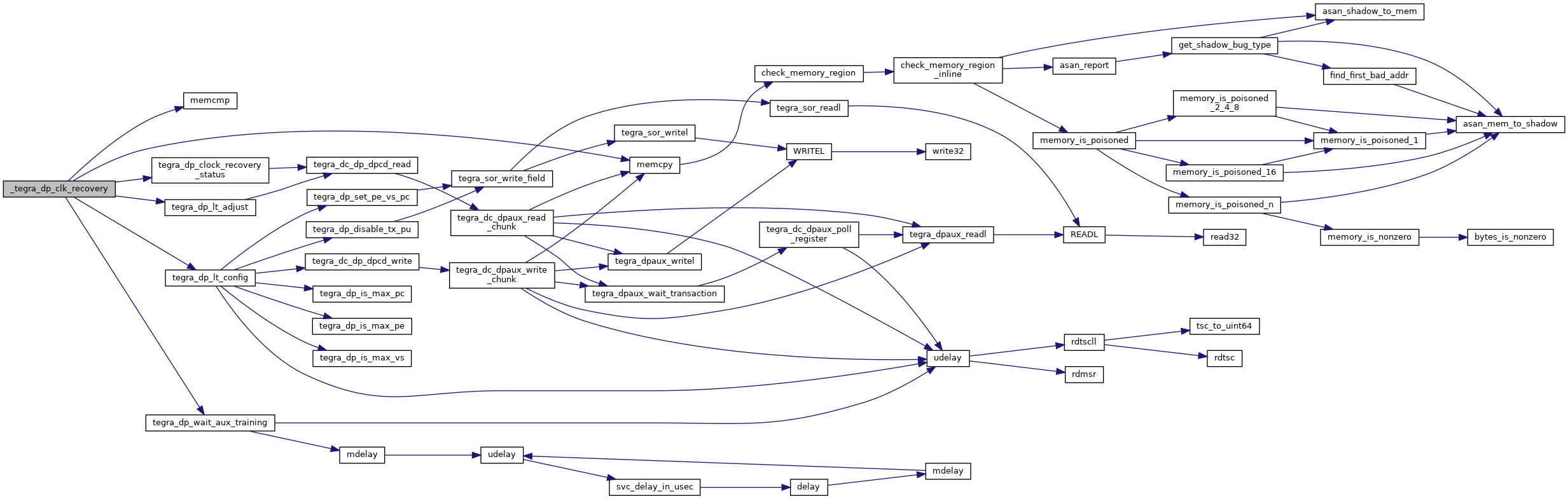

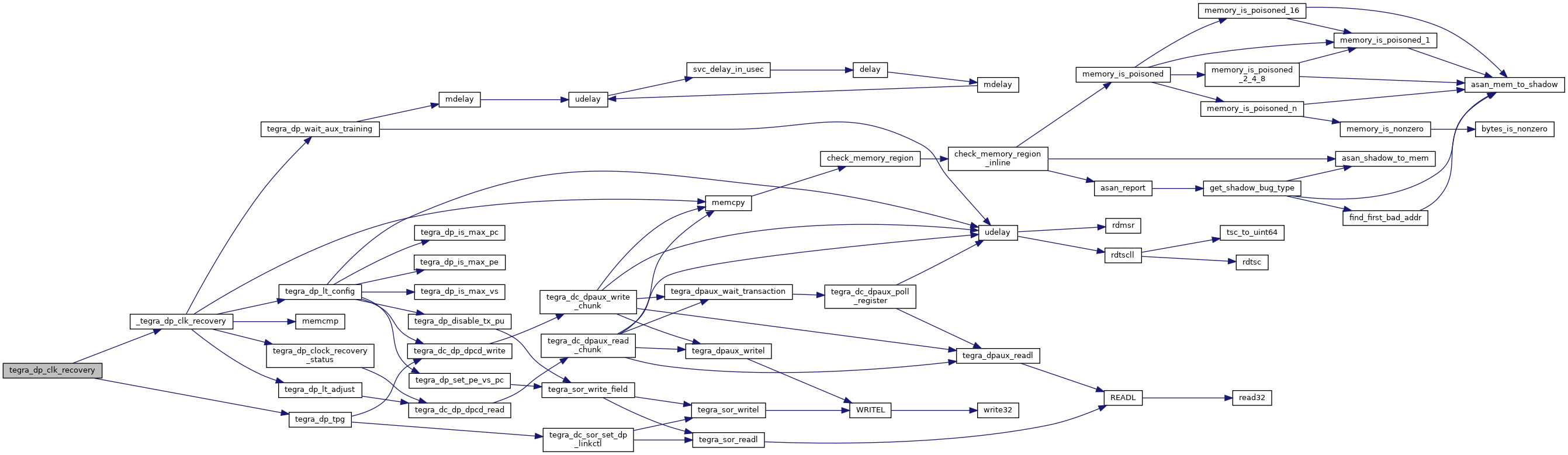

static |

Definition at line 1066 of file dp.c.

References DP_LT_FAILED, DP_LT_SUCCESS, memcmp(), memcpy(), tegra_dp_clock_recovery_status(), tegra_dp_lt_adjust(), tegra_dp_lt_config(), and tegra_dp_wait_aux_training().

Referenced by tegra_dp_clk_recovery().

|

static |

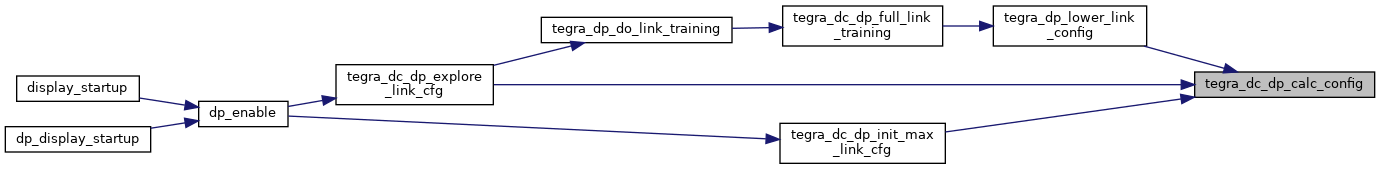

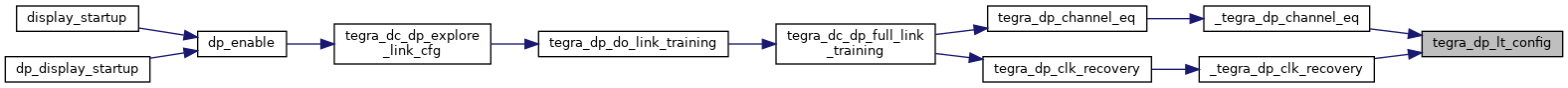

Definition at line 440 of file dp.c.

References BIOS_ERR, DP_LT_FAILED, DP_LT_SUCCESS, tegra_dc_dp_link_config::lane_count, tegra_dc_dp_link_config::link_bw, tegra_dc_dp_link_config::max_lane_count, tegra_dc_dp_link_config::max_link_bw, printk, SOR_LINK_SPEED_G1_62, SOR_LINK_SPEED_G2_7, and SOR_LINK_SPEED_G5_4.

Referenced by tegra_dp_lower_link_config().

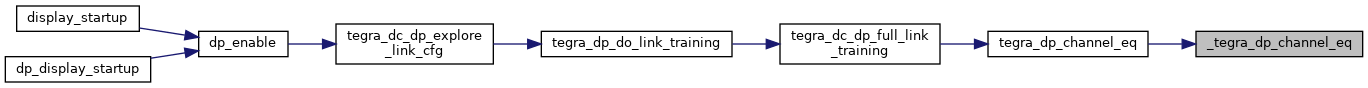

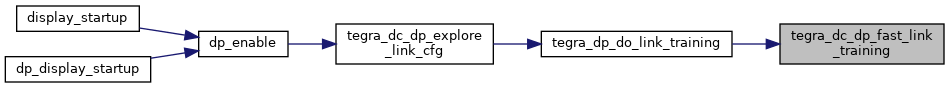

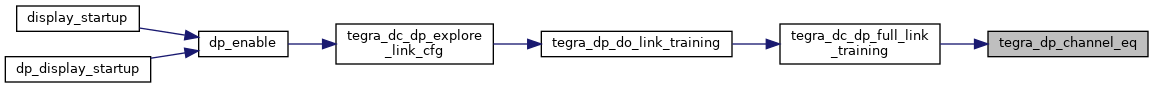

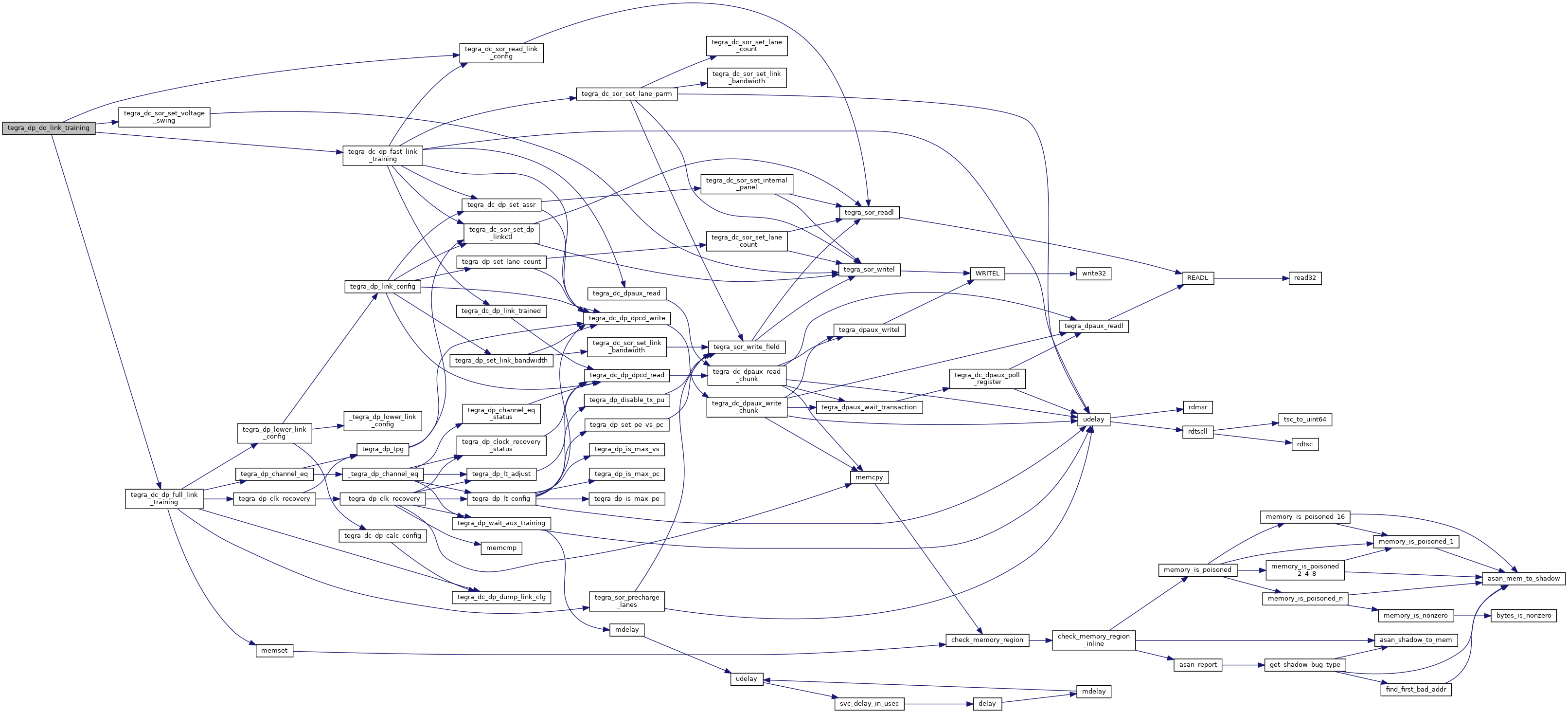

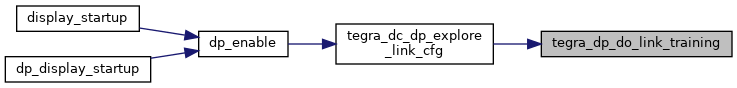

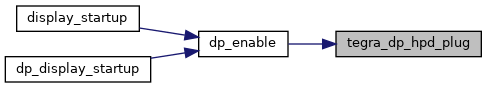

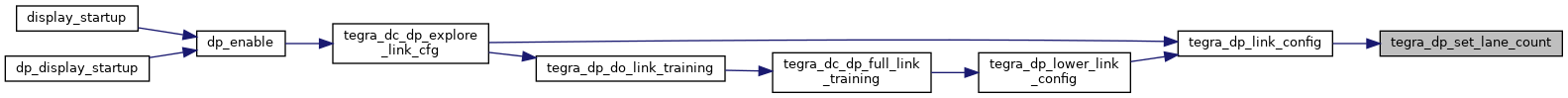

Definition at line 1394 of file dp.c.

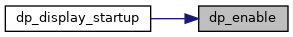

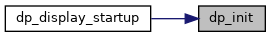

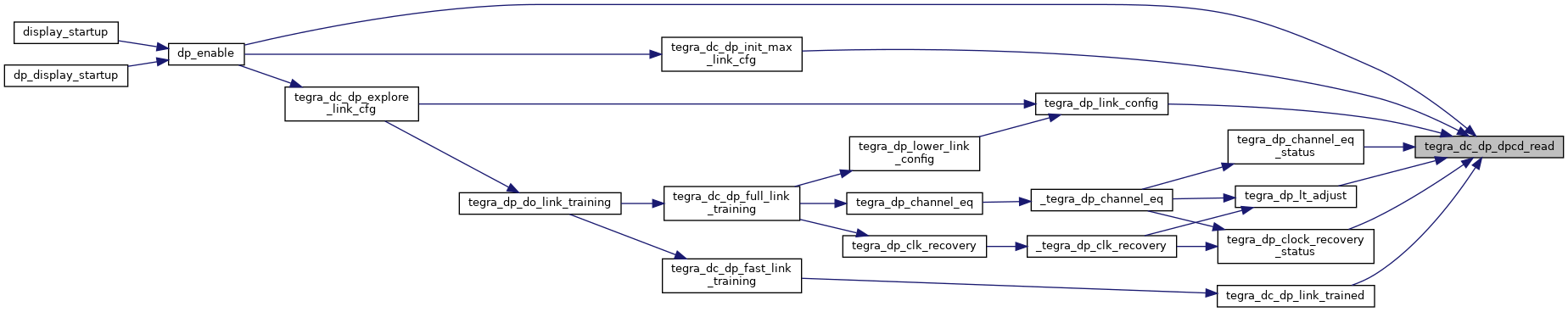

Referenced by dp_display_startup().

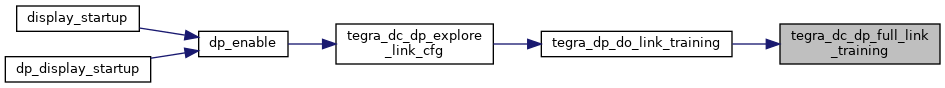

Definition at line 1344 of file dp.c.

Referenced by dp_display_startup().

|

static |

Definition at line 470 of file dp.c.

References tegra_dc_dp_link_config::active_count, tegra_dc_dp_link_config::active_frac, tegra_dc_dp_link_config::activepolarity, BIOS_INFO, tegra_dc_dp_link_config::bits_per_pixel, config, tegra_dc_dp_link_config::enhanced_framing, tegra_dc_dp_link_config::hblank_sym, tegra_dc_dp_link_config::is_valid, tegra_dc_dp_link_config::lane_count, tegra_dc_dp_link_config::link_bw, tegra_dc_dp_data::link_cfg, printk, tegra_dc_dp_dump_link_cfg(), tegra_dc_dp_link_config::tu_size, tegra_dc_dp_link_config::vblank_sym, and tegra_dc_dp_link_config::watermark.

Referenced by tegra_dc_dp_explore_link_cfg(), tegra_dc_dp_init_max_link_cfg(), and tegra_dp_lower_link_config().

|

static |

Definition at line 316 of file dp.c.

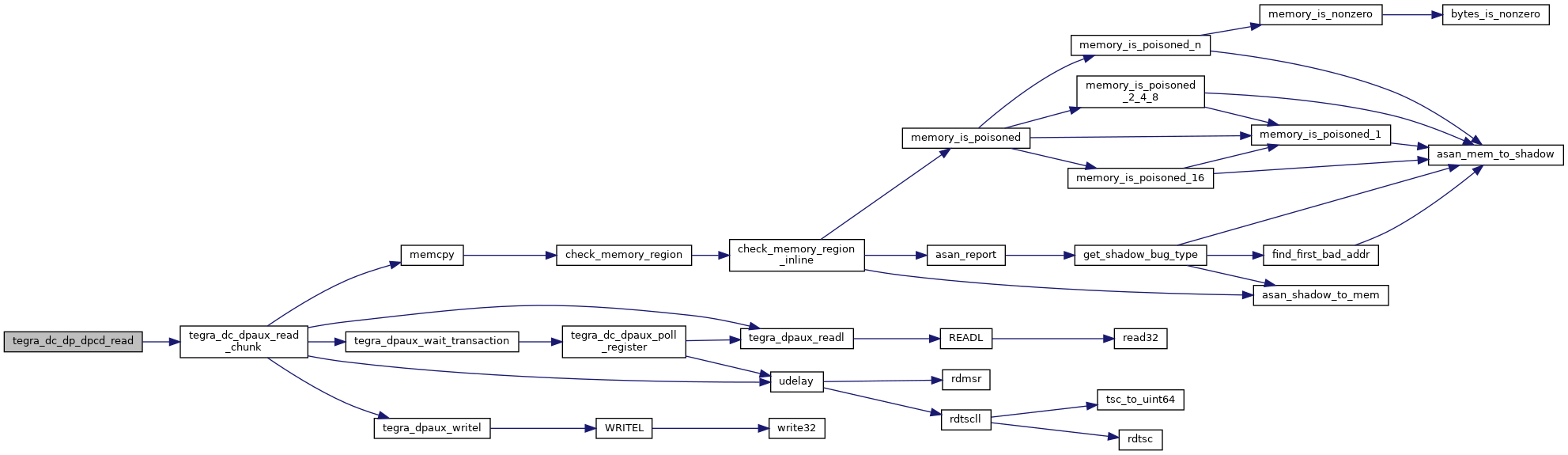

References BIOS_ERR, DPAUX_DP_AUXCTL_CMD_AUXRD, printk, and tegra_dc_dpaux_read_chunk().

Referenced by dp_enable(), tegra_dc_dp_init_max_link_cfg(), tegra_dc_dp_link_trained(), tegra_dp_channel_eq_status(), tegra_dp_clock_recovery_status(), tegra_dp_link_config(), and tegra_dp_lt_adjust().

|

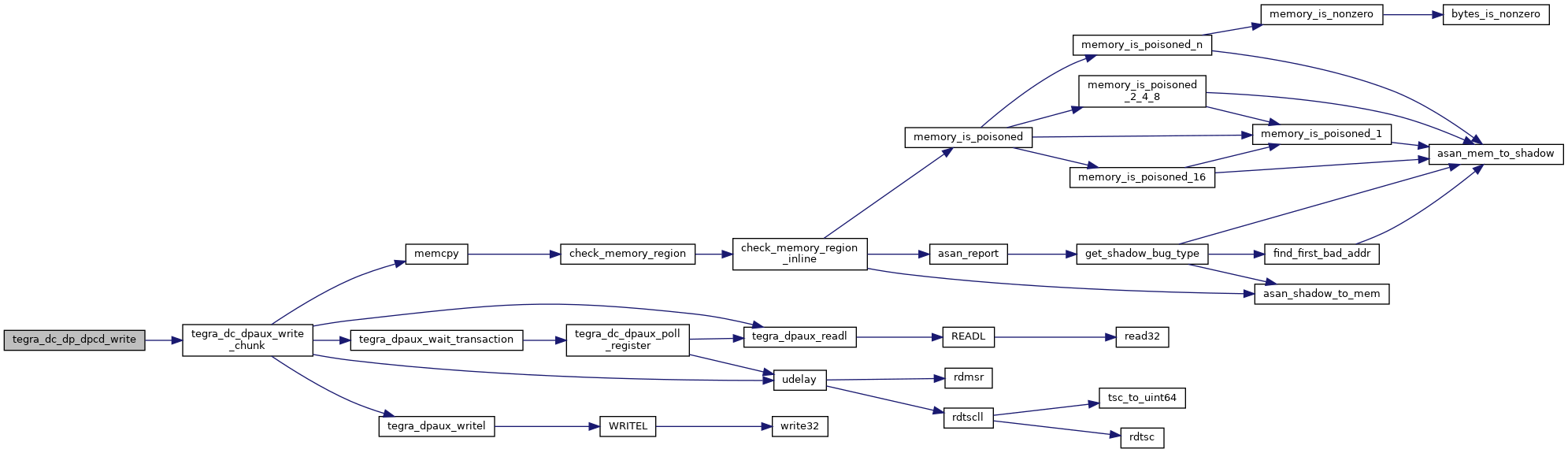

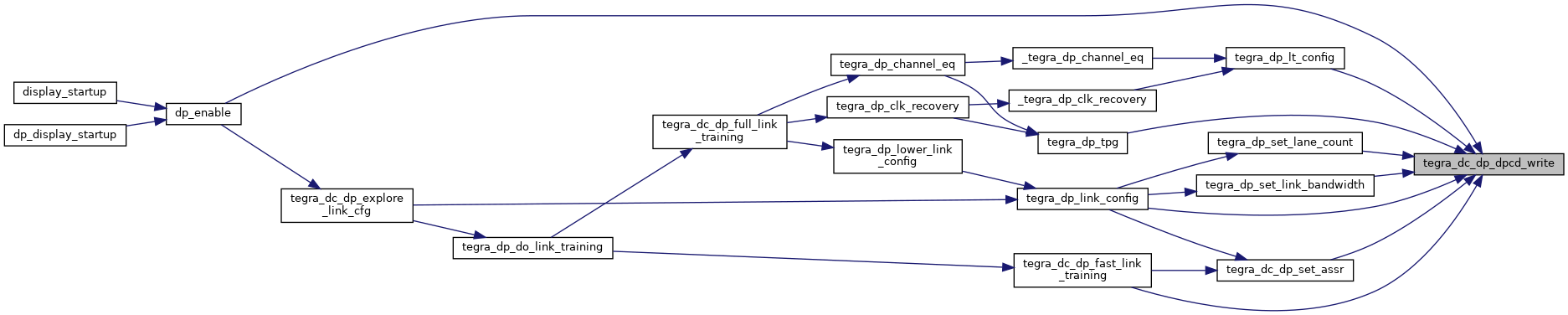

static |

Definition at line 333 of file dp.c.

References BIOS_ERR, DPAUX_DP_AUXCTL_CMD_AUXWR, printk, and tegra_dc_dpaux_write_chunk().

Referenced by dp_enable(), tegra_dc_dp_fast_link_training(), tegra_dc_dp_set_assr(), tegra_dp_link_config(), tegra_dp_lt_config(), tegra_dp_set_lane_count(), tegra_dp_set_link_bandwidth(), and tegra_dp_tpg().

|

static |

Definition at line 403 of file dp.c.

References tegra_dc_dp_link_config::active_count, tegra_dc_dp_link_config::active_frac, tegra_dc_dp_link_config::activepolarity, BIOS_INFO, tegra_dc_dp_link_config::bits_per_pixel, tegra_dc_dp_link_config::enhanced_framing, tegra_dc_dp_link_config::hblank_sym, tegra_dc_dp_link_config::lane_count, tegra_dc_dp_link_config::link_bw, tegra_dc_dp_data::link_cfg, tegra_dc_dp_link_config::max_lane_count, tegra_dc_dp_link_config::max_link_bw, printk, tegra_dc_dp_link_config::scramble_ena, tegra_dc_dp_link_config::support_enhanced_framing, tegra_dc_dp_link_config::tu_size, tegra_dc_dp_link_config::vblank_sym, and tegra_dc_dp_link_config::watermark.

Referenced by tegra_dc_dp_calc_config(), and tegra_dc_dp_full_link_training().

|

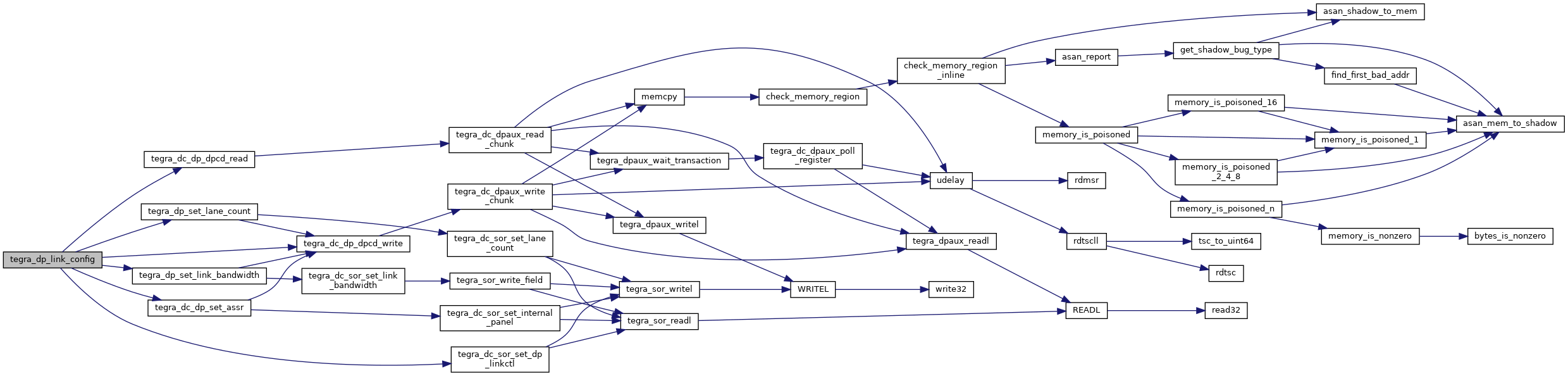

static |

Definition at line 1261 of file dp.c.

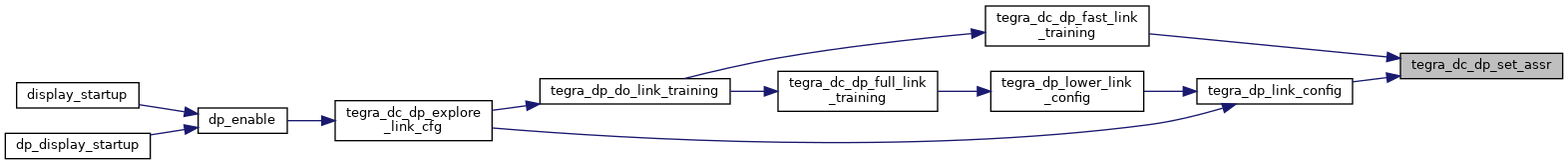

References BIOS_ERR, config, EFAULT, EINVAL, tegra_dc_dp_link_config::is_valid, tegra_dc_dp_link_config::lane_count, tegra_dc_dp_link_config::link_bw, tegra_dc_dp_link_config::max_lane_count, tegra_dc_dp_link_config::max_link_bw, memcpy(), printk, tegra_dc_dp_calc_config(), tegra_dp_do_link_training(), and tegra_dp_link_config().

Referenced by dp_enable().

|

static |

Definition at line 1151 of file dp.c.

References BIOS_ERR, BIOS_INFO, DPAUX_DP_AUXCTL_CMD_AUXRD, EFAULT, tegra_dc_dp_link_config::lane_count, tegra_dc_dp_link_config::link_bw, tegra_dc_sor_data::link_cfg, mask, NV_DPCD_LANE0_1_STATUS, NV_DPCD_MAIN_LINK_CHANNEL_CODING_SET, NV_DPCD_MAIN_LINK_CHANNEL_CODING_SET_ANSI_8B10B, NV_DPCD_TRAINING_LANE0_SET, NV_DPCD_TRAINING_PATTERN_SET, NV_DPCD_TRAINING_PATTERN_SET_TPS_TP1, printk, tegra_dc_dp_link_config::scramble_ena, tegra_dc_dp_data::sor, tegra_dc_dp_dpcd_write(), tegra_dc_dp_link_trained(), tegra_dc_dp_set_assr(), tegra_dc_dpaux_read(), tegra_dc_sor_read_link_config(), tegra_dc_sor_set_dp_linkctl(), tegra_dc_sor_set_lane_parm(), training_pattern_1, training_pattern_3, training_pattern_disabled, and udelay().

Referenced by tegra_dp_do_link_training().

|

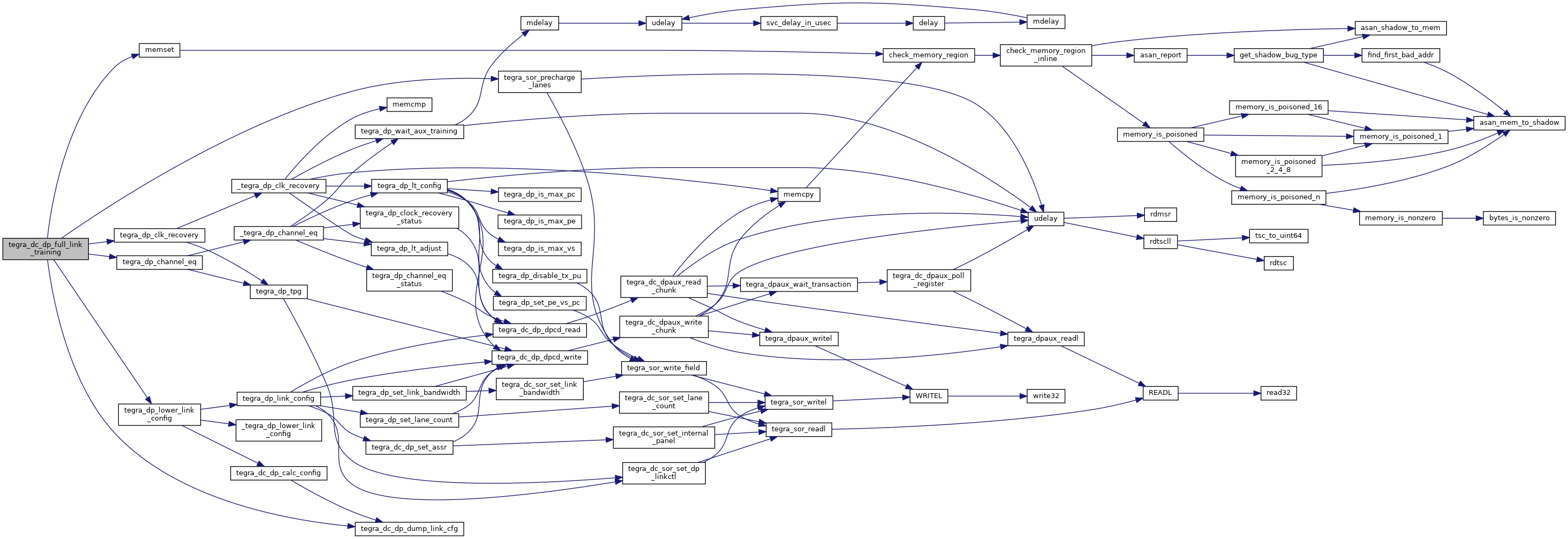

static |

Definition at line 1108 of file dp.c.

References BIOS_ERR, DP_LT_SUCCESS, driveCurrent_Level0, tegra_dc_dp_data::link_cfg, memset(), postCursor2_Level0, preEmphasis_Disabled, printk, tegra_dc_dp_data::sor, tegra_dc_dp_dump_link_cfg(), tegra_dp_channel_eq(), tegra_dp_clk_recovery(), tegra_dp_lower_link_config(), and tegra_sor_precharge_lanes().

Referenced by tegra_dp_do_link_training().

|

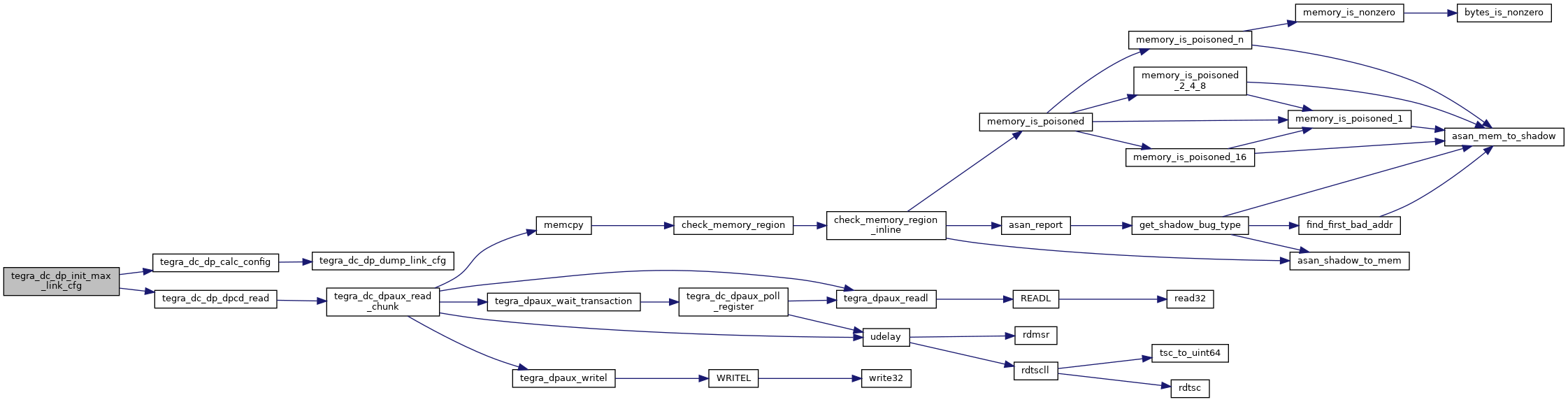

static |

Definition at line 637 of file dp.c.

References tegra_dc_dp_link_config::alt_scramber_reset_cap, tegra_dc_dp_link_config::aux_rd_interval, tegra_dc_dp_link_config::bits_per_pixel, CHECK_RET, config, tegra_dc_dp_link_config::downspread, tegra_dc_dp_link_config::drive_current, tegra_dc_dp_link_config::enhanced_framing, tegra_dc_dp_link_config::lane_count, tegra_dc_dp_link_config::link_bw, tegra_dc_dp_data::link_cfg, tegra_dc_dp_link_config::max_lane_count, tegra_dc_dp_link_config::max_link_bw, NV_DPCD_EDP_CONFIG_CAP, NV_DPCD_EDP_CONFIG_CAP_ASC_RESET_YES, NV_DPCD_EDP_CONFIG_CAP_FRAMING_CHANGE_YES, NV_DPCD_MAX_DOWNSPREAD, NV_DPCD_MAX_DOWNSPREAD_VAL_0_5_PCT, NV_DPCD_MAX_LANE_COUNT, NV_DPCD_MAX_LANE_COUNT_ENHANCED_FRAMING_YES, NV_DPCD_MAX_LANE_COUNT_MASK, NV_DPCD_MAX_LANE_COUNT_TPS3_SUPPORTED_YES, NV_DPCD_MAX_LINK_BANDWIDTH, NV_DPCD_TRAINING_AUX_RD_INTERVAL, tegra_dc_dp_link_config::only_enhanced_framing, tegra_dc_dp_link_config::postcursor, tegra_dc_dp_link_config::preemphasis, tegra_dc_dp_link_config::support_enhanced_framing, tegra_dc_dp_calc_config(), tegra_dc_dp_dpcd_read(), and tegra_dc_dp_link_config::tps3_supported.

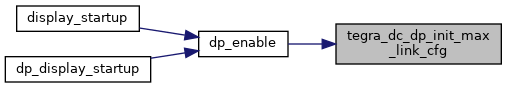

Referenced by dp_enable().

|

static |

Definition at line 736 of file dp.c.

References CHECK_RET, tegra_dc_dp_link_config::lane_count, mask, NV_DPCD_LANE0_1_STATUS, NV_DPCD_LANE2_3_STATUS, NV_DPCD_STATUS_LANEX_CHN_EQ_DONE_YES, NV_DPCD_STATUS_LANEX_CR_DONE_YES, NV_DPCD_STATUS_LANEX_SYMBOL_LOCKED_YES, NV_DPCD_STATUS_LANEXPLUS1_CHN_EQ_DONE_YES, NV_DPCD_STATUS_LANEXPLUS1_CR_DONE_YES, NV_DPCD_STATUS_LANEXPLUS1_SYMBOL_LOCKED_YES, and tegra_dc_dp_dpcd_read().

Referenced by tegra_dc_dp_fast_link_training().

|

static |

Definition at line 693 of file dp.c.

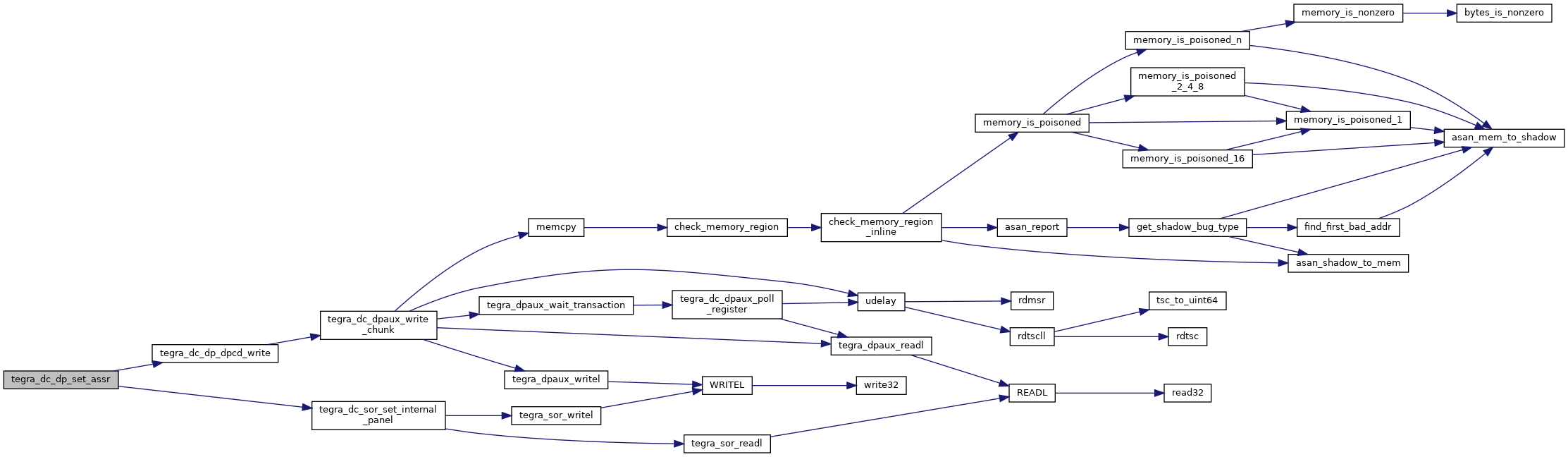

References CHECK_RET, NV_DPCD_EDP_CONFIG_SET, NV_DPCD_EDP_CONFIG_SET_ASC_RESET_DISABLE, NV_DPCD_EDP_CONFIG_SET_ASC_RESET_ENABLE, tegra_dc_dp_data::sor, tegra_dc_dp_dpcd_write(), and tegra_dc_sor_set_internal_panel().

Referenced by tegra_dc_dp_fast_link_training(), and tegra_dp_link_config().

|

static |

Definition at line 386 of file dp.c.

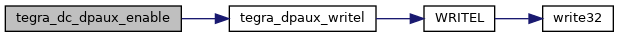

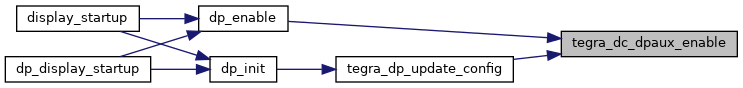

References DPAUX_HYBRID_PADCTL, DPAUX_HYBRID_PADCTL_AUX_CMH_V0_70, DPAUX_HYBRID_PADCTL_AUX_DRVI_SHIFT, DPAUX_HYBRID_PADCTL_AUX_DRVZ_OHM_50, DPAUX_HYBRID_PADCTL_AUX_INPUT_RCV_ENABLE, DPAUX_HYBRID_SPARE, DPAUX_HYBRID_SPARE_PAD_PWR_POWERUP, DPAUX_INTR_AUX, DPAUX_INTR_EN_AUX, and tegra_dpaux_writel().

Referenced by dp_enable(), and tegra_dp_update_config().

|

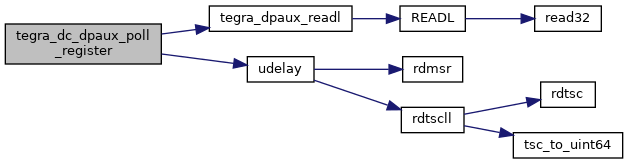

inlinestatic |

Definition at line 43 of file dp.c.

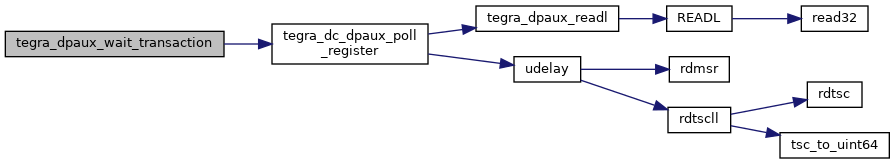

References BIOS_ERR, mask, printk, tegra_dpaux_readl(), and udelay().

Referenced by tegra_dpaux_wait_transaction().

|

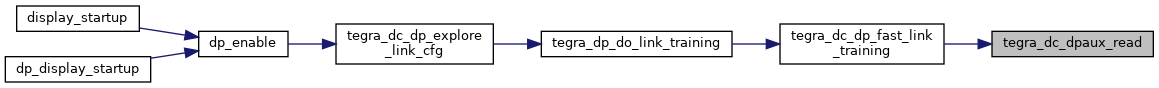

static |

Definition at line 288 of file dp.c.

References addr, DP_AUX_MAX_BYTES, and tegra_dc_dpaux_read_chunk().

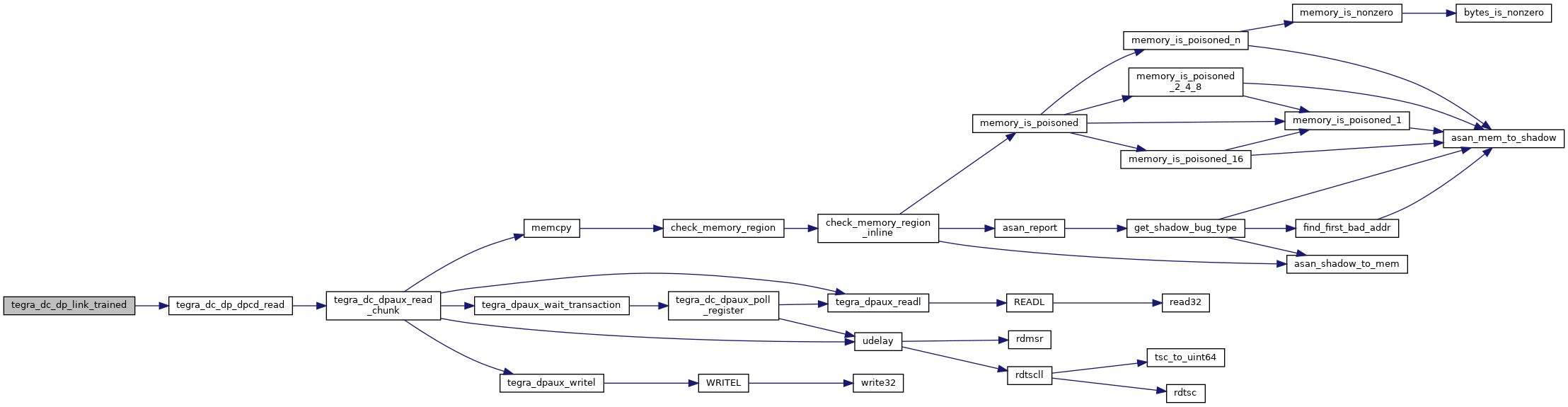

Referenced by tegra_dc_dp_fast_link_training().

|

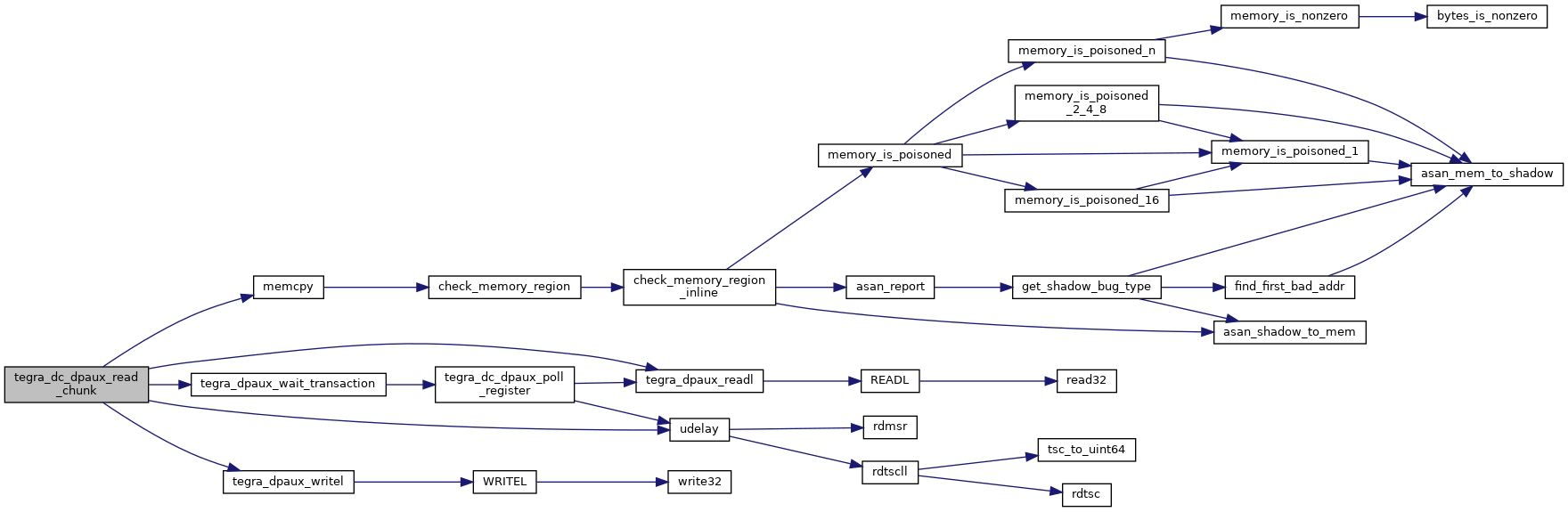

static |

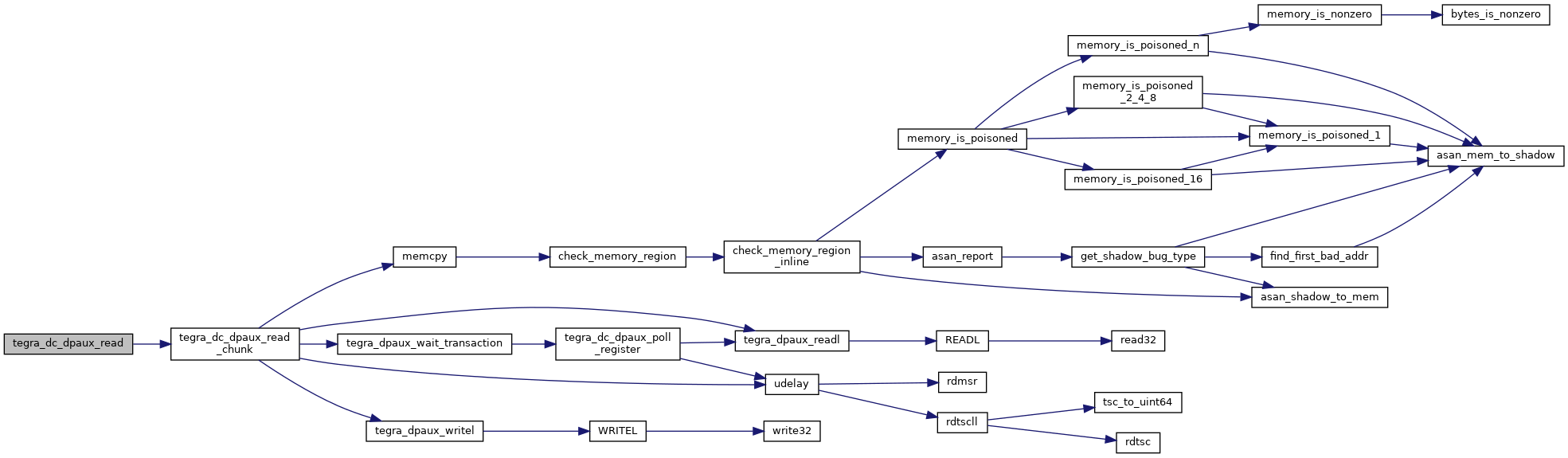

Definition at line 180 of file dp.c.

References addr, BIOS_ERR, BIOS_INFO, BIOS_SPEW, DP_AUX_DEFER_MAX_TRIES, DP_AUX_MAX_BYTES, DP_AUX_TIMEOUT_MAX_TRIES, DP_DPCP_RETRY_SLEEP_NS, DPAUX_DP_AUXADDR, DPAUX_DP_AUXCTL, DPAUX_DP_AUXCTL_CMD_AUXRD, DPAUX_DP_AUXCTL_CMD_I2CRD, DPAUX_DP_AUXCTL_CMD_I2CREQWSTAT, DPAUX_DP_AUXCTL_CMD_MASK, DPAUX_DP_AUXCTL_CMD_MOTRD, DPAUX_DP_AUXCTL_CMDLEN_FIELD, DPAUX_DP_AUXCTL_CMDLEN_SHIFT, DPAUX_DP_AUXCTL_TRANSACTREQ_PENDING, DPAUX_DP_AUXDATA_READ_W, DPAUX_DP_AUXSTAT, DPAUX_DP_AUXSTAT_HPD_STATUS_PLUGGED, DPAUX_DP_AUXSTAT_NO_STOP_ERROR_PENDING, DPAUX_DP_AUXSTAT_REPLY_M_MASK, DPAUX_DP_AUXSTAT_REPLYTYPE_ACK, DPAUX_DP_AUXSTAT_REPLYTYPE_DEFER, DPAUX_DP_AUXSTAT_REPLYTYPE_I2CDEFER, DPAUX_DP_AUXSTAT_REPLYTYPE_MASK, DPAUX_DP_AUXSTAT_RX_ERROR_PENDING, DPAUX_DP_AUXSTAT_SINKSTAT_ERROR_PENDING, DPAUX_DP_AUXSTAT_TIMEOUT_ERROR_PENDING, memcpy(), printk, tegra_dpaux_readl(), tegra_dpaux_wait_transaction(), tegra_dpaux_writel(), and udelay().

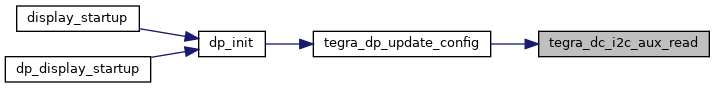

Referenced by tegra_dc_dp_dpcd_read(), tegra_dc_dpaux_read(), and tegra_dc_i2c_aux_read().

|

static |

Definition at line 83 of file dp.c.

References addr, BIOS_ERR, BIOS_INFO, DP_AUX_DEFER_MAX_TRIES, DP_AUX_MAX_BYTES, DP_AUX_TIMEOUT_MAX_TRIES, DPAUX_DP_AUXADDR, DPAUX_DP_AUXCTL, DPAUX_DP_AUXCTL_CMD_AUXWR, DPAUX_DP_AUXCTL_CMD_I2CWR, DPAUX_DP_AUXCTL_CMD_MASK, DPAUX_DP_AUXCTL_CMD_MOTWR, DPAUX_DP_AUXCTL_CMDLEN_FIELD, DPAUX_DP_AUXCTL_CMDLEN_SHIFT, DPAUX_DP_AUXCTL_TRANSACTREQ_PENDING, DPAUX_DP_AUXDATA_WRITE_W, DPAUX_DP_AUXSTAT, DPAUX_DP_AUXSTAT_NO_STOP_ERROR_PENDING, DPAUX_DP_AUXSTAT_REPLY_M_MASK, DPAUX_DP_AUXSTAT_REPLYTYPE_ACK, DPAUX_DP_AUXSTAT_REPLYTYPE_DEFER, DPAUX_DP_AUXSTAT_REPLYTYPE_I2CDEFER, DPAUX_DP_AUXSTAT_REPLYTYPE_MASK, DPAUX_DP_AUXSTAT_RX_ERROR_PENDING, DPAUX_DP_AUXSTAT_SINKSTAT_ERROR_PENDING, DPAUX_DP_AUXSTAT_TIMEOUT_ERROR_PENDING, memcpy(), printk, tegra_dpaux_readl(), tegra_dpaux_wait_transaction(), tegra_dpaux_writel(), and udelay().

Referenced by tegra_dc_dp_dpcd_write(), and tegra_dc_i2c_aux_read().

|

static |

Definition at line 349 of file dp.c.

References addr, BIOS_ERR, DP_AUX_MAX_BYTES, DPAUX_DP_AUXCTL_CMD_I2CRD, DPAUX_DP_AUXCTL_CMD_MOTWR, MIN, printk, tegra_dc_dpaux_read_chunk(), and tegra_dc_dpaux_write_chunk().

Referenced by tegra_dp_update_config().

|

static |

Definition at line 1046 of file dp.c.

References _tegra_dp_channel_eq(), tegra_dc_dp_link_config::lane_count, tegra_dc_dp_data::link_cfg, tegra_dp_tpg(), tegra_dc_dp_link_config::tps3_supported, training_pattern_2, training_pattern_3, and training_pattern_disabled.

Referenced by tegra_dc_dp_full_link_training().

|

static |

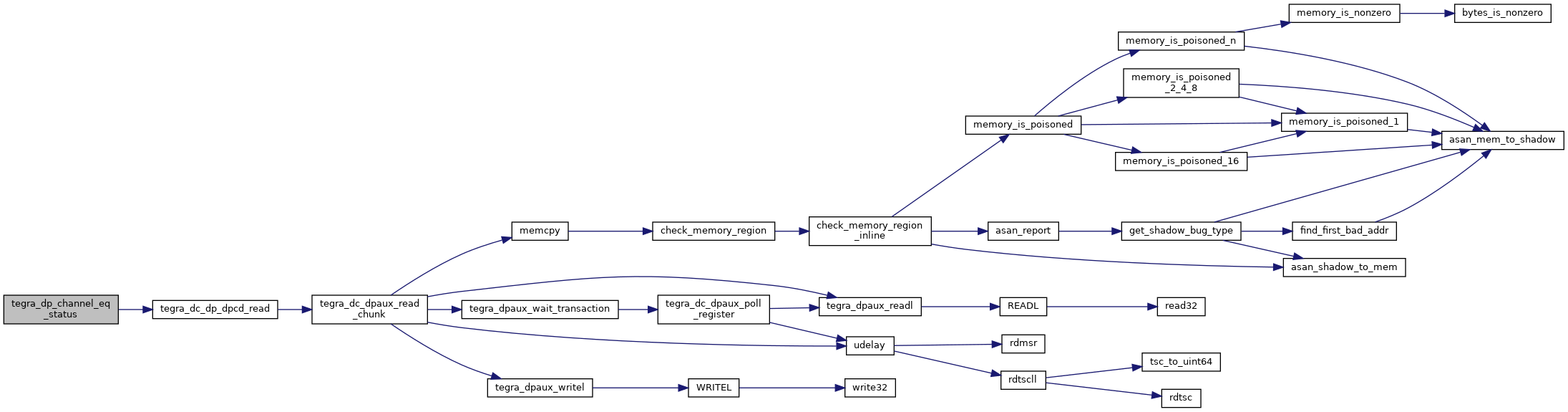

Definition at line 761 of file dp.c.

References tegra_dc_dp_link_config::lane_count, tegra_dc_dp_data::link_cfg, NV_DPCD_LANE0_1_STATUS, NV_DPCD_LANE_ALIGN_STATUS_UPDATED, NV_DPCD_LANE_ALIGN_STATUS_UPDATED_DONE_YES, NV_DPCD_STATUS_LANEX_CHN_EQ_DONE_SHIFT, NV_DPCD_STATUS_LANEX_SYMBOL_LOCKED_SHFIT, NV_DPCD_STATUS_LANEXPLUS1_CHN_EQ_DONE_SHIFT, NV_DPCD_STATUS_LANEXPLUS1_SYMBOL_LOCKED_SHIFT, and tegra_dc_dp_dpcd_read().

Referenced by _tegra_dp_channel_eq().

|

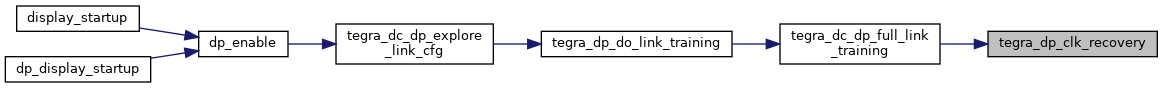

static |

Definition at line 1092 of file dp.c.

References _tegra_dp_clk_recovery(), tegra_dc_dp_link_config::lane_count, tegra_dc_dp_data::link_cfg, tegra_dp_tpg(), tegra_dc_dp_link_config::tps3_supported, training_pattern_1, and training_pattern_disabled.

Referenced by tegra_dc_dp_full_link_training().

|

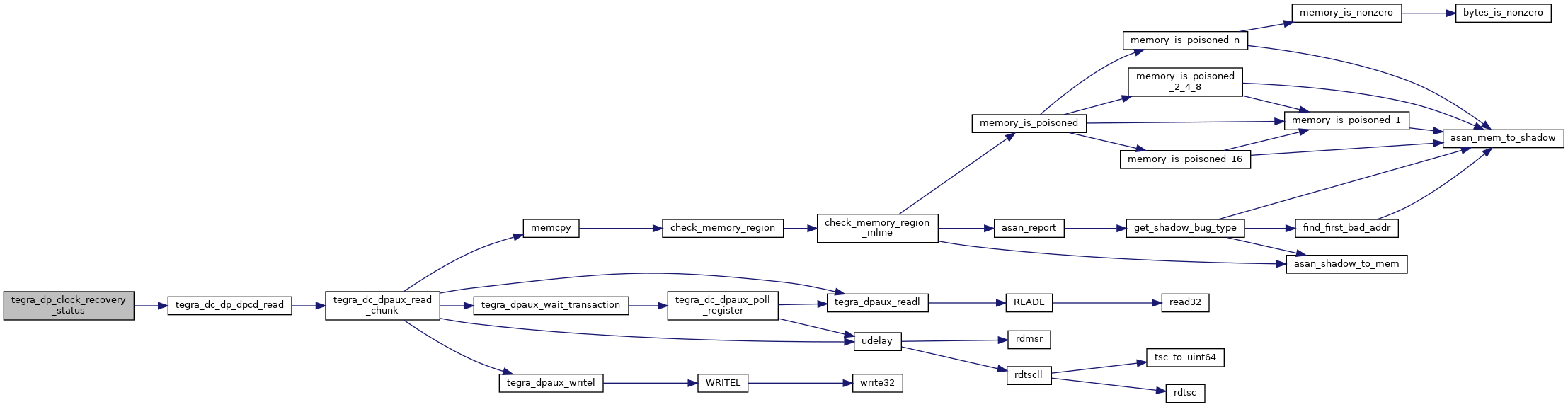

static |

Definition at line 792 of file dp.c.

References tegra_dc_dp_link_config::lane_count, tegra_dc_dp_data::link_cfg, NV_DPCD_LANE0_1_STATUS, NV_DPCD_STATUS_LANEX_CR_DONE_YES, NV_DPCD_STATUS_LANEXPLUS1_CR_DONE_YES, and tegra_dc_dp_dpcd_read().

Referenced by _tegra_dp_channel_eq(), and _tegra_dp_clk_recovery().

|

static |

Definition at line 1228 of file dp.c.

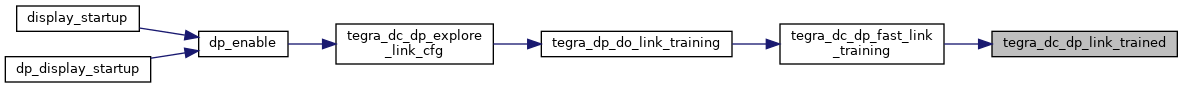

References BIOS_ERR, EFAULT, tegra_dc_dp_link_config::lane_count, tegra_dc_dp_link_config::link_bw, tegra_dc_sor_data::link_cfg, printk, tegra_dc_dp_data::sor, tegra_dc_dp_fast_link_training(), tegra_dc_dp_full_link_training(), tegra_dc_sor_read_link_config(), and tegra_dc_sor_set_voltage_swing().

Referenced by tegra_dc_dp_explore_link_cfg().

|

static |

Definition at line 1367 of file dp.c.

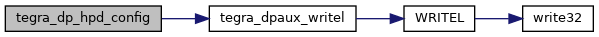

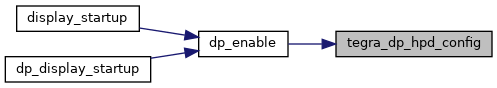

References config, DPAUX_HPD_CONFIG, DPAUX_HPD_CONFIG_UNPLUG_MIN_TIME_SHIFT, DPAUX_HPD_IRQ_CONFIG, tegra_dpaux_writel(), and val.

Referenced by dp_enable().

|

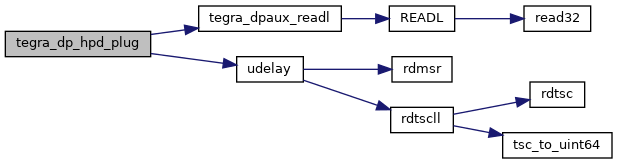

static |

Definition at line 1380 of file dp.c.

References DPAUX_DP_AUXSTAT, DPAUX_DP_AUXSTAT_HPD_STATUS_PLUGGED, tegra_dpaux_readl(), udelay(), and val.

Referenced by dp_enable().

|

static |

Definition at line 868 of file dp.c.

References tegra_dc_dp_link_config::alt_scramber_reset_cap, BIOS_ERR, DP_LT_FAILED, DP_LT_SUCCESS, tegra_dc_dp_link_config::lane_count, tegra_dc_dp_link_config::link_bw, tegra_dc_dp_data::link_cfg, NV_DPCD_SET_POWER, NV_DPCD_SET_POWER_VAL_D0_NORMAL, NV_DPCD_SET_POWER_VAL_D3_PWRDWN, printk, retry, tegra_dc_dp_data::sor, tegra_dc_dp_dpcd_read(), tegra_dc_dp_dpcd_write(), tegra_dc_dp_set_assr(), tegra_dc_sor_set_dp_linkctl(), tegra_dp_set_lane_count(), tegra_dp_set_link_bandwidth(), and training_pattern_none.

Referenced by tegra_dc_dp_explore_link_cfg(), and tegra_dp_lower_link_config().

|

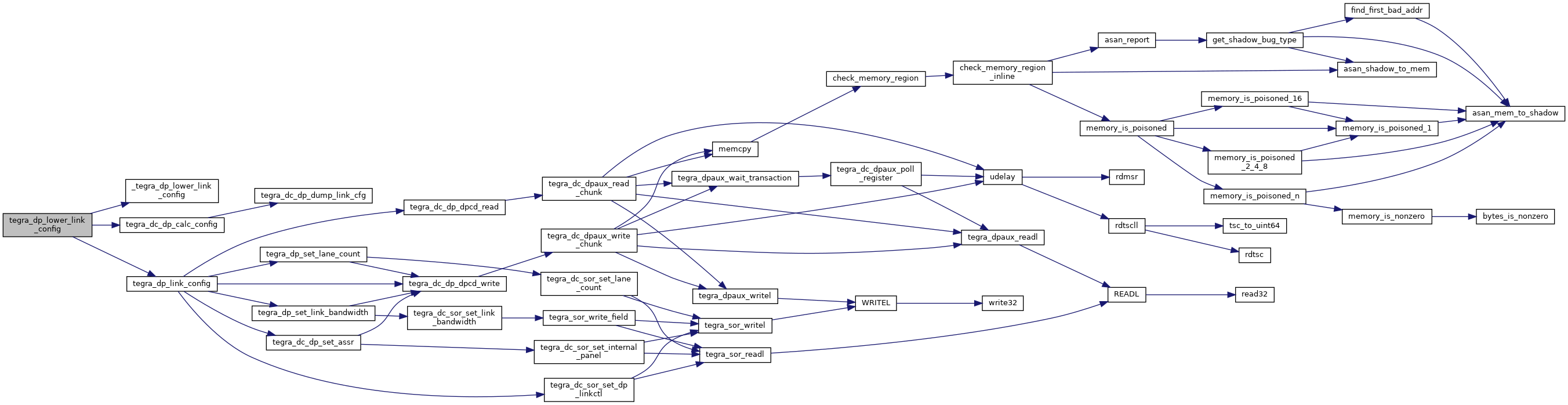

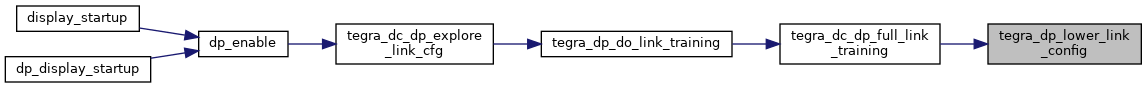

static |

Definition at line 916 of file dp.c.

References _tegra_dp_lower_link_config(), tegra_dc::config, tegra_dc_dp_data::dc, DP_LT_FAILED, DP_LT_SUCCESS, tegra_dc_dp_link_config::is_valid, tegra_dc_dp_data::link_cfg, tegra_dc_dp_calc_config(), and tegra_dp_link_config().

Referenced by tegra_dc_dp_full_link_training().

|

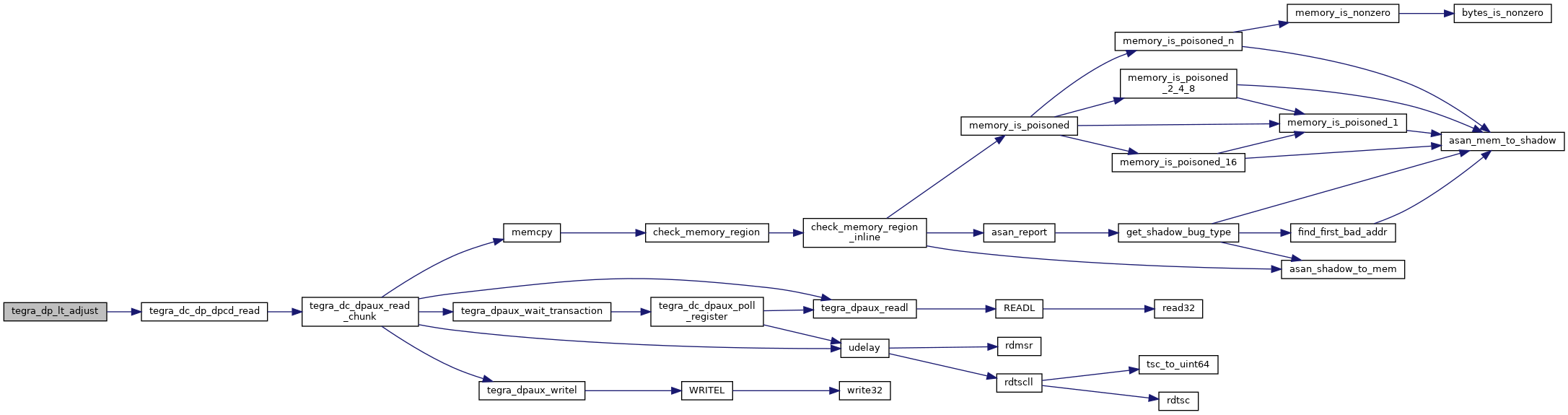

static |

Definition at line 813 of file dp.c.

References tegra_dc_dp_link_config::lane_count, tegra_dc_dp_data::link_cfg, NV_DPCD_ADJUST_REQ_LANEX_DC_MASK, NV_DPCD_ADJUST_REQ_LANEX_DC_SHIFT, NV_DPCD_ADJUST_REQ_LANEX_PE_MASK, NV_DPCD_ADJUST_REQ_LANEX_PE_SHIFT, NV_DPCD_ADJUST_REQ_LANEXPLUS1_DC_MASK, NV_DPCD_ADJUST_REQ_LANEXPLUS1_DC_SHIFT, NV_DPCD_ADJUST_REQ_LANEXPLUS1_PE_MASK, NV_DPCD_ADJUST_REQ_LANEXPLUS1_PE_SHIFT, NV_DPCD_ADJUST_REQ_POST_CURSOR2, NV_DPCD_ADJUST_REQ_POST_CURSOR2_LANE_MASK, NV_DPCD_ADJUST_REQ_POST_CURSOR2_LANE_SHIFT, NV_DPCD_LANE0_1_ADJUST_REQ, and tegra_dc_dp_dpcd_read().

Referenced by _tegra_dp_channel_eq(), and _tegra_dp_clk_recovery().

|

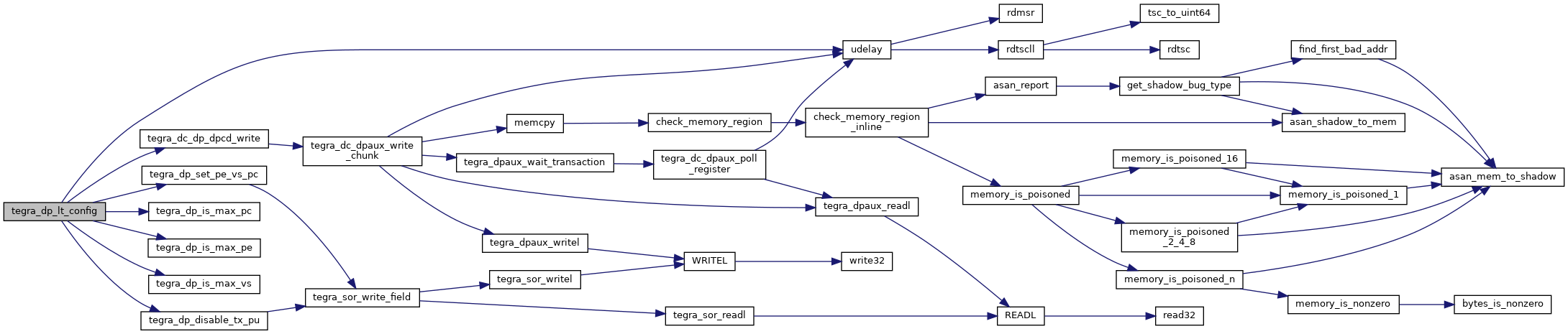

static |

Definition at line 938 of file dp.c.

References BIOS_ERR, tegra_dc_dp_link_config::lane_count, tegra_dc_dp_data::link_cfg, mask, NV_DPCD_LANEX_SET2_PC2_MAX_REACHED_F, NV_DPCD_LANEX_SET2_PC2_MAX_REACHED_T, NV_DPCD_LANEX_SET2_PC2_SHIFT, NV_DPCD_LANEXPLUS1_SET2_PC2_MAX_REACHED_F, NV_DPCD_LANEXPLUS1_SET2_PC2_MAX_REACHED_T, NV_DPCD_LANEXPLUS1_SET2_PC2_SHIFT, NV_DPCD_TRAINING_LANE0_1_SET2, NV_DPCD_TRAINING_LANE0_SET, NV_DPCD_TRAINING_LANEX_SET_DC_MAX_REACHED_F, NV_DPCD_TRAINING_LANEX_SET_DC_MAX_REACHED_T, NV_DPCD_TRAINING_LANEX_SET_DC_SHIFT, NV_DPCD_TRAINING_LANEX_SET_PE_MAX_REACHED_F, NV_DPCD_TRAINING_LANEX_SET_PE_MAX_REACHED_T, NV_DPCD_TRAINING_LANEX_SET_PE_SHIFT, NV_SOR_PR_LANE0_DP_LANE2_MASK, NV_SOR_PR_LANE0_DP_LANE2_SHIFT, NV_SOR_PR_LANE1_DP_LANE1_MASK, NV_SOR_PR_LANE1_DP_LANE1_SHIFT, NV_SOR_PR_LANE2_DP_LANE0_MASK, NV_SOR_PR_LANE2_DP_LANE0_SHIFT, NV_SOR_PR_LANE3_DP_LANE3_MASK, NV_SOR_PR_LANE3_DP_LANE3_SHIFT, printk, tegra_dc_dp_data::sor, tegra_dc_dp_dpcd_write(), tegra_dp_disable_tx_pu(), tegra_dp_is_max_pc(), tegra_dp_is_max_pe(), tegra_dp_is_max_vs(), tegra_dp_pc_regs, tegra_dp_pe_regs, tegra_dp_set_pe_vs_pc(), tegra_dp_vs_regs, tegra_dc_dp_link_config::tps3_supported, udelay(), and val.

Referenced by _tegra_dp_channel_eq(), and _tegra_dp_clk_recovery().

|

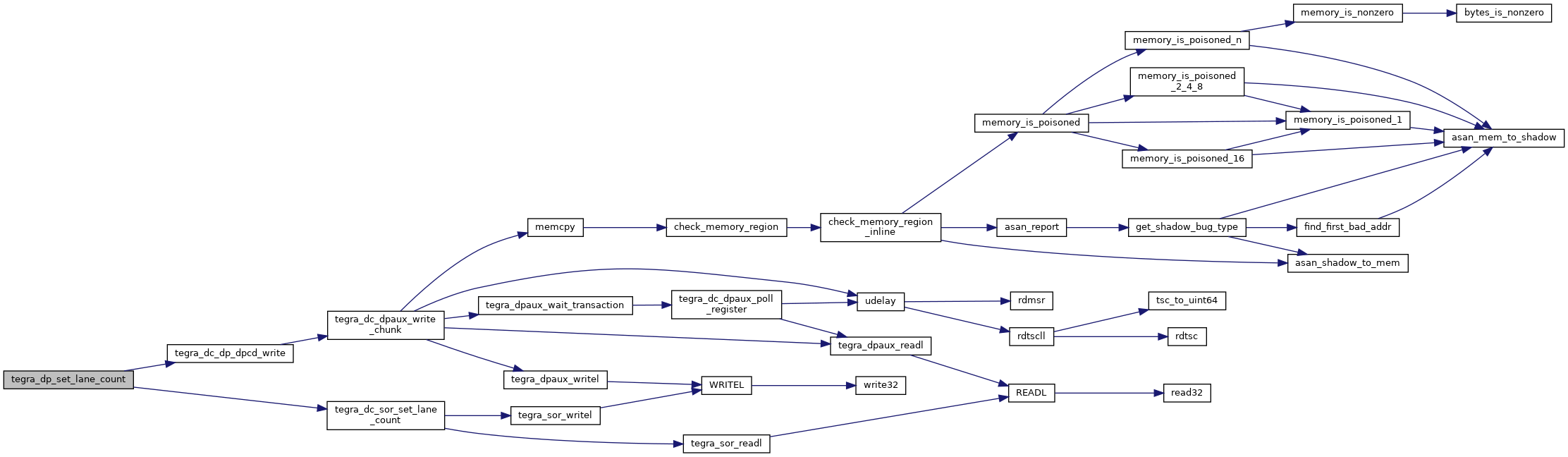

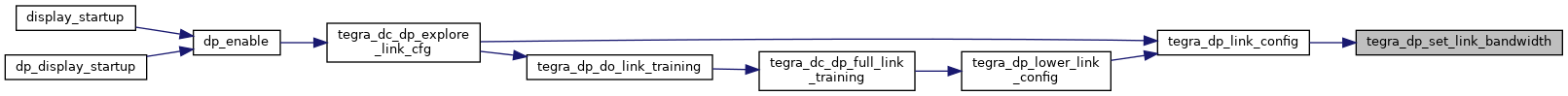

static |

Definition at line 717 of file dp.c.

References CHECK_RET, tegra_dc_dp_link_config::enhanced_framing, tegra_dc_dp_link_config::lane_count, tegra_dc_dp_data::link_cfg, NV_DPCD_LANE_COUNT_SET, NV_DPCD_LANE_COUNT_SET_ENHANCEDFRAMING_T, tegra_dc_dp_data::sor, tegra_dc_dp_dpcd_write(), and tegra_dc_sor_set_lane_count().

Referenced by tegra_dp_link_config().

|

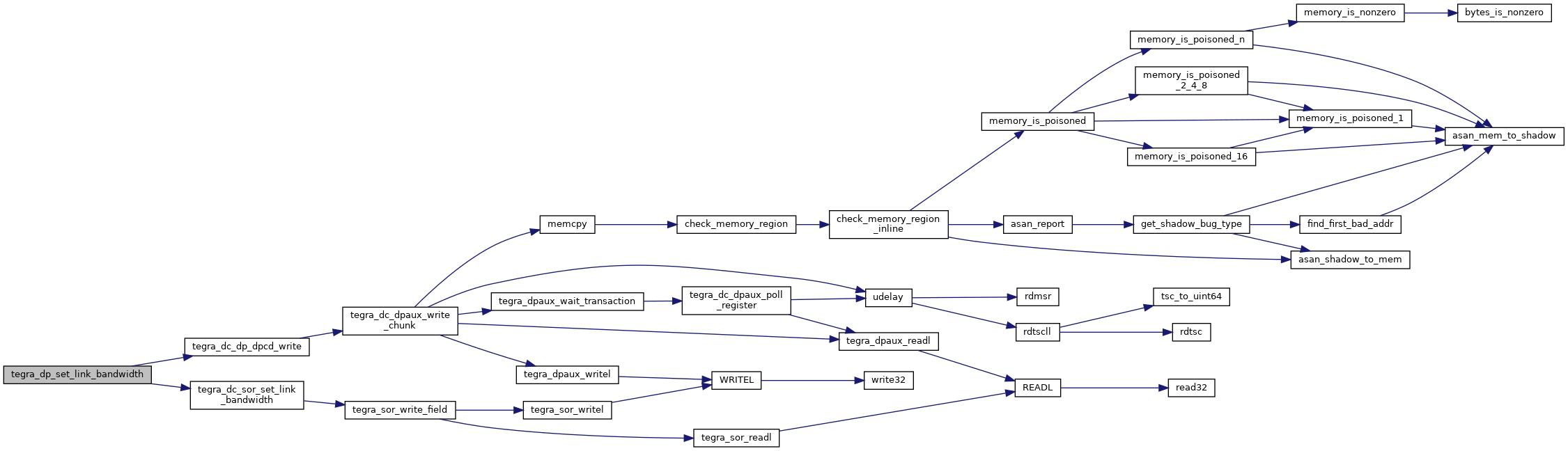

static |

Definition at line 709 of file dp.c.

References NV_DPCD_LINK_BANDWIDTH_SET, tegra_dc_dp_data::sor, tegra_dc_dp_dpcd_write(), and tegra_dc_sor_set_link_bandwidth().

Referenced by tegra_dp_link_config().

|

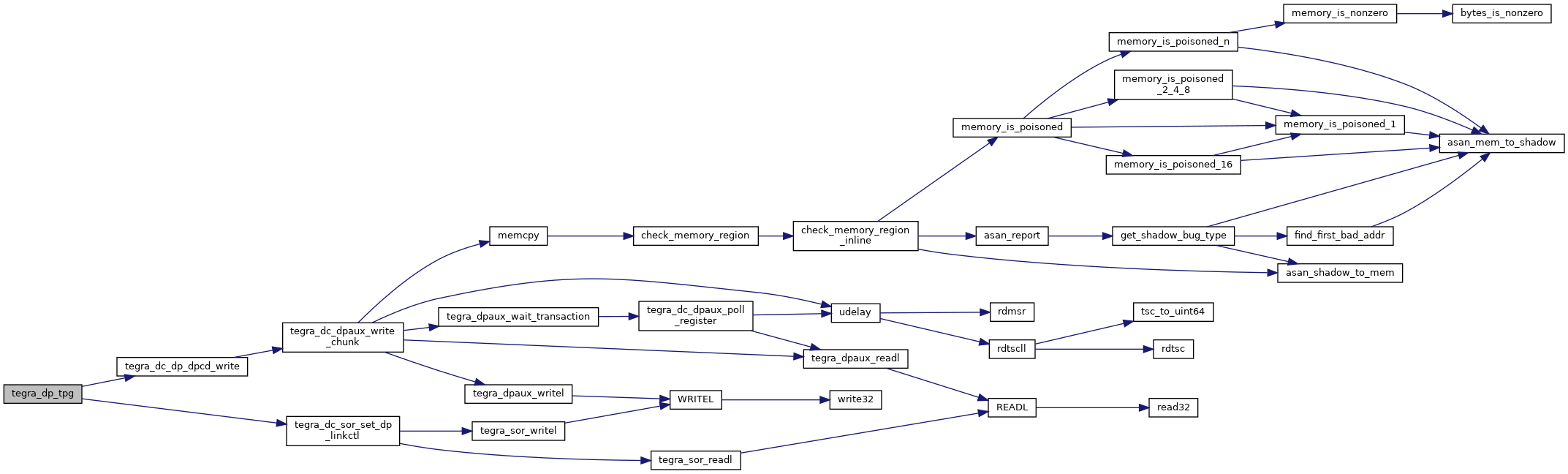

static |

Definition at line 858 of file dp.c.

References tegra_dc_dp_data::link_cfg, NV_DPCD_TRAINING_PATTERN_SET, NV_DPCD_TRAINING_PATTERN_SET_SC_DISABLED_F, NV_DPCD_TRAINING_PATTERN_SET_SC_DISABLED_T, tegra_dc_dp_data::sor, tegra_dc_dp_dpcd_write(), tegra_dc_sor_set_dp_linkctl(), and training_pattern_disabled.

Referenced by tegra_dp_channel_eq(), and tegra_dp_clk_recovery().

|

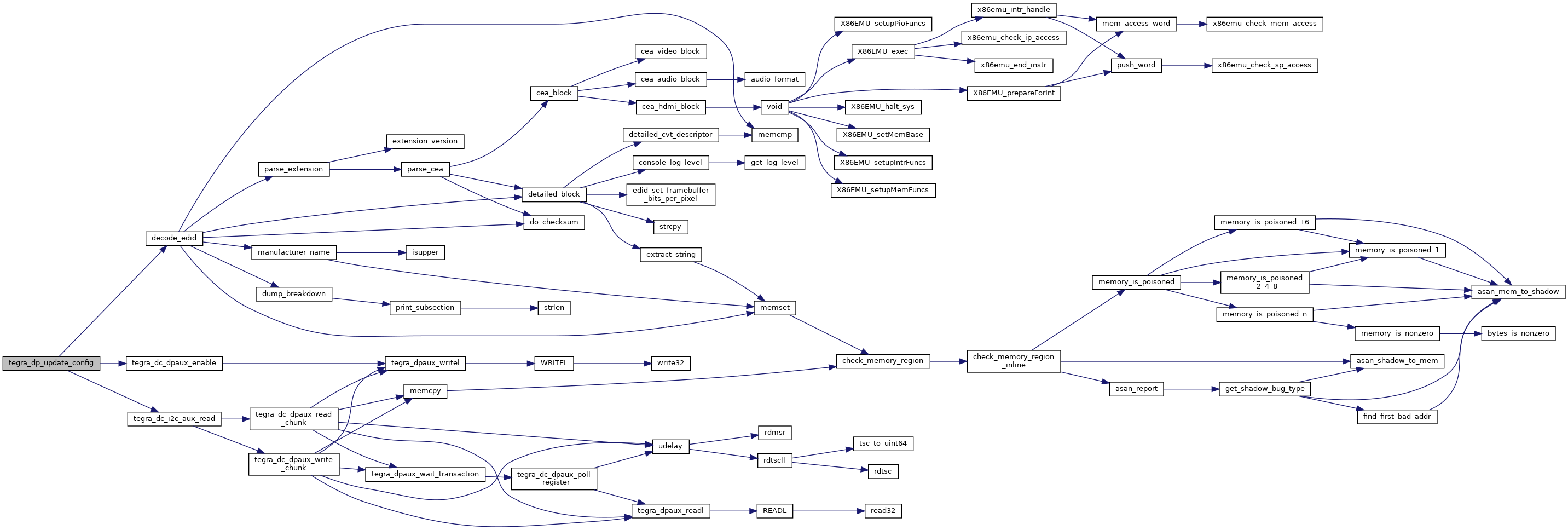

static |

Note edid->framebuffer_bits_per_pixel is currently hard-coded as 32, so we should keep the default value in device config.

EDID v1.3 panels may not have color depth info, so we need to check if these values are zero before updating config.

Definition at line 1297 of file dp.c.

References BIOS_ERR, BIOS_SPEW, buf, config, decode_edid(), EDID_CONFORMANT, edid_mode::ha, edid_mode::hbl, edid_mode::hso, edid_mode::hspw, edid::mode, edid::panel_bits_per_color, edid::panel_bits_per_pixel, edid_mode::pixel_clock, printk, tegra_dc_dpaux_enable(), tegra_dc_i2c_aux_read(), TEGRA_EDID_I2C_ADDRESS, edid_mode::va, edid_mode::vbl, edid_mode::vso, and edid_mode::vspw.

Referenced by dp_init().

|

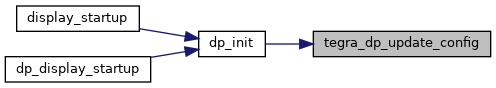

inlinestatic |

Definition at line 846 of file dp.c.

References tegra_dc_dp_link_config::aux_rd_interval, tegra_dc_dp_data::link_cfg, mdelay(), and udelay().

Referenced by _tegra_dp_channel_eq(), and _tegra_dp_clk_recovery().

|

inlinestatic |

Definition at line 29 of file dp.c.

References addr, tegra_dc_dp_data::aux_base, and READL().

Referenced by dp_enable(), tegra_dc_dpaux_poll_register(), tegra_dc_dpaux_read_chunk(), tegra_dc_dpaux_write_chunk(), and tegra_dp_hpd_plug().

|

inlinestatic |

Definition at line 69 of file dp.c.

References BIOS_INFO, DP_AUX_TIMEOUT_MS, DPAUX_DP_AUXCTL, DPAUX_DP_AUXCTL_TRANSACTREQ_DONE, DPAUX_DP_AUXCTL_TRANSACTREQ_MASK, printk, and tegra_dc_dpaux_poll_register().

Referenced by tegra_dc_dpaux_read_chunk(), and tegra_dc_dpaux_write_chunk().

|

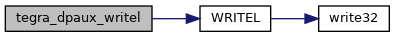

inlinestatic |

Definition at line 36 of file dp.c.

References addr, tegra_dc_dp_data::aux_base, val, and WRITEL().

Referenced by tegra_dc_dpaux_enable(), tegra_dc_dpaux_read_chunk(), tegra_dc_dpaux_write_chunk(), and tegra_dp_hpd_config().

| struct tegra_dc_dp_data dp_data |