|

coreboot

coreboot is an Open Source project aimed at replacing the proprietary BIOS found in most computers.

|

|

coreboot

coreboot is an Open Source project aimed at replacing the proprietary BIOS found in most computers.

|

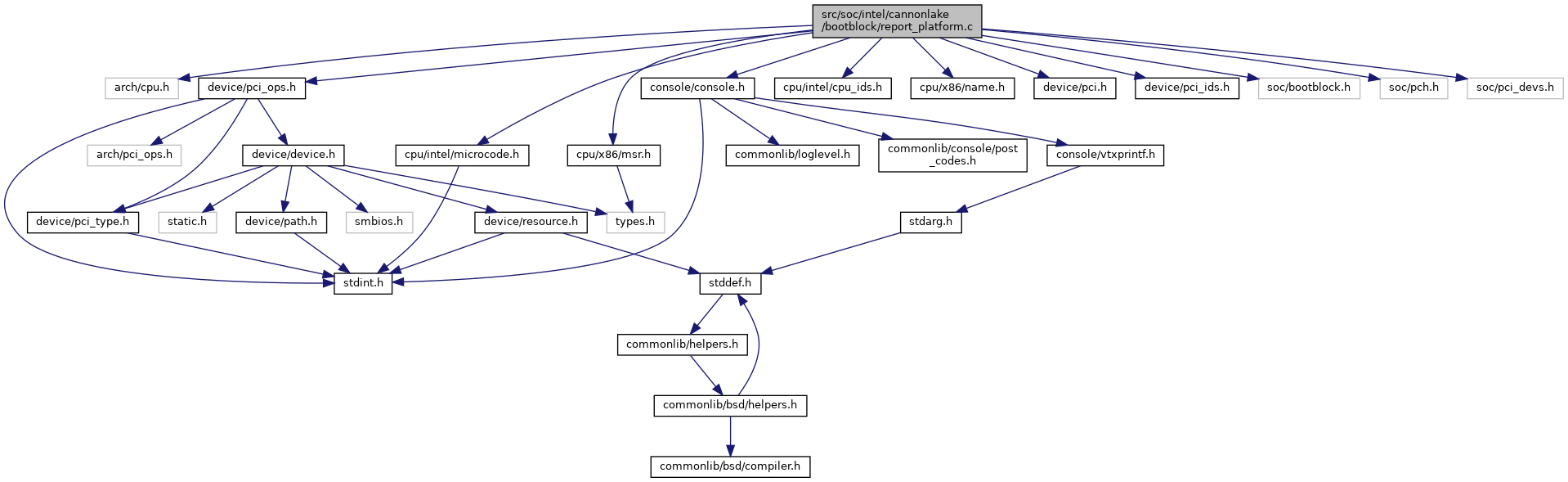

#include <arch/cpu.h>#include <device/pci_ops.h>#include <console/console.h>#include <cpu/intel/cpu_ids.h>#include <cpu/intel/microcode.h>#include <cpu/x86/msr.h>#include <cpu/x86/name.h>#include <device/pci.h>#include <device/pci_ids.h>#include <soc/bootblock.h>#include <soc/pch.h>#include <soc/pci_devs.h>

Go to the source code of this file.

Functions | |

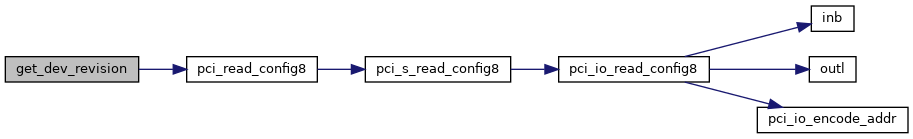

| static uint8_t | get_dev_revision (pci_devfn_t dev) |

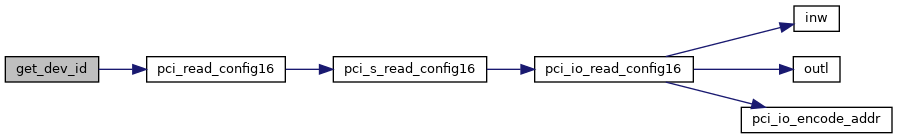

| static uint16_t | get_dev_id (pci_devfn_t dev) |

| static void | report_cpu_info (void) |

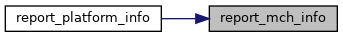

| static void | report_mch_info (void) |

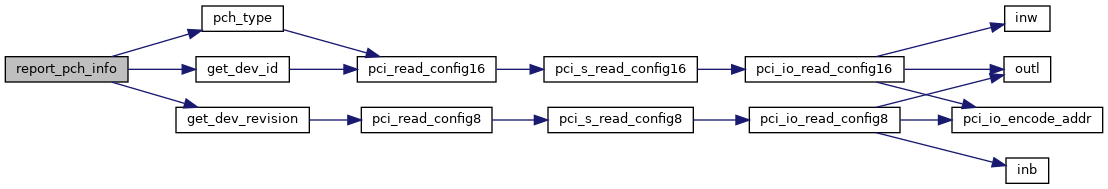

| static void | report_pch_info (void) |

| static void | report_igd_info (void) |

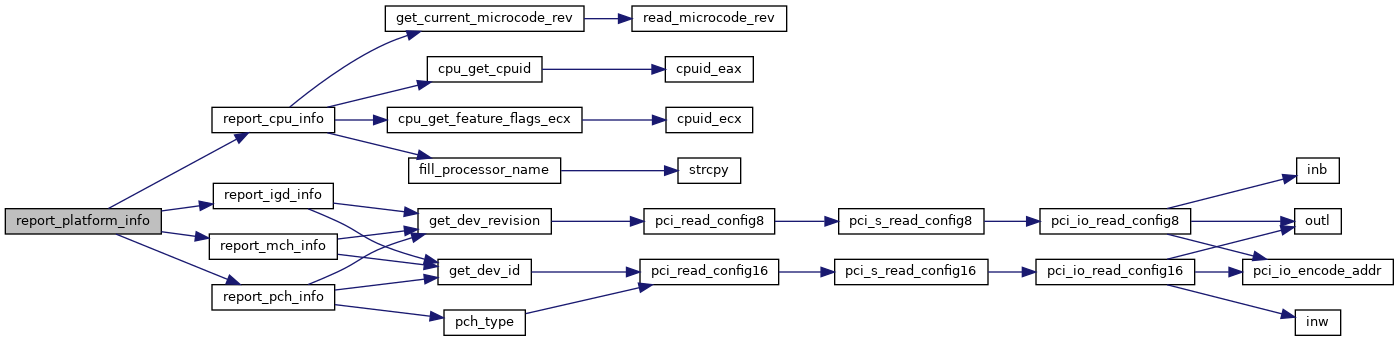

| void | report_platform_info (void) |

Variables | |

| struct { | |

| u32 cpuid | |

| const char * name | |

| } | cpu_table [] |

| struct { | |

| u16 mchid | |

| const char * name | |

| } | mch_table [] |

| struct { | |

| u16 lpcid | |

| const char * name | |

| } | pch_table [] |

| struct { | |

| u16 igdid | |

| const char * name | |

| } | igd_table [] |

|

static |

Definition at line 164 of file report_platform.c.

References PCI_DEVICE_ID, and pci_read_config16().

Referenced by report_igd_info(), report_mch_info(), and report_pch_info().

|

static |

Definition at line 159 of file report_platform.c.

References pci_read_config8(), and PCI_REVISION_ID.

Referenced by report_igd_info(), report_mch_info(), and report_pch_info().

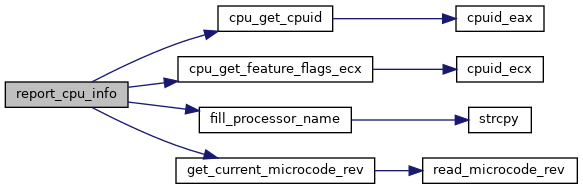

Definition at line 169 of file report_platform.c.

References ARRAY_SIZE, BIOS_DEBUG, cpu_get_cpuid(), cpu_get_feature_flags_ecx(), cpu_id, cpu_table, cpuid, CPUID_AES, CPUID_SMX, CPUID_VMX, fill_processor_name(), get_current_microcode_rev(), and printk.

Referenced by report_platform_info().

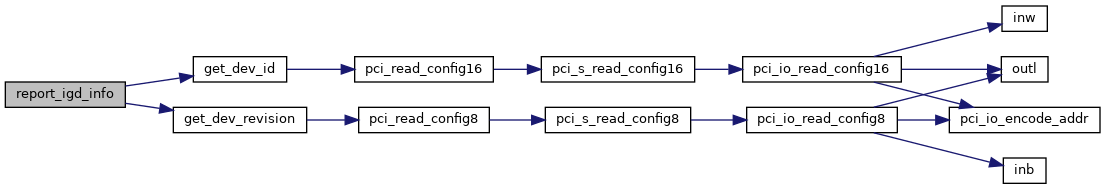

Definition at line 237 of file report_platform.c.

References ARRAY_SIZE, BIOS_DEBUG, get_dev_id(), get_dev_revision(), igd_table, igdid, printk, and SA_DEV_IGD.

Referenced by report_platform_info().

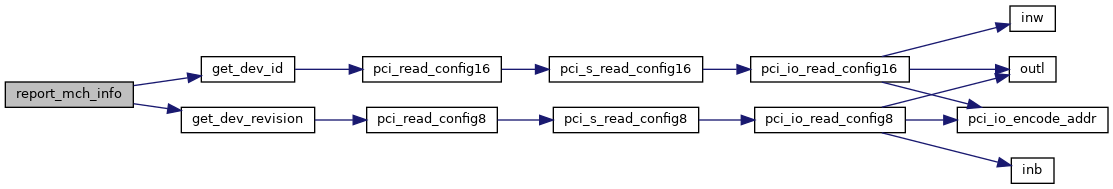

Definition at line 201 of file report_platform.c.

References ARRAY_SIZE, BIOS_DEBUG, get_dev_id(), get_dev_revision(), mch_table, mchid, printk, and SA_DEV_ROOT.

Referenced by report_platform_info().

Definition at line 220 of file report_platform.c.

References ARRAY_SIZE, BIOS_DEBUG, get_dev_id(), get_dev_revision(), lpcid, PCH_DEV_LPC, pch_table, pch_type(), and printk.

Referenced by report_platform_info().

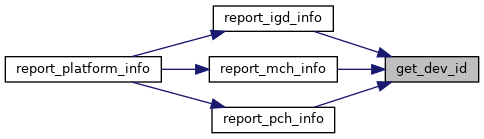

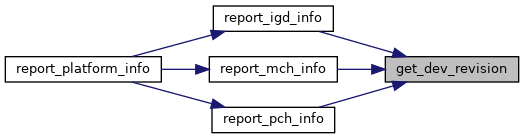

Definition at line 254 of file report_platform.c.

References report_cpu_info(), report_igd_info(), report_mch_info(), and report_pch_info().

| struct { ... } cpu_table[] |

Referenced by report_cpu_info().

| u32 cpuid |

Definition at line 17 of file report_platform.c.

| struct { ... } igd_table[] |

Referenced by report_igd_info().

| u16 igdid |

Definition at line 109 of file report_platform.c.

| u16 lpcid |

Definition at line 78 of file report_platform.c.

| struct { ... } mch_table[] |

Referenced by report_mch_info().

| u16 mchid |

Definition at line 40 of file report_platform.c.

| const char* name |

Definition at line 18 of file report_platform.c.

| struct { ... } pch_table[] |

Referenced by report_pch_info().