|

coreboot

coreboot is an Open Source project aimed at replacing the proprietary BIOS found in most computers.

|

|

coreboot

coreboot is an Open Source project aimed at replacing the proprietary BIOS found in most computers.

|

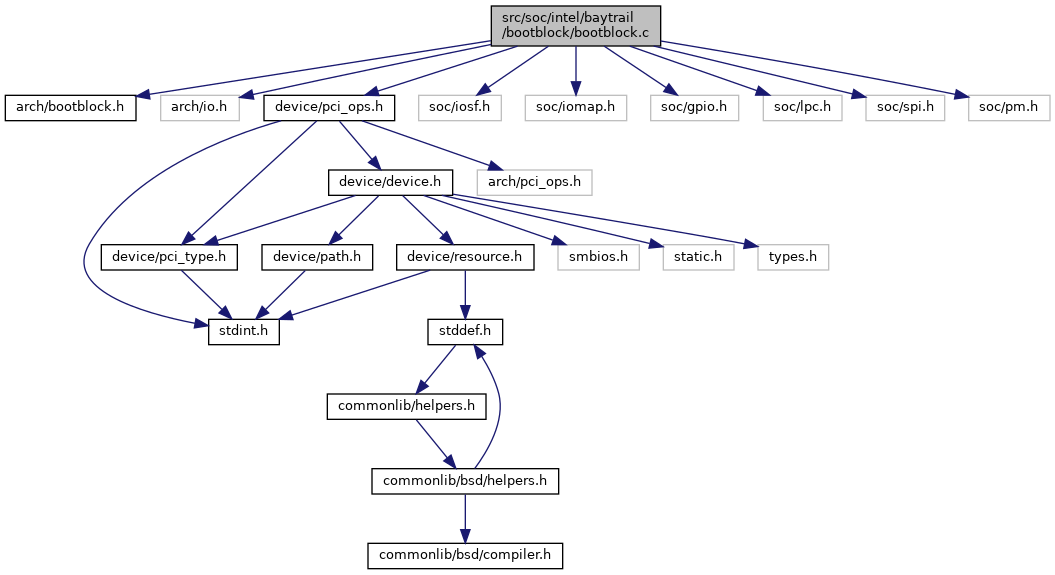

#include <arch/bootblock.h>#include <arch/io.h>#include <device/pci_ops.h>#include <soc/iosf.h>#include <soc/iomap.h>#include <soc/gpio.h>#include <soc/lpc.h>#include <soc/spi.h>#include <soc/pm.h>

Go to the source code of this file.

Functions | |

| static void | program_base_addresses (void) |

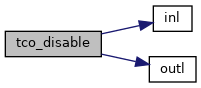

| static void | tco_disable (void) |

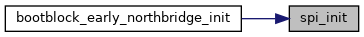

| static void | spi_init (void) |

| static void | byt_config_com1_and_enable (void) |

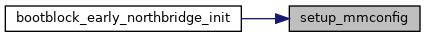

| static void | setup_mmconfig (void) |

| void | bootblock_early_northbridge_init (void) |

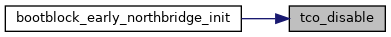

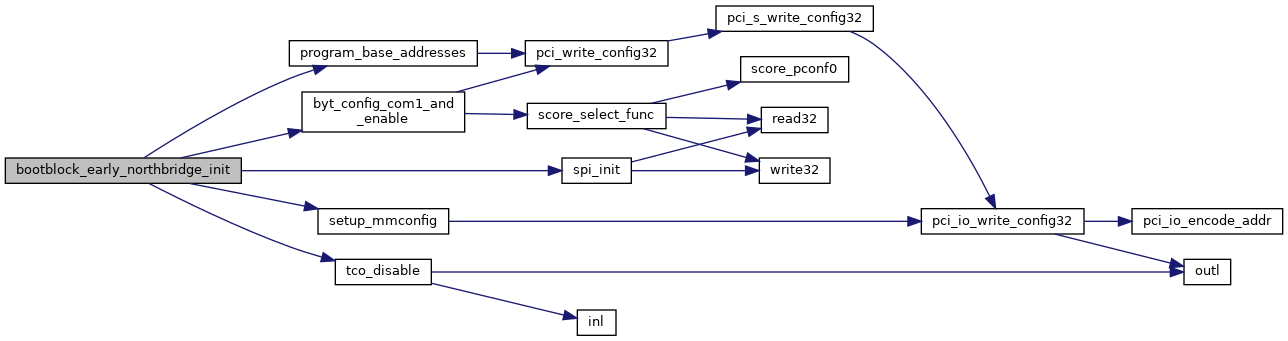

Definition at line 101 of file bootblock.c.

References byt_config_com1_and_enable(), CONFIG, program_base_addresses(), setup_mmconfig(), spi_init(), and tco_disable().

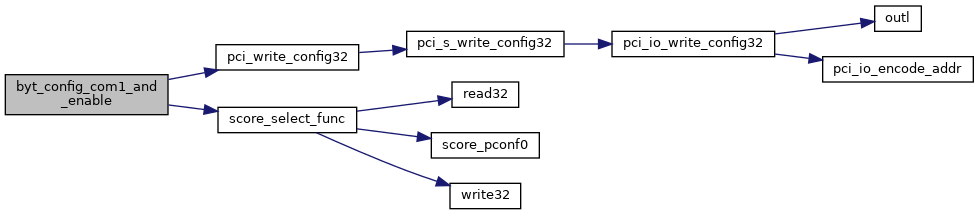

Definition at line 67 of file bootblock.c.

References LPC_DEV, PCI_DEV, pci_write_config32(), score_select_func(), UART_CONT, UART_RXD_PAD, and UART_TXD_PAD.

Referenced by bootblock_early_northbridge_init().

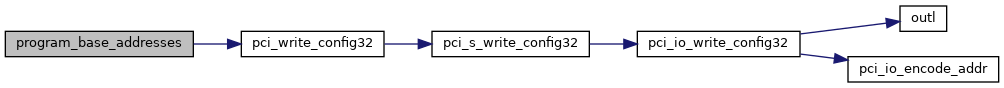

Definition at line 13 of file bootblock.c.

References ABASE, ACPI_BASE_ADDRESS, GBASE, GPIO_BASE_ADDRESS, IBASE, ILB_BASE_ADDRESS, IO_BASE_ADDRESS, IOBASE, LPC_DEV, LPC_FUNC, MPBASE, MPHY_BASE_ADDRESS, PBASE, PCI_DEV, pci_write_config32(), PMC_BASE_ADDRESS, PUBASE, PUNIT_BASE_ADDRESS, RCBA, RCBA_BASE_ADDRESS, SBASE, and SPI_BASE_ADDRESS.

Referenced by bootblock_early_northbridge_init().

Definition at line 80 of file bootblock.c.

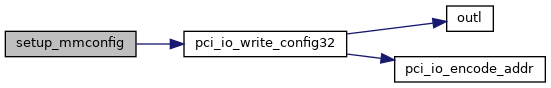

References BUNIT_MMCONF_REG, IOSF_BYTE_EN, IOSF_OP_WRITE_BUNIT, IOSF_OPCODE, IOSF_PCI_DEV, IOSF_PORT, IOSF_PORT_BUNIT, IOSF_REG, MCR_REG, MCRX_REG, MDR_REG, and pci_io_write_config32().

Referenced by bootblock_early_northbridge_init().

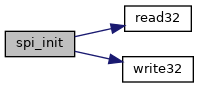

Definition at line 50 of file bootblock.c.

References BCR, BCR_WPD, EISS, read32(), SCS, SMIWPEN, SPI_BASE_ADDRESS, SRC_CACHE_PREFETCH, SRC_MASK, and write32().

Referenced by bootblock_early_northbridge_init().

Definition at line 41 of file bootblock.c.

References ACPI_BASE_ADDRESS, inl(), outl(), TCO1_CNT, and TCO_TMR_HALT.

Referenced by bootblock_early_northbridge_init().