|

coreboot

coreboot is an Open Source project aimed at replacing the proprietary BIOS found in most computers.

|

|

coreboot

coreboot is an Open Source project aimed at replacing the proprietary BIOS found in most computers.

|

Go to the source code of this file.

Functions | |

| void | rtc_read (u16 addr, u16 *rdata) |

| void | rtc_write (u16 addr, u16 wdata) |

| void | rtc_bbpu_power_on (void) |

| int | rtc_init (int recover) |

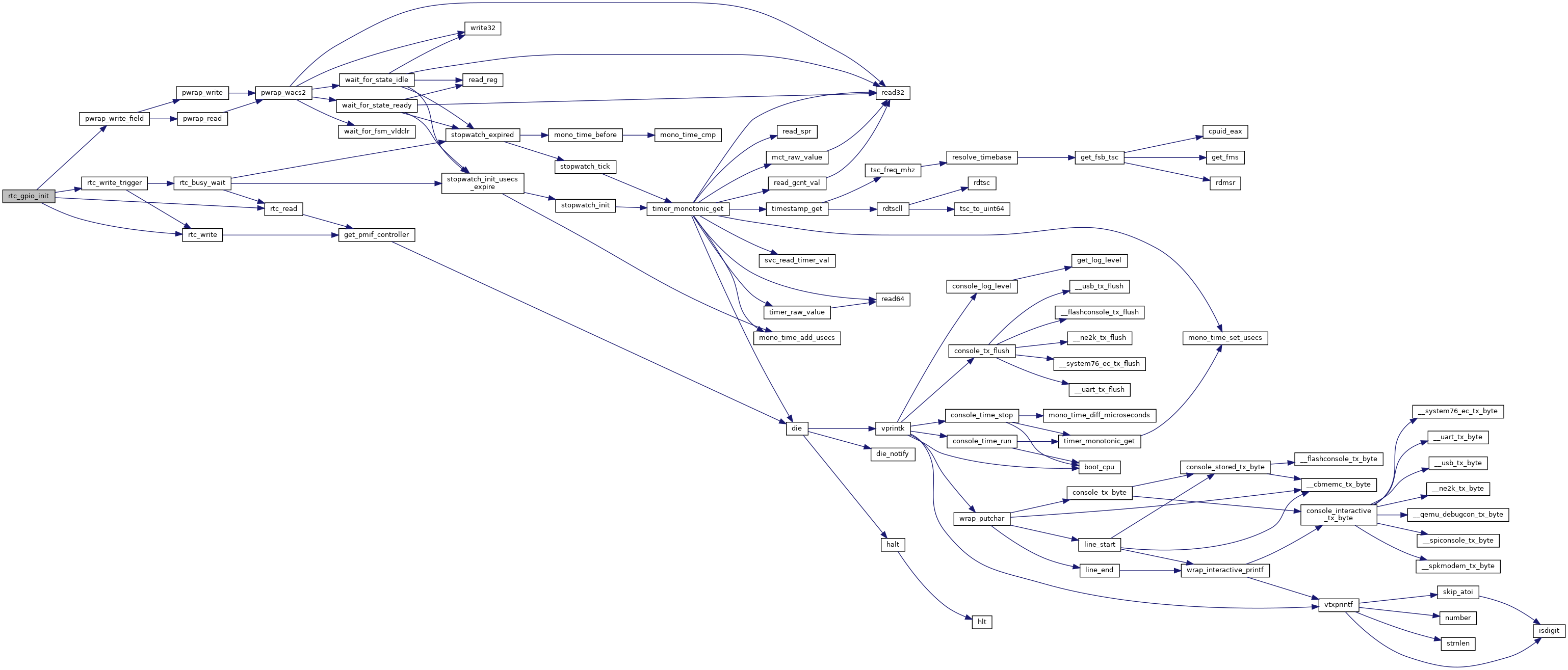

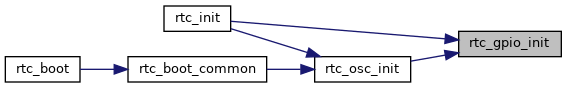

| bool | rtc_gpio_init (void) |

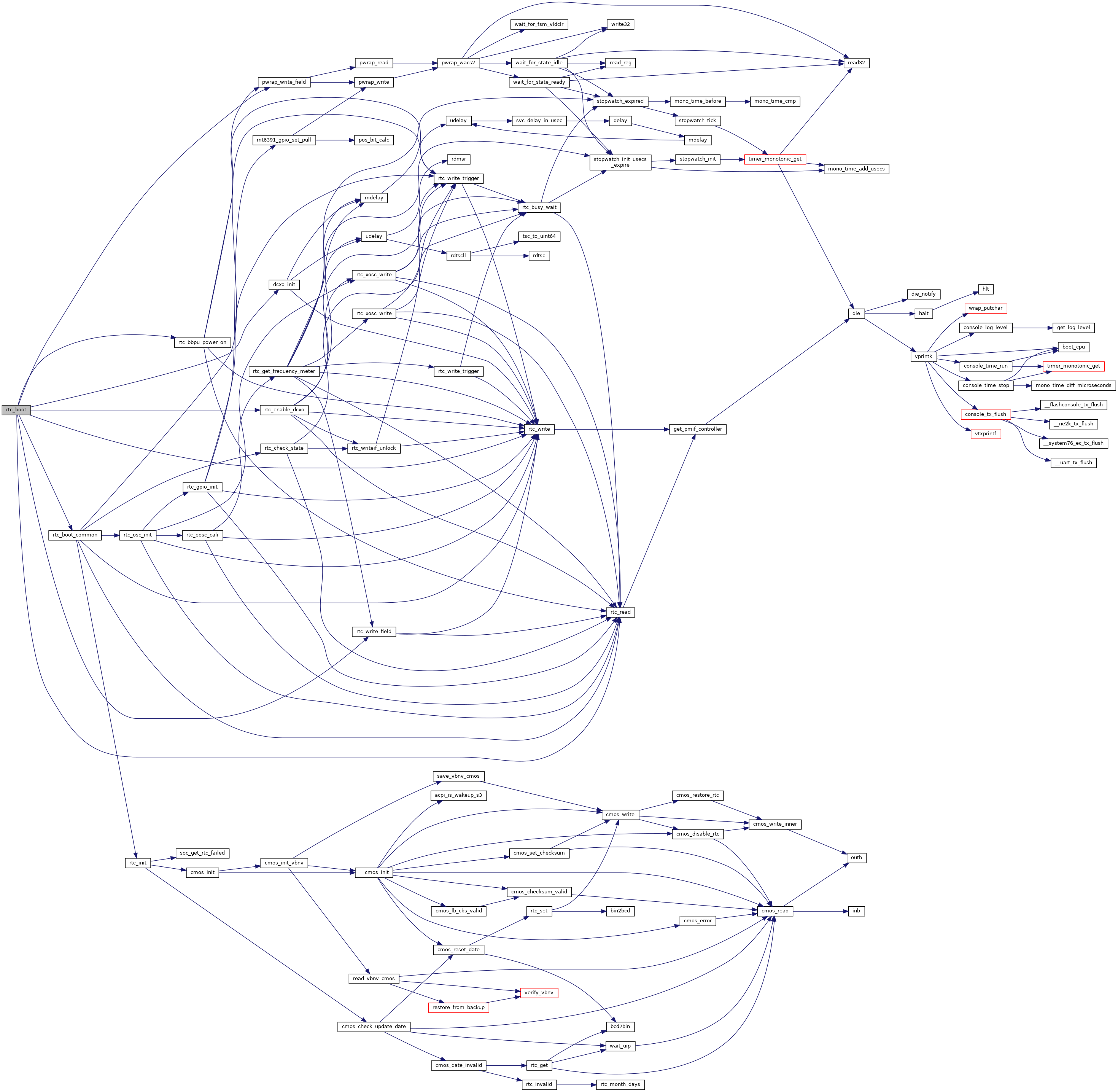

| void | rtc_boot (void) |

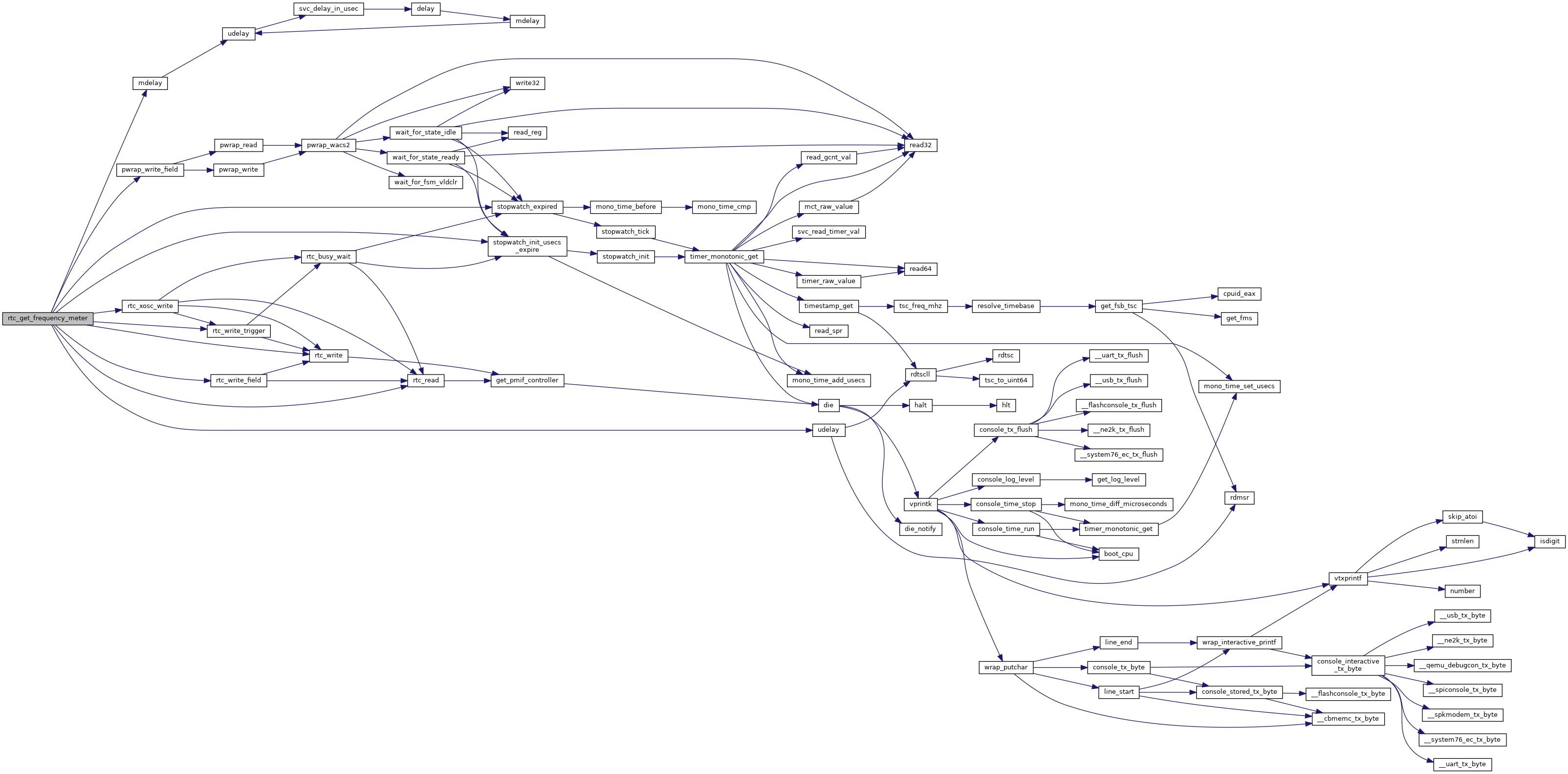

| u16 | rtc_get_frequency_meter (u16 val, u16 measure_src, u16 window_size) |

| anonymous enum |

| anonymous enum |

| anonymous enum |

| anonymous enum |

| anonymous enum |

| anonymous enum |

| anonymous enum |

| anonymous enum |

| anonymous enum |

| anonymous enum |

| anonymous enum |

| anonymous enum |

| anonymous enum |

| anonymous enum |

| anonymous enum |

| anonymous enum |

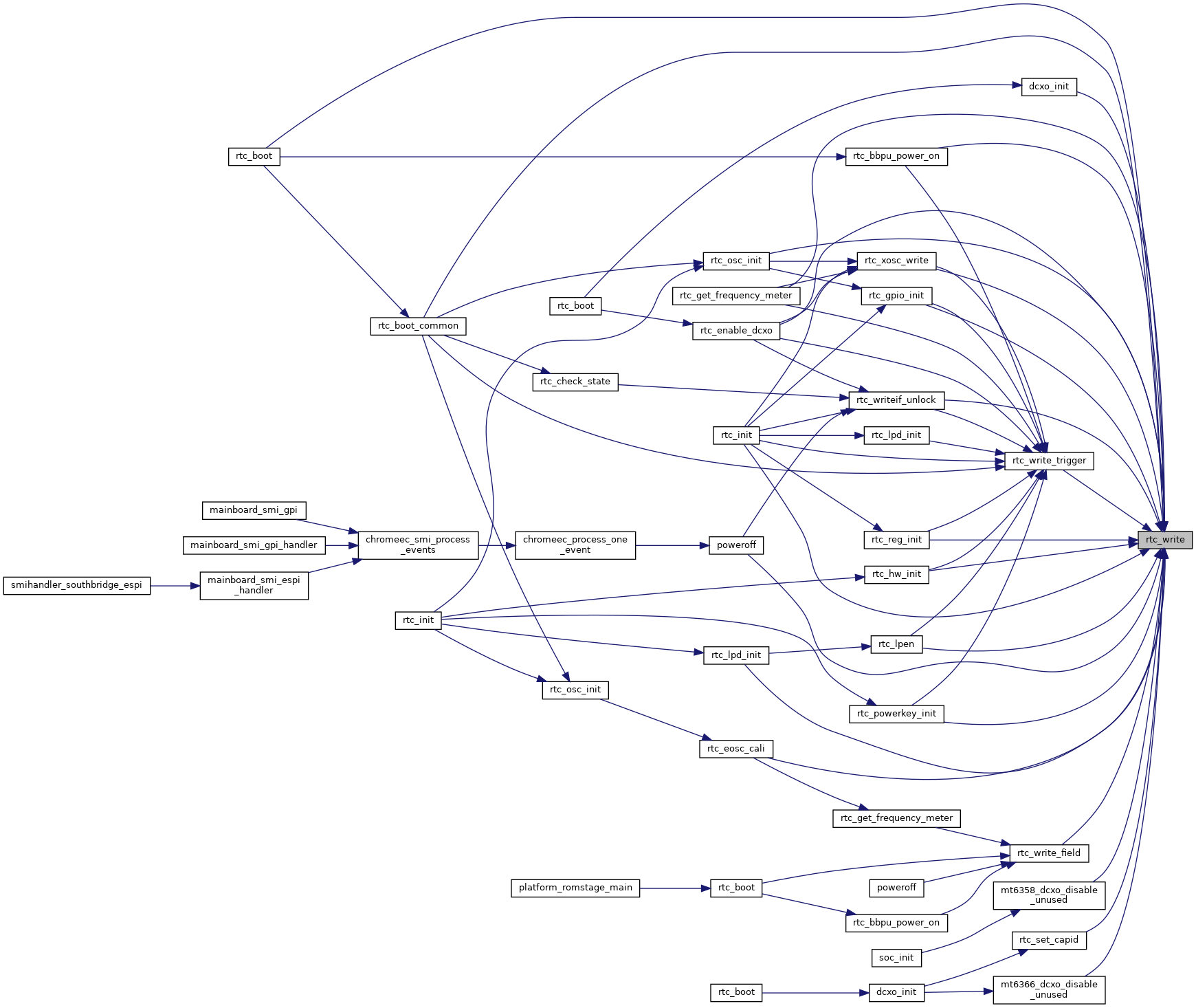

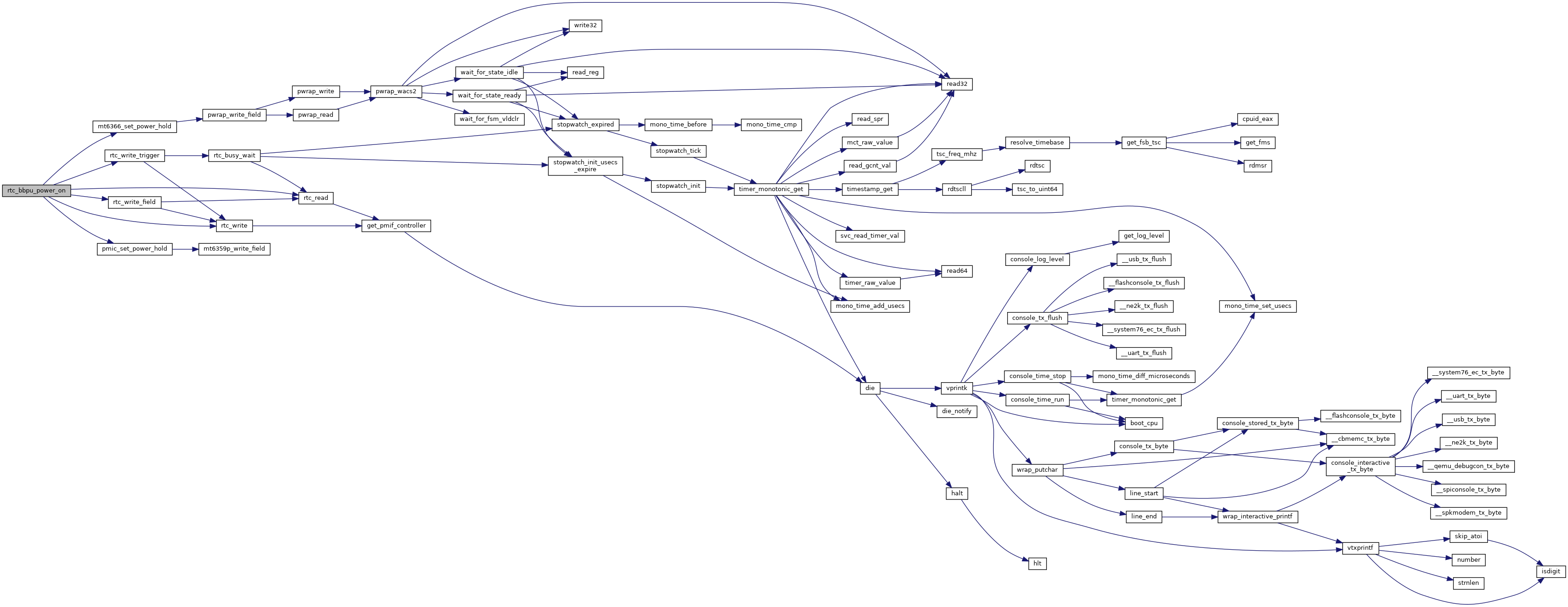

Definition at line 286 of file rtc_mt6359p.c.

References mt6366_set_power_hold(), PMIC_PWRHOLD, pmic_set_power_hold(), RTC_BBPU, RTC_BBPU_AUTO, RTC_BBPU_ENABLE_ALARM, RTC_BBPU_KEY, RTC_BBPU_PWREN, RTC_BBPU_RELOAD, rtc_info, rtc_read(), rtc_write(), rtc_write_field(), and rtc_write_trigger().

Referenced by rtc_boot().

Definition at line 315 of file rtc_mt6359p.c.

References dcxo_init(), PMIC_RG_DCXO_CW02, PMIC_RG_SCK_TOP_CON0, PMIC_RG_TOP_CKPDN, PMIC_RG_TOP_CKPDN2, pwrap_write_field(), rtc_bbpu_power_on(), rtc_boot_common(), rtc_enable_dcxo(), rtc_info, rtc_read(), rtc_write(), and rtc_write_field().

Referenced by platform_romstage_main().

Definition at line 87 of file rtc_mt6359p.c.

References FQMTR_TIMEOUT_US, mdelay(), PMIC_FQMTR_CON0_BUSY, PMIC_FQMTR_CON0_DCXO26M_EN, PMIC_FQMTR_CON0_FQMTR_EN, PMIC_FQMTR_RST_SHIFT, PMIC_RG_BANK_FQMTR_RST, PMIC_RG_BANK_FQMTR_RST_SHIFT, PMIC_RG_FQMTR_32K_CK_PDN_SHIFT, PMIC_RG_FQMTR_CK_PDN_SHIFT, PMIC_RG_FQMTR_CON0, PMIC_RG_FQMTR_DATA, PMIC_RG_FQMTR_DCXO26M_EN_SHIFT, PMIC_RG_FQMTR_RST, PMIC_RG_FQMTR_WINSET, PMIC_RG_TOP_CKPDN_CON0_CLR, PMIC_RG_TOP_CKPDN_CON0_SET, pwrap_write_field(), RTC_BBPU, RTC_BBPU_KEY, RTC_BBPU_RELOAD, rtc_info, RTC_OSC32CON, rtc_read(), rtc_write(), rtc_write_field(), rtc_write_trigger(), rtc_xosc_write(), RTC_XOSCCALI_MASK, stopwatch_expired(), stopwatch_init_usecs_expire(), udelay(), val, and wait_us.

Referenced by rtc_eosc_cali().

Definition at line 71 of file rtc_mt6359p.c.

References PMIC_RG_TOP_CKPDN_CON1_CLR, PMIC_RG_TOP_CKSEL_CON0_SET, pwrap_write_field(), RTC_CON, RTC_CON_EOSC32_LPEN, RTC_CON_F32KOB, RTC_CON_GOE, RTC_CON_GPEN, RTC_CON_GPU, RTC_CON_LPRST, RTC_CON_LPSTA_RAW, RTC_CON_XOSC32_LPEN, rtc_read(), rtc_write(), and rtc_write_trigger().

Referenced by rtc_init(), and rtc_osc_init().

| int rtc_init | ( | int | recover | ) |

Definition at line 219 of file rtc_mt6359p.c.

References mdelay(), PMIC_RG_CHRSTATUS, pwrap_write_field(), RTC_AL_YEA, rtc_gpio_init(), rtc_hw_init(), rtc_info, RTC_K_EOSC_RSV_0, RTC_K_EOSC_RSV_1, RTC_K_EOSC_RSV_2, rtc_lpd_init(), rtc_osc_init(), RTC_POWERKEY1, RTC_POWERKEY1_KEY, RTC_POWERKEY2, RTC_POWERKEY2_KEY, rtc_powerkey_init(), rtc_read(), rtc_reg_init(), RTC_STATUS_GPIO_INIT_FAIL, RTC_STATUS_HW_INIT_FAIL, RTC_STATUS_LPD_INIT_FAIL, RTC_STATUS_OK, RTC_STATUS_OSC_SETTING_FAIL, RTC_STATUS_POWERKEY_INIT_FAIL, RTC_STATUS_REG_INIT_FAIL, RTC_STATUS_WRITEIF_UNLOCK_FAIL, rtc_write(), rtc_write_trigger(), rtc_writeif_unlock(), rtc_xosc_write(), and year.

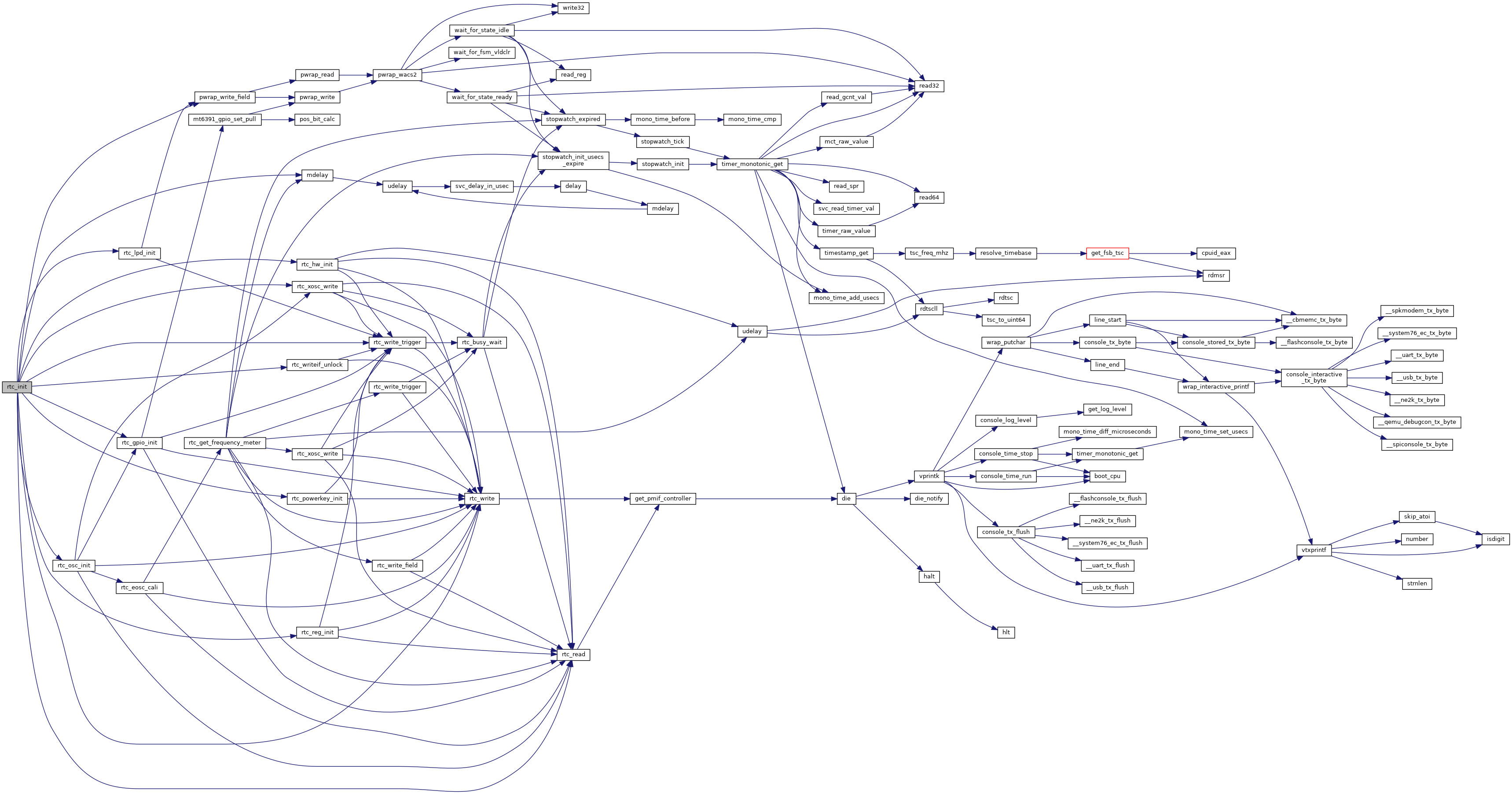

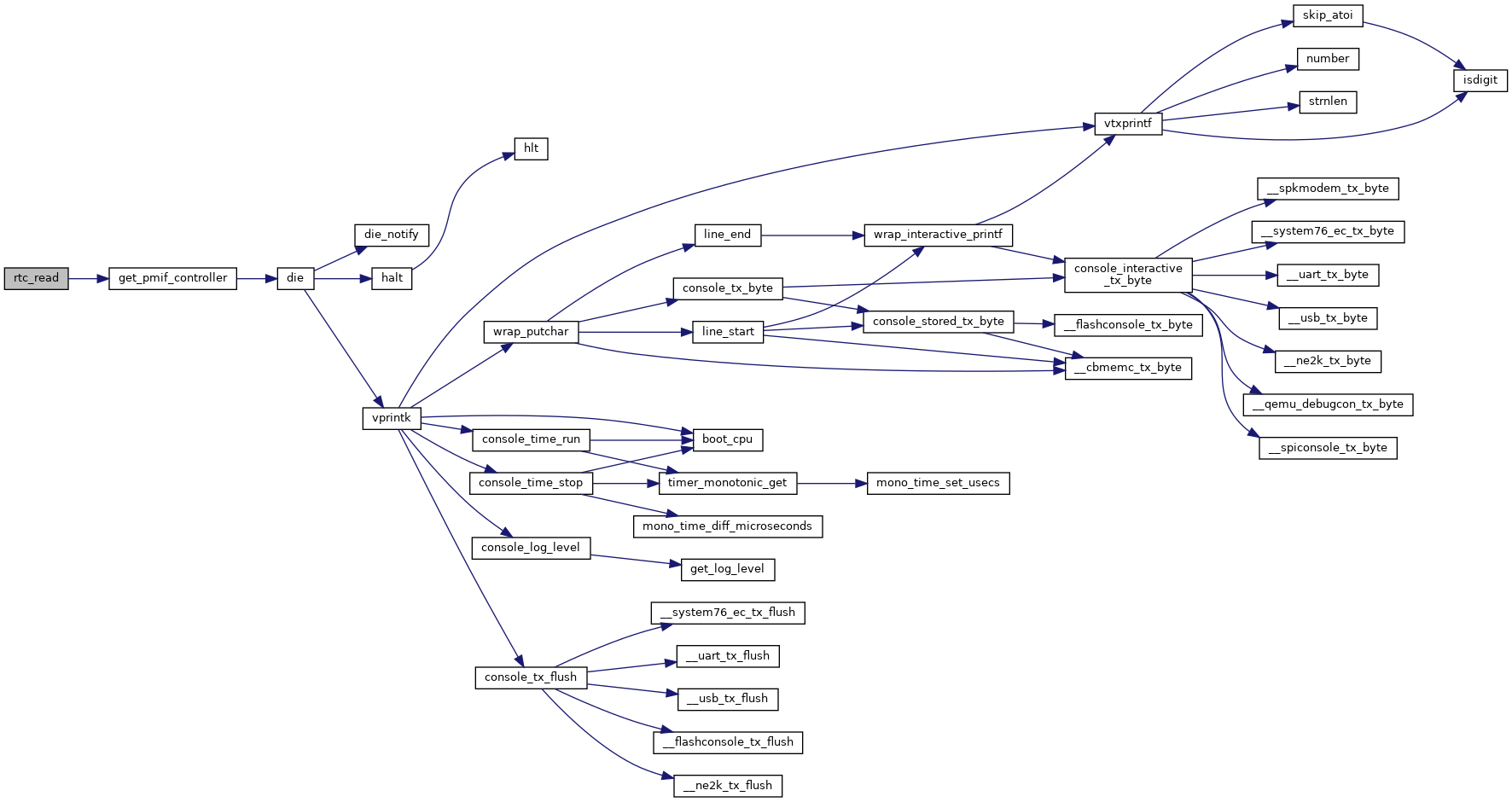

Definition at line 14 of file rtc_mt6359p.c.

References addr, get_pmif_controller(), NULL, pmif_arb, PMIF_SPI, and pmif::read.

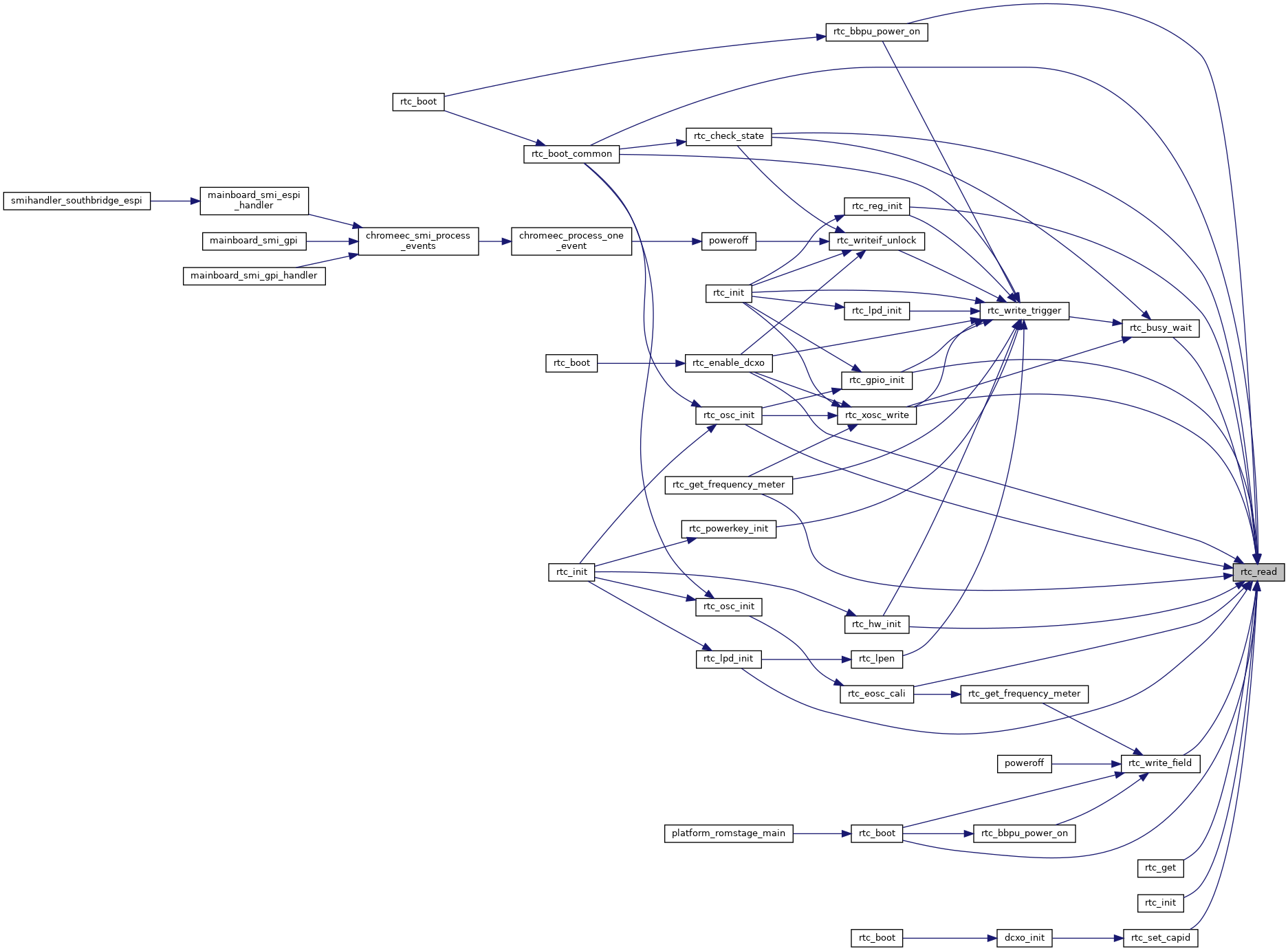

Referenced by rtc_bbpu_power_on(), rtc_boot(), rtc_boot_common(), rtc_busy_wait(), rtc_check_state(), rtc_enable_dcxo(), rtc_eosc_cali(), rtc_get(), rtc_get_frequency_meter(), rtc_gpio_init(), rtc_hw_init(), rtc_init(), rtc_lpd_init(), rtc_osc_init(), rtc_reg_init(), rtc_set_capid(), rtc_write_field(), and rtc_xosc_write().

Definition at line 25 of file rtc_mt6359p.c.

References addr, get_pmif_controller(), NULL, pmif_arb, PMIF_SPI, and pmif::write.

Referenced by dcxo_init(), mt6358_dcxo_disable_unused(), mt6366_dcxo_disable_unused(), poweroff(), rtc_bbpu_power_on(), rtc_boot(), rtc_boot_common(), rtc_enable_dcxo(), rtc_eosc_cali(), rtc_get_frequency_meter(), rtc_gpio_init(), rtc_hw_init(), rtc_init(), rtc_lpd_init(), rtc_lpen(), rtc_osc_init(), rtc_powerkey_init(), rtc_reg_init(), rtc_set_capid(), rtc_write_field(), rtc_write_trigger(), rtc_writeif_unlock(), and rtc_xosc_write().