|

coreboot

coreboot is an Open Source project aimed at replacing the proprietary BIOS found in most computers.

|

|

coreboot

coreboot is an Open Source project aimed at replacing the proprietary BIOS found in most computers.

|

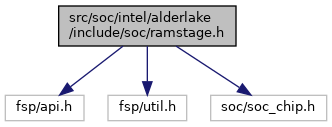

#include <fsp/api.h>#include <fsp/util.h>#include <soc/soc_chip.h>

Go to the source code of this file.

Functions | |

| void | mainboard_silicon_init_params (FSP_S_CONFIG *params) |

| void | mainboard_update_soc_chip_config (struct soc_intel_alderlake_config *config) |

| void | soc_init_pre_device (void *chip_info) |

| void mainboard_silicon_init_params | ( | FSP_S_CONFIG * | params | ) |

Definition at line 8 of file ramstage.c.

| void mainboard_update_soc_chip_config | ( | struct soc_intel_alderlake_config * | config | ) |

Definition at line 34 of file mainboard.c.

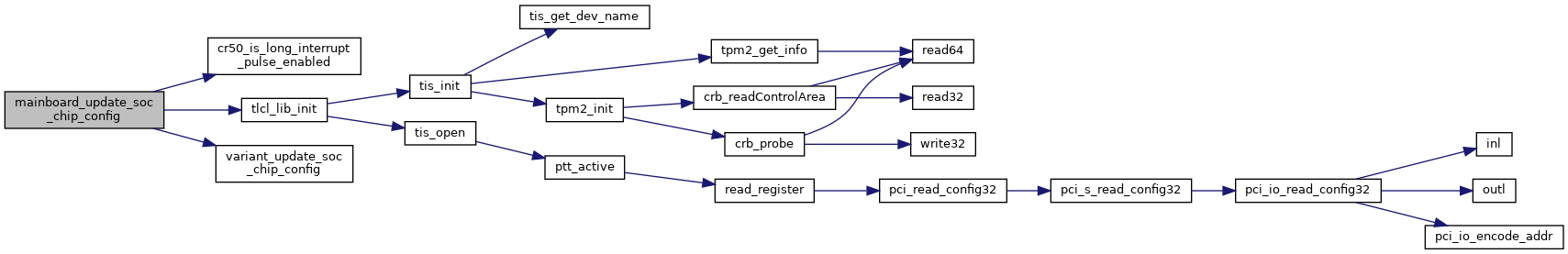

References BIOS_ERR, BIOS_INFO, COMM_0, COMM_1, COMM_2, COMM_3, COMM_4, COMM_5, config, cr50_is_long_interrupt_pulse_enabled(), printk, tlcl_lib_init(), and variant_update_soc_chip_config().

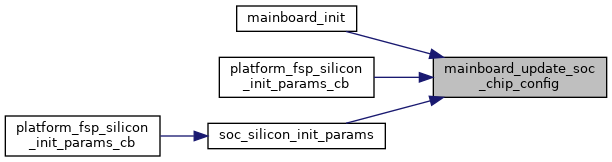

Referenced by mainboard_init(), platform_fsp_silicon_init_params_cb(), and soc_silicon_init_params().