|

coreboot

coreboot is an Open Source project aimed at replacing the proprietary BIOS found in most computers.

|

|

coreboot

coreboot is an Open Source project aimed at replacing the proprietary BIOS found in most computers.

|

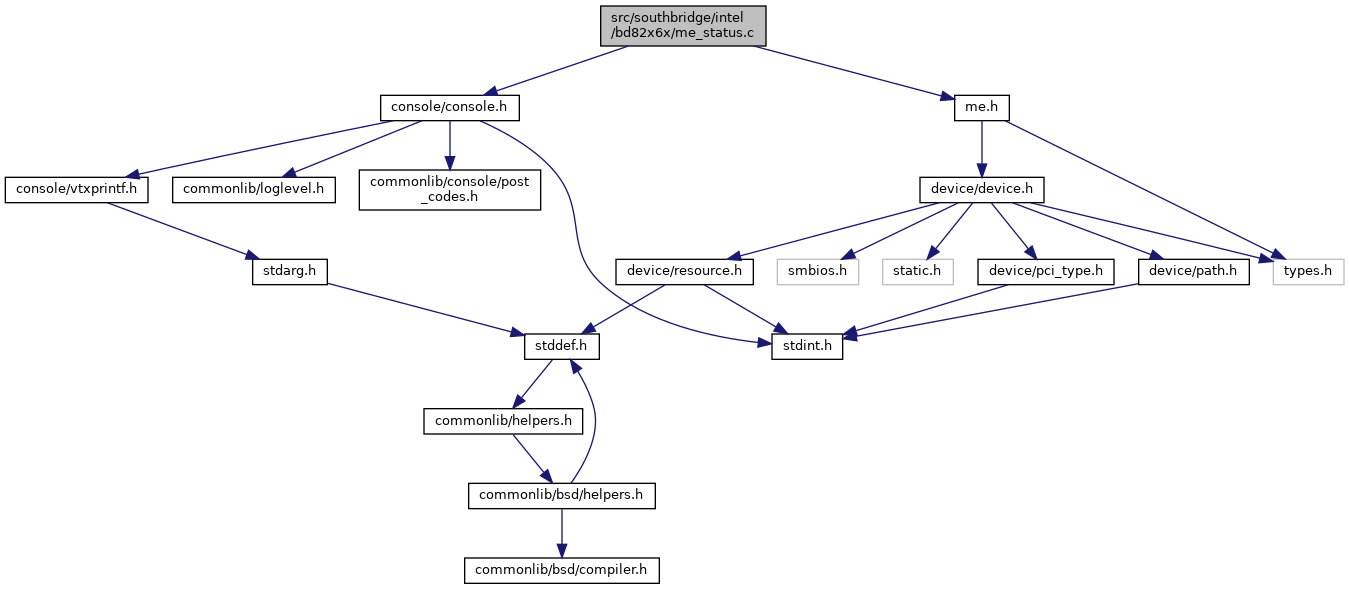

Go to the source code of this file.

Functions | |

| void | intel_me_status (union me_hfs *hfs, union me_gmes *gmes) |

Variables | |

| static const char * | me_cws_values [] |

| static const char * | me_opstate_values [] |

| static const char * | me_opmode_values [] |

| static const char * | me_error_values [] |

| static const char * | me_progress_values [] |

| static const char * | me_pmevent_values [] |

| static const char * | me_progress_rom_values [] |

| static const char * | me_progress_bup_values [] |

| static const char * | me_progress_policy_values [] |

Definition at line 125 of file me_status.c.

References ARRAY_SIZE, BIOS_DEBUG, me_hfs::boot_options_present, me_gmes::current_pmevent, me_gmes::current_state, me_hfs::error_code, me_hfs::fpt_bad, me_hfs::ft_bup_ld_flr, me_hfs::fw_init_complete, me_cws_values, me_error_values, ME_GMES_PHASE_BUP, ME_GMES_PHASE_HOST, ME_GMES_PHASE_POLICY, ME_GMES_PHASE_ROM, me_opmode_values, me_opstate_values, me_pmevent_values, me_progress_bup_values, me_progress_policy_values, me_progress_rom_values, me_progress_values, me_hfs::mfg_mode, me_hfs::operation_mode, me_hfs::operation_state, printk, me_gmes::progress_code, me_hfs::update_in_progress, and me_hfs::working_state.

|

static |

Definition at line 7 of file me_status.c.

Referenced by intel_me_status().

|

static |

Definition at line 37 of file me_status.c.

Referenced by intel_me_status().

|

static |

Definition at line 28 of file me_status.c.

Referenced by intel_me_status().

|

static |

Definition at line 18 of file me_status.c.

Referenced by intel_me_status().

|

static |

Definition at line 56 of file me_status.c.

Referenced by intel_me_status().

|

static |

Definition at line 79 of file me_status.c.

Referenced by intel_me_status().

|

static |

Definition at line 107 of file me_status.c.

Referenced by intel_me_status().

|

static |

Definition at line 73 of file me_status.c.

Referenced by intel_me_status().

|

static |

Definition at line 45 of file me_status.c.

Referenced by intel_me_status().