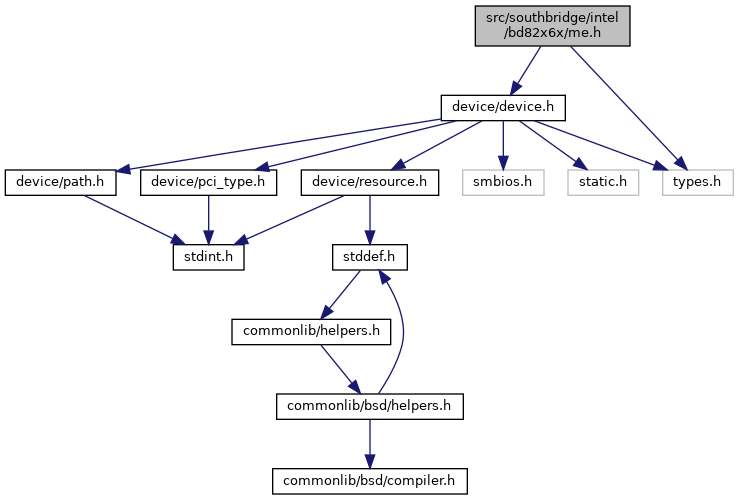

#include <device/device.h>

#include <types.h>

Go to the source code of this file.

|

| enum | me_bios_path {

ME_NORMAL_BIOS_PATH

, ME_S3WAKE_BIOS_PATH

, ME_ERROR_BIOS_PATH

, ME_RECOVERY_BIOS_PATH

,

ME_DISABLE_BIOS_PATH

, ME_FIRMWARE_UPDATE_BIOS_PATH

, ME_NORMAL_BIOS_PATH

, ME_S3WAKE_BIOS_PATH

,

ME_ERROR_BIOS_PATH

, ME_RECOVERY_BIOS_PATH

, ME_DISABLE_BIOS_PATH

, ME_FIRMWARE_UPDATE_BIOS_PATH

,

ME_NORMAL_BIOS_PATH

, ME_S3WAKE_BIOS_PATH

, ME_ERROR_BIOS_PATH

, ME_RECOVERY_BIOS_PATH

,

ME_DISABLE_BIOS_PATH

, ME_FIRMWARE_UPDATE_BIOS_PATH

, ME_NORMAL_BIOS_PATH

, ME_S3WAKE_BIOS_PATH

,

ME_ERROR_BIOS_PATH

, ME_RECOVERY_BIOS_PATH

, ME_DISABLE_BIOS_PATH

, ME_FIRMWARE_UPDATE_BIOS_PATH

} |

| |

◆ CBM_RR_GLOBAL_RESET

| #define CBM_RR_GLOBAL_RESET 0x01 |

Definition at line 237 of file me.h.

◆ CMOS_ME_CHANGED

| #define CMOS_ME_CHANGED |

( |

|

state | ) |

(((state) & 0x2) >> 1) |

Definition at line 197 of file me.h.

◆ CMOS_ME_STATE

Definition at line 196 of file me.h.

◆ CMOS_ME_STATE_CHANGED

| #define CMOS_ME_STATE_CHANGED 2 |

Definition at line 200 of file me.h.

◆ CMOS_ME_STATE_DISABLED

| #define CMOS_ME_STATE_DISABLED 1 |

Definition at line 199 of file me.h.

◆ CMOS_ME_STATE_NORMAL

| #define CMOS_ME_STATE_NORMAL 0 |

Definition at line 198 of file me.h.

◆ GLOBAL_RESET_BIOS_MRC

| #define GLOBAL_RESET_BIOS_MRC 0x01 |

Definition at line 239 of file me.h.

◆ GLOBAL_RESET_BIOS_POST

| #define GLOBAL_RESET_BIOS_POST 0x02 |

Definition at line 240 of file me.h.

◆ GLOBAL_RESET_MEBX

| #define GLOBAL_RESET_MEBX 0x03 |

Definition at line 241 of file me.h.

◆ HECI_EOP_PERFORM_GLOBAL_RESET

| #define HECI_EOP_PERFORM_GLOBAL_RESET 0x1 |

Definition at line 235 of file me.h.

◆ HECI_EOP_STATUS_SUCCESS

| #define HECI_EOP_STATUS_SUCCESS 0x0 |

Definition at line 234 of file me.h.

◆ ME_DELAY

| #define ME_DELAY 10 /* 10 us */ |

Definition at line 10 of file me.h.

◆ ME_ENABLE_TIMEOUT

| #define ME_ENABLE_TIMEOUT 20000 |

Definition at line 202 of file me.h.

◆ ME_GMES_PHASE_BUP

| #define ME_GMES_PHASE_BUP 1 |

Definition at line 103 of file me.h.

◆ ME_GMES_PHASE_HOST

| #define ME_GMES_PHASE_HOST 6 |

Definition at line 108 of file me.h.

◆ ME_GMES_PHASE_MODULE

| #define ME_GMES_PHASE_MODULE 4 |

Definition at line 106 of file me.h.

◆ ME_GMES_PHASE_POLICY

| #define ME_GMES_PHASE_POLICY 3 |

Definition at line 105 of file me.h.

◆ ME_GMES_PHASE_ROM

| #define ME_GMES_PHASE_ROM 0 |

Definition at line 102 of file me.h.

◆ ME_GMES_PHASE_UKERNEL

| #define ME_GMES_PHASE_UKERNEL 2 |

Definition at line 104 of file me.h.

◆ ME_GMES_PHASE_UNKNOWN

| #define ME_GMES_PHASE_UNKNOWN 5 |

Definition at line 107 of file me.h.

◆ ME_HFS_ACK_CONTINUE

| #define ME_HFS_ACK_CONTINUE 7 |

Definition at line 51 of file me.h.

◆ ME_HFS_ACK_GBL_RESET

| #define ME_HFS_ACK_GBL_RESET 6 |

Definition at line 50 of file me.h.

◆ ME_HFS_ACK_NO_DID

| #define ME_HFS_ACK_NO_DID 0 |

Definition at line 44 of file me.h.

◆ ME_HFS_ACK_PWR_CYCLE

| #define ME_HFS_ACK_PWR_CYCLE 2 |

Definition at line 46 of file me.h.

◆ ME_HFS_ACK_RESET

| #define ME_HFS_ACK_RESET 1 |

Definition at line 45 of file me.h.

◆ ME_HFS_ACK_S3

Definition at line 47 of file me.h.

◆ ME_HFS_ACK_S4

Definition at line 48 of file me.h.

◆ ME_HFS_ACK_S5

Definition at line 49 of file me.h.

◆ ME_HFS_BIOS_DRAM_ACK

| #define ME_HFS_BIOS_DRAM_ACK 1 |

Definition at line 43 of file me.h.

◆ ME_HFS_CWS_INIT

| #define ME_HFS_CWS_INIT 1 |

Definition at line 22 of file me.h.

◆ ME_HFS_CWS_INVALID

| #define ME_HFS_CWS_INVALID 8 |

Definition at line 27 of file me.h.

◆ ME_HFS_CWS_NORMAL

| #define ME_HFS_CWS_NORMAL 5 |

Definition at line 24 of file me.h.

◆ ME_HFS_CWS_REC

Definition at line 23 of file me.h.

◆ ME_HFS_CWS_RESET

| #define ME_HFS_CWS_RESET 0 |

Definition at line 21 of file me.h.

◆ ME_HFS_CWS_TRANS

| #define ME_HFS_CWS_TRANS 7 |

Definition at line 26 of file me.h.

◆ ME_HFS_CWS_WAIT

| #define ME_HFS_CWS_WAIT 6 |

Definition at line 25 of file me.h.

◆ ME_HFS_ERROR_DEBUG

| #define ME_HFS_ERROR_DEBUG 4 |

Definition at line 37 of file me.h.

◆ ME_HFS_ERROR_IMAGE

| #define ME_HFS_ERROR_IMAGE 3 |

Definition at line 36 of file me.h.

◆ ME_HFS_ERROR_NONE

| #define ME_HFS_ERROR_NONE 0 |

Definition at line 34 of file me.h.

◆ ME_HFS_ERROR_UNCAT

| #define ME_HFS_ERROR_UNCAT 1 |

Definition at line 35 of file me.h.

◆ ME_HFS_MODE_DEBUG

| #define ME_HFS_MODE_DEBUG 2 |

Definition at line 39 of file me.h.

◆ ME_HFS_MODE_DIS

| #define ME_HFS_MODE_DIS 3 |

Definition at line 40 of file me.h.

◆ ME_HFS_MODE_NORMAL

| #define ME_HFS_MODE_NORMAL 0 |

Definition at line 38 of file me.h.

◆ ME_HFS_MODE_OVER_JMPR

| #define ME_HFS_MODE_OVER_JMPR 4 |

Definition at line 41 of file me.h.

◆ ME_HFS_MODE_OVER_MEI

| #define ME_HFS_MODE_OVER_MEI 5 |

Definition at line 42 of file me.h.

◆ ME_HFS_STATE_BRINGUP

| #define ME_HFS_STATE_BRINGUP 6 |

Definition at line 32 of file me.h.

◆ ME_HFS_STATE_ERROR

| #define ME_HFS_STATE_ERROR 7 |

Definition at line 33 of file me.h.

◆ ME_HFS_STATE_M0

| #define ME_HFS_STATE_M0 5 |

Definition at line 31 of file me.h.

◆ ME_HFS_STATE_M0_UMA

| #define ME_HFS_STATE_M0_UMA 1 |

Definition at line 29 of file me.h.

◆ ME_HFS_STATE_M3

| #define ME_HFS_STATE_M3 4 |

Definition at line 30 of file me.h.

◆ ME_HFS_STATE_PREBOOT

| #define ME_HFS_STATE_PREBOOT 0 |

Definition at line 28 of file me.h.

◆ ME_INIT_DONE

Definition at line 86 of file me.h.

◆ ME_INIT_STATUS_ERROR

| #define ME_INIT_STATUS_ERROR 2 |

Definition at line 89 of file me.h.

◆ ME_INIT_STATUS_NOMEM

| #define ME_INIT_STATUS_NOMEM 1 |

Definition at line 88 of file me.h.

◆ ME_INIT_STATUS_SUCCESS

| #define ME_INIT_STATUS_SUCCESS 0 |

Definition at line 87 of file me.h.

◆ ME_RETRY

| #define ME_RETRY 100000 /* 1 second */ |

Definition at line 9 of file me.h.

◆ MEI_ADDRESS_AMT

| #define MEI_ADDRESS_AMT 0x02 |

Definition at line 167 of file me.h.

◆ MEI_ADDRESS_CORE

| #define MEI_ADDRESS_CORE 0x01 |

Definition at line 166 of file me.h.

◆ MEI_ADDRESS_ICC

| #define MEI_ADDRESS_ICC 0x08 |

Definition at line 171 of file me.h.

◆ MEI_ADDRESS_MKHI

| #define MEI_ADDRESS_MKHI 0x07 |

Definition at line 170 of file me.h.

◆ MEI_ADDRESS_RESERVED

| #define MEI_ADDRESS_RESERVED 0x03 |

Definition at line 168 of file me.h.

◆ MEI_ADDRESS_THERMAL

| #define MEI_ADDRESS_THERMAL 0x09 |

Definition at line 172 of file me.h.

◆ MEI_ADDRESS_WDT

| #define MEI_ADDRESS_WDT 0x04 |

Definition at line 169 of file me.h.

◆ MEI_H_CB_WW

Definition at line 149 of file me.h.

◆ MEI_H_CSR

Definition at line 150 of file me.h.

◆ MEI_HOST_ADDRESS

| #define MEI_HOST_ADDRESS 0 |

Definition at line 174 of file me.h.

◆ MEI_ME_CB_RW

| #define MEI_ME_CB_RW 0x08 |

Definition at line 151 of file me.h.

◆ MEI_ME_CSR_HA

| #define MEI_ME_CSR_HA 0x0c |

Definition at line 152 of file me.h.

◆ MKHI_DISABLE_RULE_ID

| #define MKHI_DISABLE_RULE_ID 0x06 |

Definition at line 194 of file me.h.

◆ MKHI_END_OF_POST

| #define MKHI_END_OF_POST 0x0c |

Definition at line 212 of file me.h.

◆ MKHI_FEATURE_OVERRIDE

| #define MKHI_FEATURE_OVERRIDE 0x14 |

Definition at line 213 of file me.h.

◆ MKHI_FWCAPS_GET_RULE

| #define MKHI_FWCAPS_GET_RULE 0x02 |

Definition at line 191 of file me.h.

◆ MKHI_FWCAPS_SET_RULE

| #define MKHI_FWCAPS_SET_RULE 0x03 |

Definition at line 192 of file me.h.

◆ MKHI_GET_FW_VERSION

| #define MKHI_GET_FW_VERSION 0x02 |

Definition at line 211 of file me.h.

◆ MKHI_GLOBAL_RESET

| #define MKHI_GLOBAL_RESET 0x0b |

Definition at line 189 of file me.h.

◆ MKHI_GROUP_ID_CBM

| #define MKHI_GROUP_ID_CBM 0x00 |

Definition at line 184 of file me.h.

◆ MKHI_GROUP_ID_FWCAPS

| #define MKHI_GROUP_ID_FWCAPS 0x03 |

Definition at line 185 of file me.h.

◆ MKHI_GROUP_ID_GEN

| #define MKHI_GROUP_ID_GEN 0xff |

Definition at line 187 of file me.h.

◆ MKHI_GROUP_ID_MDES

| #define MKHI_GROUP_ID_MDES 0x08 |

Definition at line 186 of file me.h.

◆ MKHI_MDES_ENABLE

| #define MKHI_MDES_ENABLE 0x09 |

Definition at line 209 of file me.h.

◆ PCI_CPU_DEVICE

| #define PCI_CPU_DEVICE PCI_DEV(0,0,0) |

Definition at line 16 of file me.h.

◆ PCI_CPU_MEBASE_H

| #define PCI_CPU_MEBASE_H 0x74 /* Set by MRC */ |

Definition at line 18 of file me.h.

◆ PCI_CPU_MEBASE_L

| #define PCI_CPU_MEBASE_L 0x70 /* Set by MRC */ |

Definition at line 17 of file me.h.

◆ PCI_ME_EXT_SHA1

| #define PCI_ME_EXT_SHA1 0x00 |

Definition at line 131 of file me.h.

◆ PCI_ME_EXT_SHA256

| #define PCI_ME_EXT_SHA256 0x02 |

Definition at line 132 of file me.h.

◆ PCI_ME_GMES

Definition at line 101 of file me.h.

◆ PCI_ME_H_GS

Definition at line 85 of file me.h.

◆ PCI_ME_HER

| #define PCI_ME_HER |

( |

|

x | ) |

(0xc0+(4*(x))) |

Definition at line 133 of file me.h.

◆ PCI_ME_HERES

| #define PCI_ME_HERES 0xbc |

Definition at line 130 of file me.h.

◆ PCI_ME_HFS

Definition at line 20 of file me.h.

◆ PCI_ME_UMA

Definition at line 72 of file me.h.

◆ me_bios_path

| Enumerator |

|---|

| ME_NORMAL_BIOS_PATH | |

| ME_S3WAKE_BIOS_PATH | |

| ME_ERROR_BIOS_PATH | |

| ME_RECOVERY_BIOS_PATH | |

| ME_DISABLE_BIOS_PATH | |

| ME_FIRMWARE_UPDATE_BIOS_PATH | |

| ME_NORMAL_BIOS_PATH | |

| ME_S3WAKE_BIOS_PATH | |

| ME_ERROR_BIOS_PATH | |

| ME_RECOVERY_BIOS_PATH | |

| ME_DISABLE_BIOS_PATH | |

| ME_FIRMWARE_UPDATE_BIOS_PATH | |

| ME_NORMAL_BIOS_PATH | |

| ME_S3WAKE_BIOS_PATH | |

| ME_ERROR_BIOS_PATH | |

| ME_RECOVERY_BIOS_PATH | |

| ME_DISABLE_BIOS_PATH | |

| ME_FIRMWARE_UPDATE_BIOS_PATH | |

| ME_NORMAL_BIOS_PATH | |

| ME_S3WAKE_BIOS_PATH | |

| ME_ERROR_BIOS_PATH | |

| ME_RECOVERY_BIOS_PATH | |

| ME_DISABLE_BIOS_PATH | |

| ME_FIRMWARE_UPDATE_BIOS_PATH | |

Definition at line 248 of file me.h.

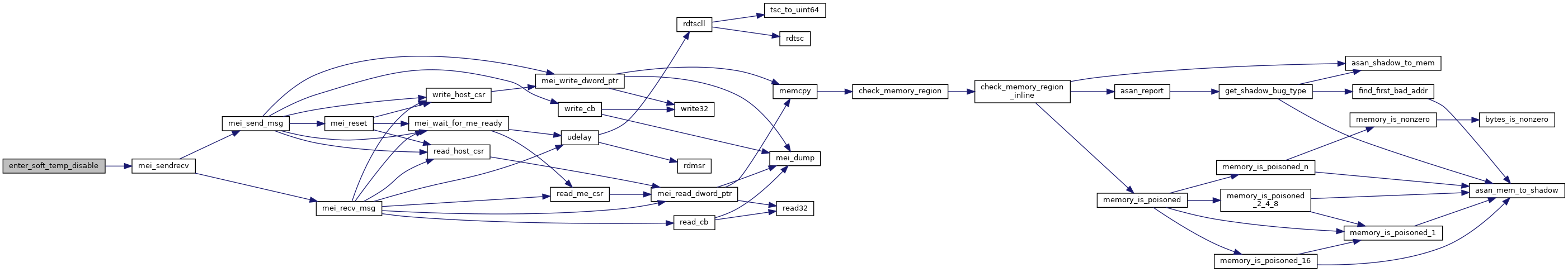

◆ enter_soft_temp_disable()

Definition at line 411 of file me_common.c.

References BIOS_WARNING, mkhi_header::group_id, mei_header::is_complete, MEI_ADDRESS_MKHI, MEI_HOST_ADDRESS, mei_sendrecv(), MKHI_DISABLE_RULE_ID, MKHI_FWCAPS_SET_RULE, MKHI_GROUP_ID_FWCAPS, printk, and me_disable::rule_id.

◆ enter_soft_temp_disable_wait()

| void enter_soft_temp_disable_wait |

( |

void |

| ) |

|

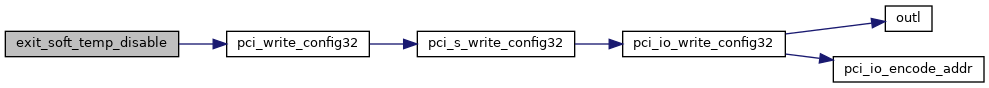

◆ exit_soft_temp_disable()

| void exit_soft_temp_disable |

( |

struct device * |

dev | ) |

|

◆ exit_soft_temp_disable_wait()

| void exit_soft_temp_disable_wait |

( |

struct device * |

dev | ) |

|

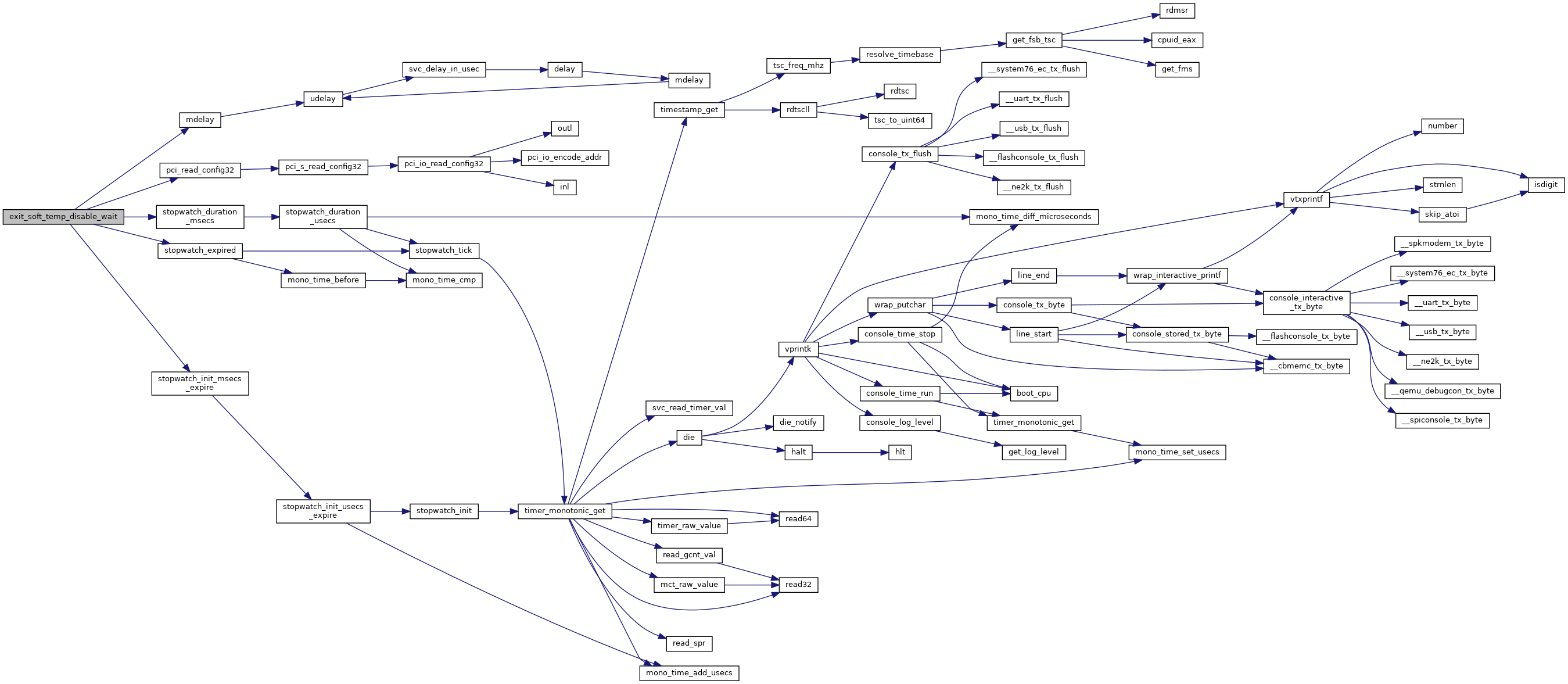

Wait for fw_init_complete. Check every 50 ms, give up after 20 sec. This is what vendor BIOS does. Usually it takes 1.5 seconds or so.

Definition at line 460 of file me_common.c.

References BIOS_ERR, BIOS_NOTICE, me_hfs::fw_init_complete, mdelay(), ME_ENABLE_TIMEOUT, PCI_ME_HFS, pci_read_config32(), printk, me_hfs::raw, stopwatch_duration_msecs(), stopwatch_expired(), and stopwatch_init_msecs_expire().

◆ intel_early_me_init()

| int intel_early_me_init |

( |

void |

| ) |

|

◆ intel_early_me_init_done()

| int intel_early_me_init_done |

( |

u8 |

status | ) |

|

◆ intel_early_me_status()

◆ intel_early_me_uma_size()

| int intel_early_me_uma_size |

( |

void |

| ) |

|

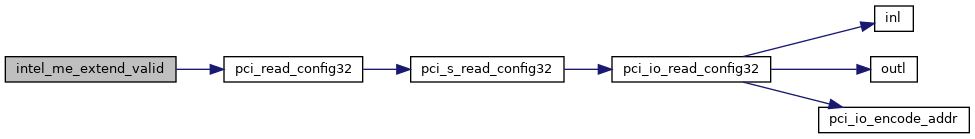

◆ intel_me_extend_valid()

| int intel_me_extend_valid |

( |

struct device * |

dev | ) |

|

Definition at line 359 of file me_common.c.

References BIOS_DEBUG, BIOS_ERR, CONFIG, count, me_heres::extend_feature_present, me_heres::extend_reg_algorithm, me_heres::extend_reg_valid, PCI_ME_EXT_SHA1, PCI_ME_EXT_SHA256, PCI_ME_HER, PCI_ME_HERES, pci_read_config32(), printk, and me_heres::raw.

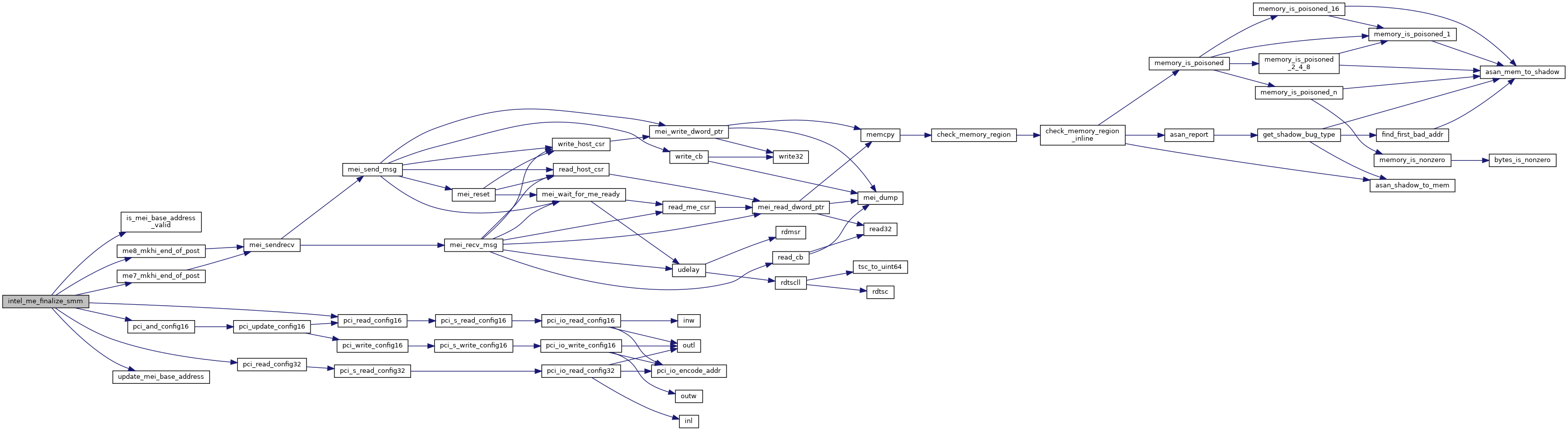

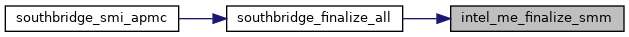

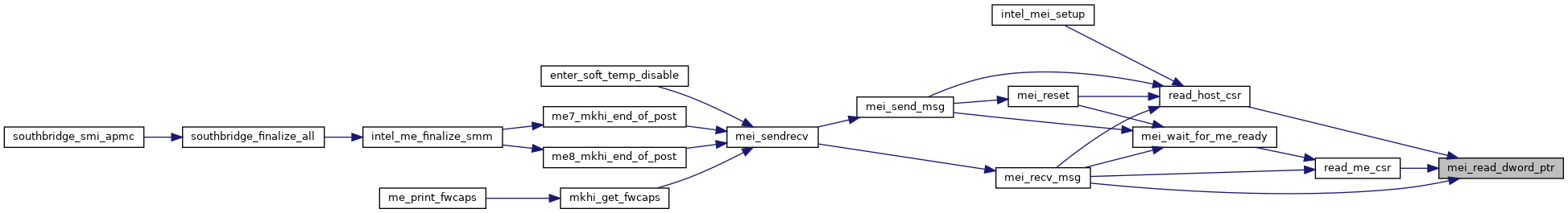

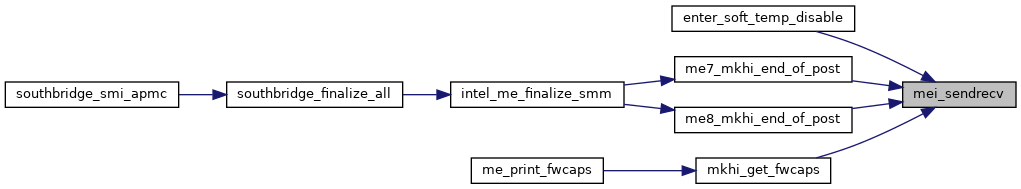

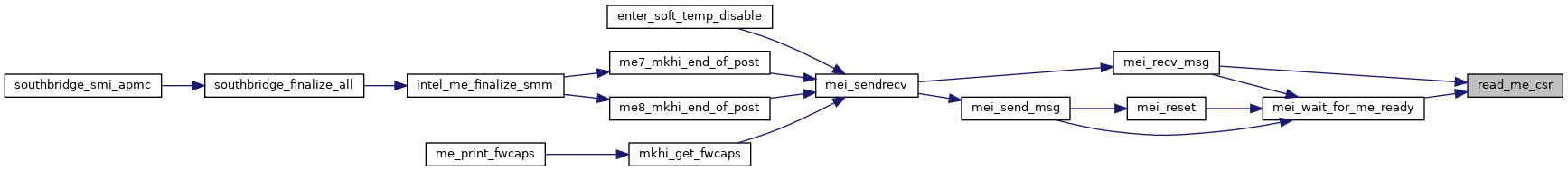

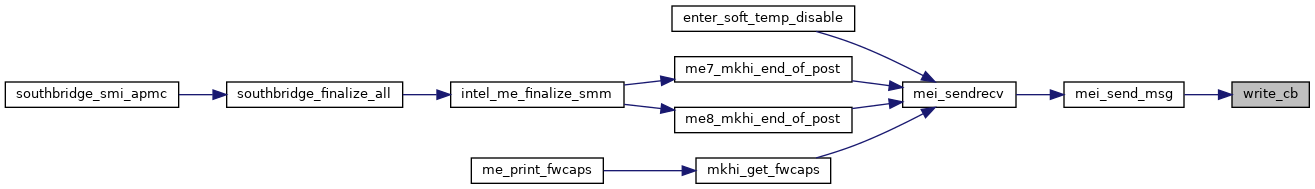

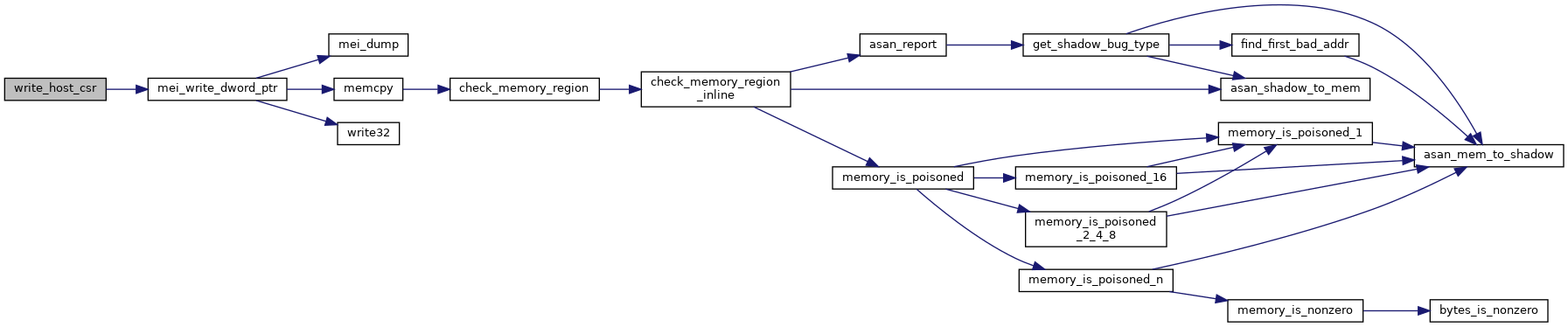

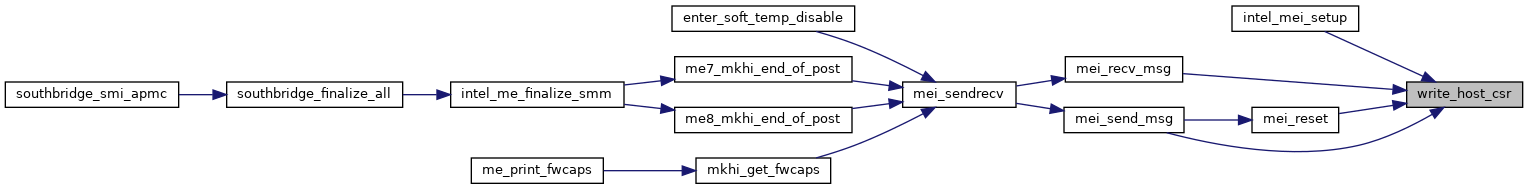

◆ intel_me_finalize_smm()

Definition at line 64 of file me_smm.c.

References BIOS_ERR, did, FD2, me_hfs::fpt_bad, is_mei_base_address_valid(), me7_mkhi_end_of_post(), me8_mkhi_end_of_post(), ME_HFS_CWS_NORMAL, ME_HFS_MODE_NORMAL, me_hfs::operation_mode, PCH_DISABLE_MEI1, PCH_ME_DEV, pci_and_config16(), PCI_COMMAND, PCI_COMMAND_IO, PCI_COMMAND_MASTER, PCI_COMMAND_MEMORY, PCI_DEVICE_ID, PCI_ME_HFS, pci_read_config16(), pci_read_config32(), printk, me_hfs::raw, RCBA32_OR, update_mei_base_address(), and me_hfs::working_state.

Referenced by southbridge_finalize_all().

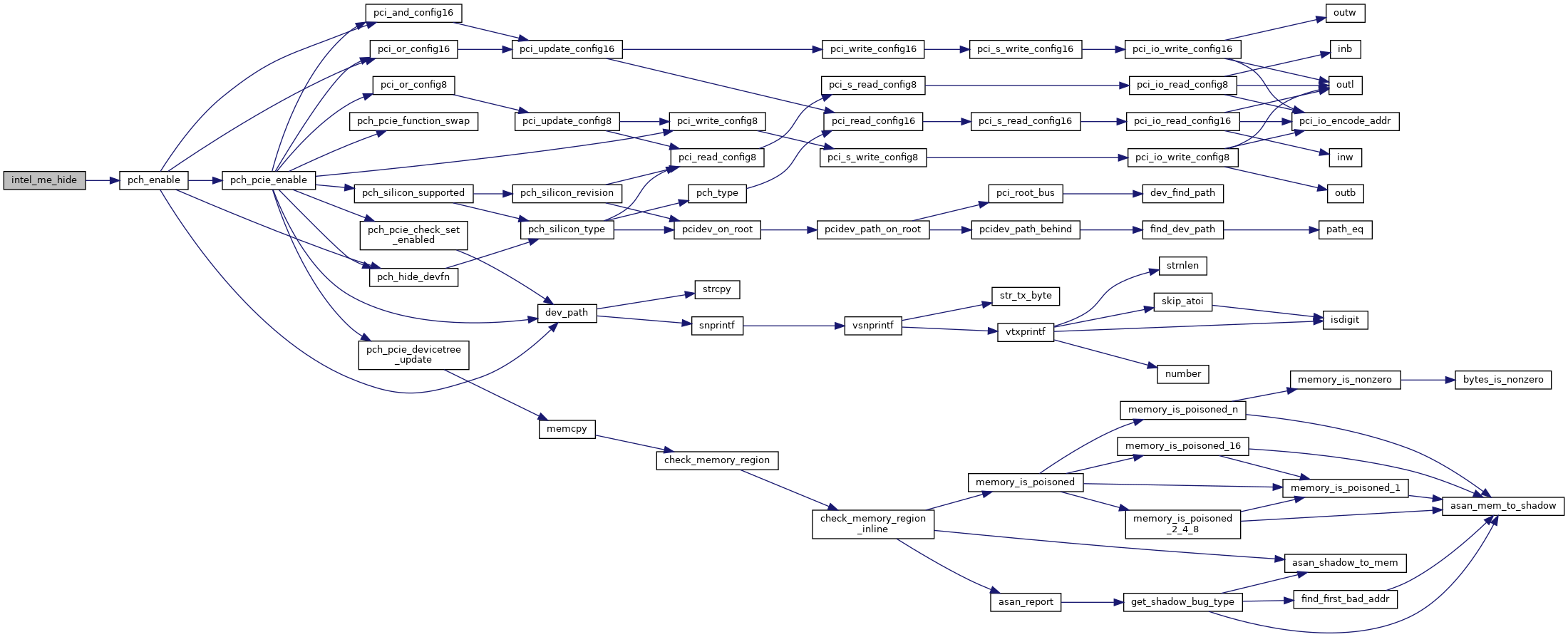

◆ intel_me_hide()

◆ intel_me_status()

Definition at line 125 of file me_status.c.

References ARRAY_SIZE, BIOS_DEBUG, me_hfs::boot_options_present, me_gmes::current_pmevent, me_gmes::current_state, me_hfs::error_code, me_hfs::fpt_bad, me_hfs::ft_bup_ld_flr, me_hfs::fw_init_complete, me_cws_values, me_error_values, ME_GMES_PHASE_BUP, ME_GMES_PHASE_HOST, ME_GMES_PHASE_POLICY, ME_GMES_PHASE_ROM, me_opmode_values, me_opstate_values, me_pmevent_values, me_progress_bup_values, me_progress_policy_values, me_progress_rom_values, me_progress_values, me_hfs::mfg_mode, me_hfs::operation_mode, me_hfs::operation_state, printk, me_gmes::progress_code, me_hfs::update_in_progress, and me_hfs::working_state.

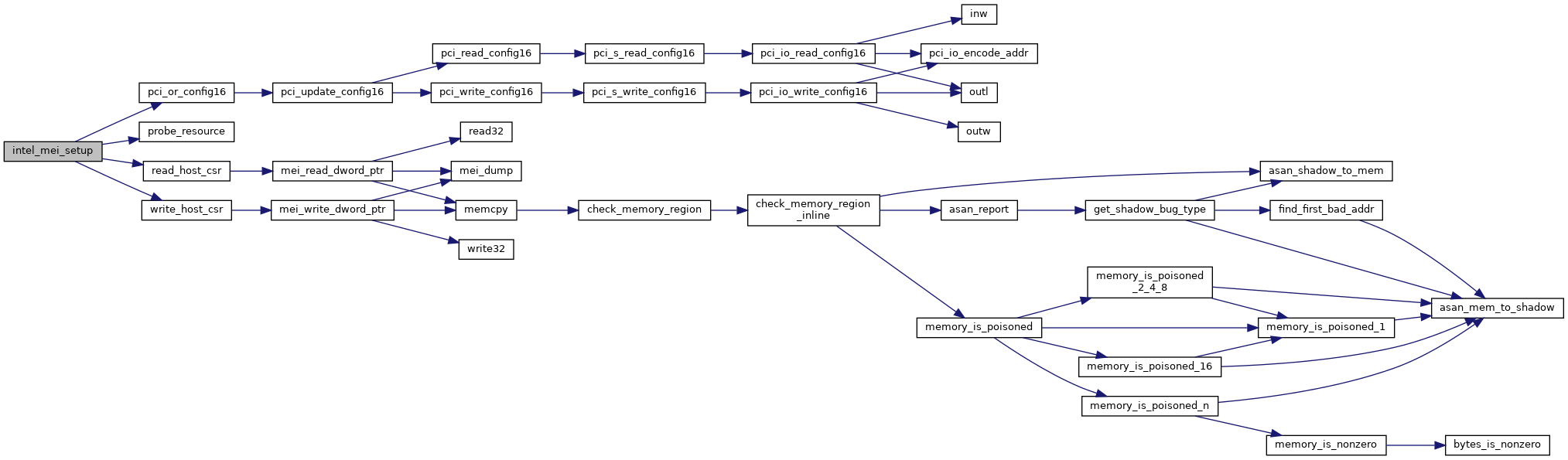

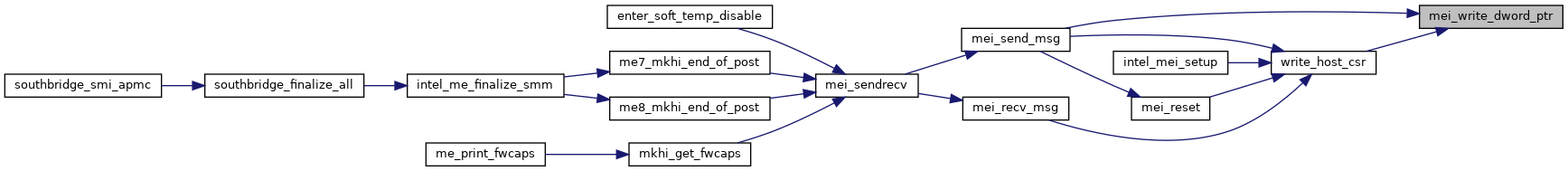

◆ intel_mei_setup()

| int intel_mei_setup |

( |

struct device * |

dev | ) |

|

Definition at line 332 of file me_common.c.

References resource::base, BIOS_DEBUG, mei_csr::interrupt_generate, mei_base_address, PCI_BASE_ADDRESS_0, PCI_COMMAND, PCI_COMMAND_MASTER, PCI_COMMAND_MEMORY, pci_or_config16(), printk, probe_resource(), read_host_csr(), mei_csr::ready, mei_csr::reset, resource::size, and write_host_csr().

◆ is_mei_base_address_valid()

◆ me_get_bios_path_string()

| const char* const me_get_bios_path_string |

( |

int |

path | ) |

|

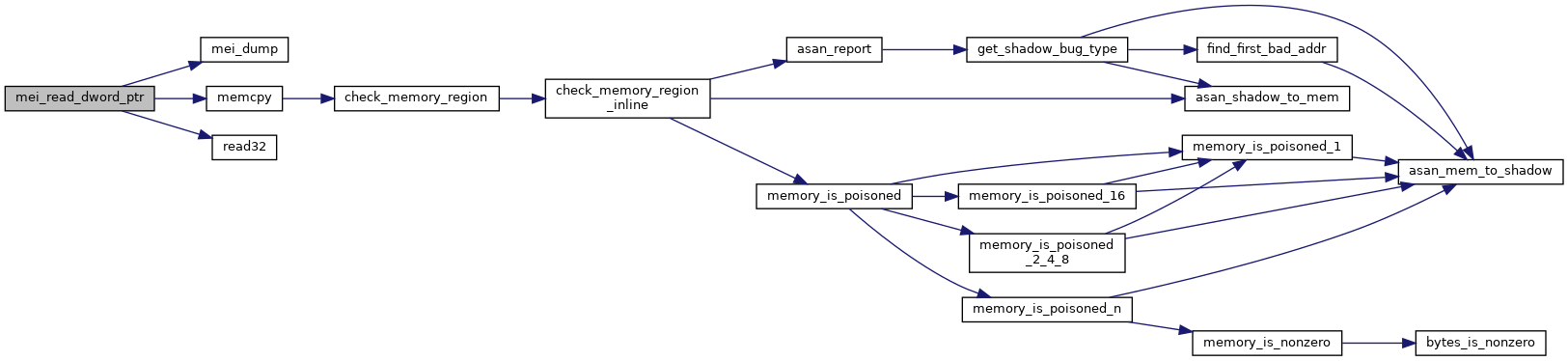

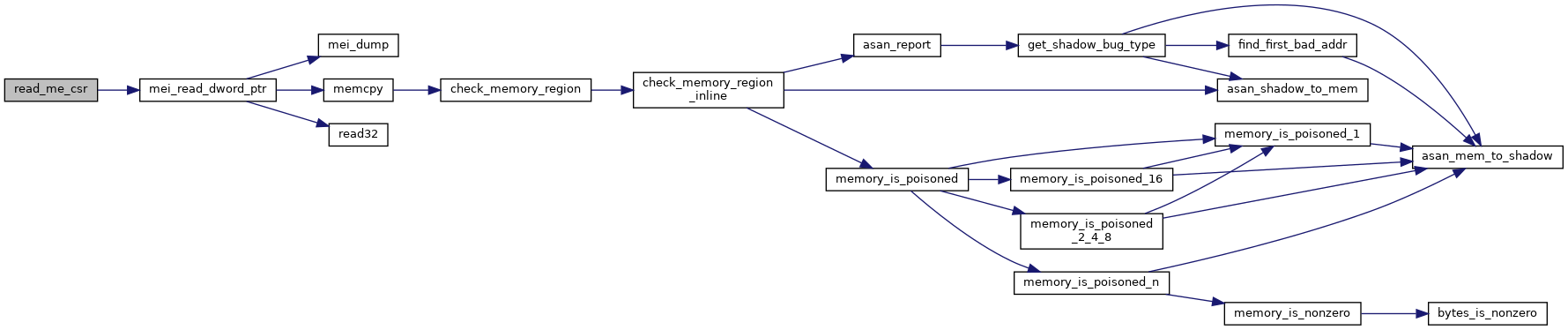

◆ mei_read_dword_ptr()

| void mei_read_dword_ptr |

( |

void * |

ptr, |

|

|

int |

offset |

|

) |

| |

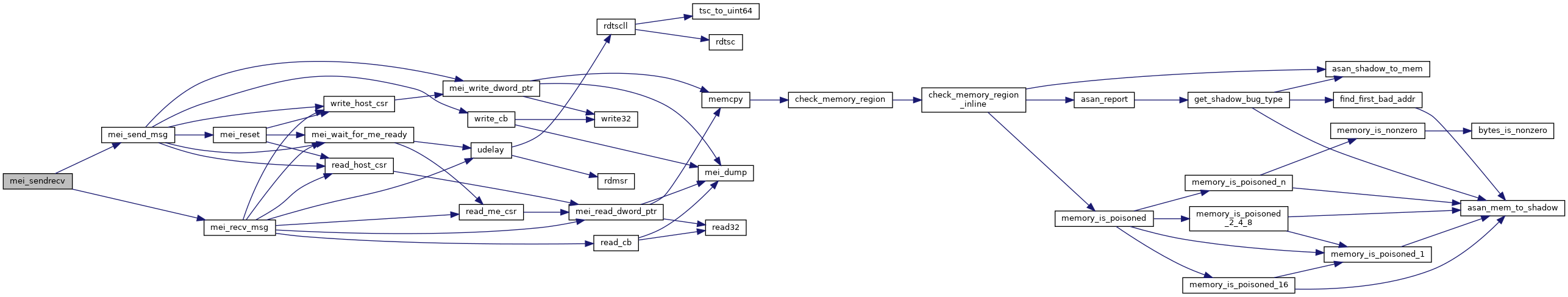

◆ mei_sendrecv()

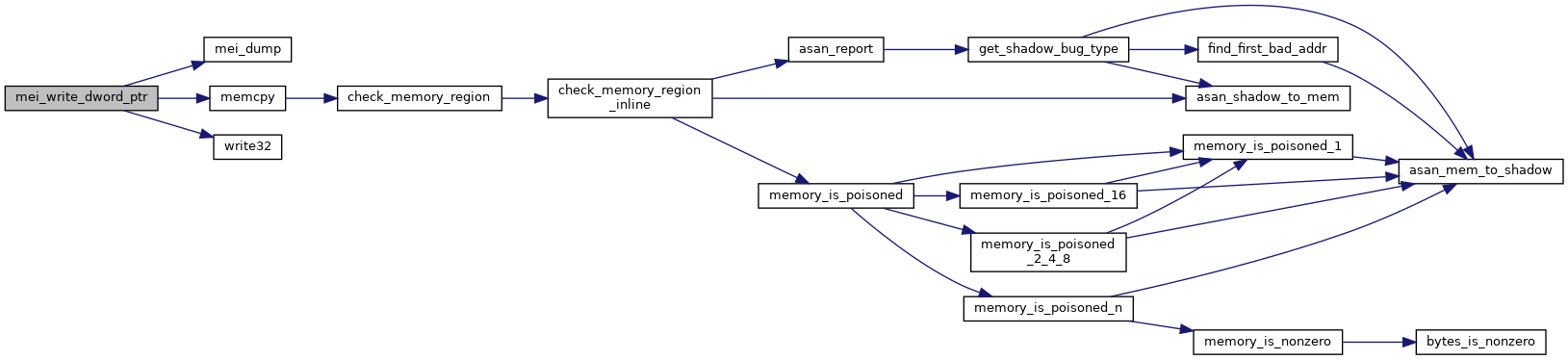

◆ mei_write_dword_ptr()

| void mei_write_dword_ptr |

( |

void * |

ptr, |

|

|

int |

offset |

|

) |

| |

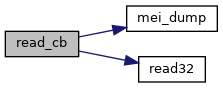

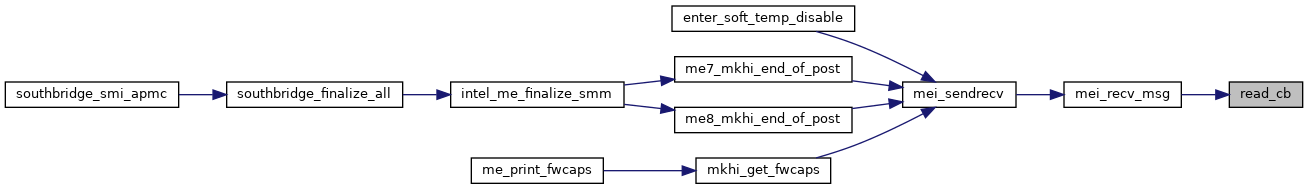

◆ read_cb()

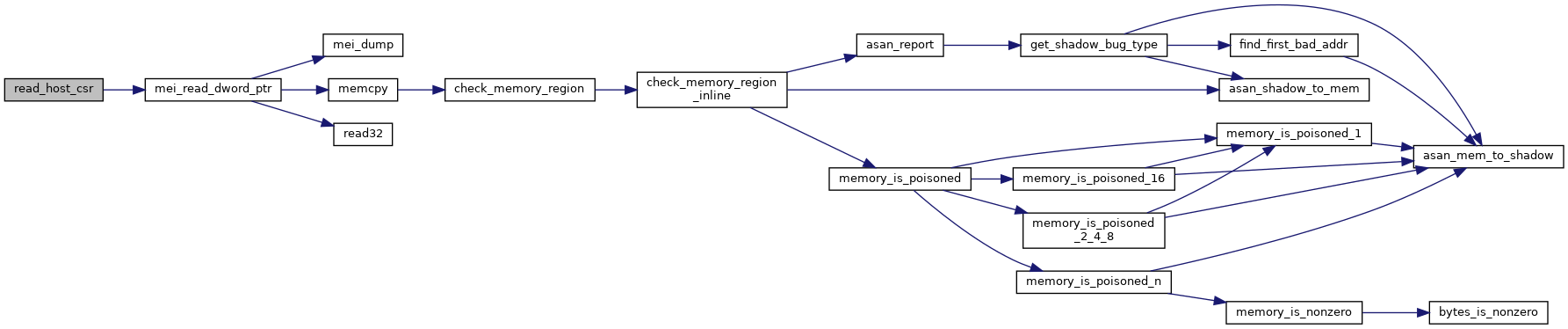

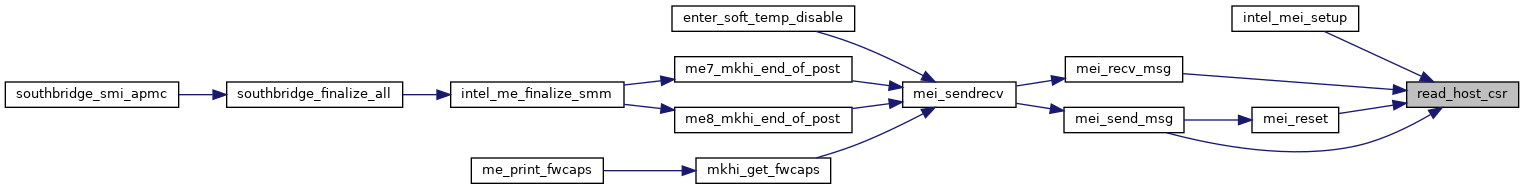

◆ read_host_csr()

◆ read_me_csr()

◆ update_mei_base_address()

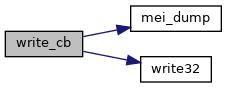

◆ write_cb()

◆ write_host_csr()

◆ __packed