|

coreboot

coreboot is an Open Source project aimed at replacing the proprietary BIOS found in most computers.

|

|

coreboot

coreboot is an Open Source project aimed at replacing the proprietary BIOS found in most computers.

|

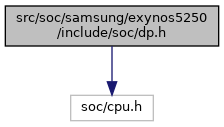

#include <soc/cpu.h>

Go to the source code of this file.

Data Structures | |

| struct | exynos5_dp |

Functions | |

| check_member (exynos5_dp, soc_general_ctl, 0x800) | |

| void | clock_init_dp_clock (void) |

Variables | |

| static struct exynos5_dp *const | exynos_dp0 = (void *)EXYNOS5_DP0_BASE |

| static struct exynos5_dp *const | exynos_dp1 = (void *)EXYNOS5_DP1_BASE |

| #define DPCD_CHANNEL_EQ_BITS |

| check_member | ( | exynos5_dp | , |

| soc_general_ctl | , | ||

| 0x800 | |||

| ) |

Definition at line 417 of file clock_init.c.

References CLK_DIV_DISP1_0_FIMD1, CLK_GATE_DP1_ALLOW, exynos5_clock::div_disp1_0, exynos_clock, exynos5_clock::gate_ip_disp1, and setbits32.

Referenced by dp_controller_init().

|

static |

|

static |

Definition at line 153 of file dp.h.

Referenced by mainboard_init().