|

coreboot

coreboot is an Open Source project aimed at replacing the proprietary BIOS found in most computers.

|

|

coreboot

coreboot is an Open Source project aimed at replacing the proprietary BIOS found in most computers.

|

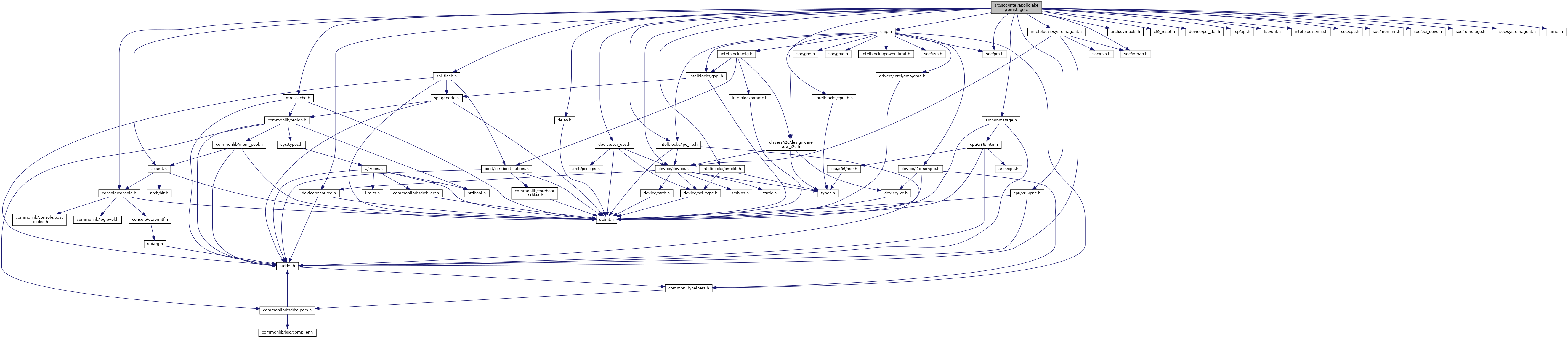

#include <arch/romstage.h>#include <device/pci_ops.h>#include <arch/symbols.h>#include <assert.h>#include <cf9_reset.h>#include <console/console.h>#include <device/device.h>#include <cpu/x86/pae.h>#include <delay.h>#include <device/pci_def.h>#include <device/resource.h>#include <fsp/api.h>#include <fsp/util.h>#include <intelblocks/cpulib.h>#include <intelblocks/lpc_lib.h>#include <intelblocks/msr.h>#include <intelblocks/pmclib.h>#include <intelblocks/systemagent.h>#include <mrc_cache.h>#include <soc/cpu.h>#include <soc/iomap.h>#include <soc/meminit.h>#include <soc/pci_devs.h>#include <soc/pm.h>#include <soc/romstage.h>#include <soc/systemagent.h>#include <spi_flash.h>#include <timer.h>#include "chip.h"

Go to the source code of this file.

Macros | |

| #define | P2SB_HPTC 0x60 |

| #define | P2SB_HPTC_ADDRESS_ENABLE (1 << 7) |

| #define | P2SB_HPTC_ADDRESS_SELECT_0 (0 << 0) |

| #define | P2SB_HPTC_ADDRESS_SELECT_1 (1 << 0) |

| #define | P2SB_HPTC_ADDRESS_SELECT_2 (2 << 0) |

| #define | P2SB_HPTC_ADDRESS_SELECT_3 (3 << 0) |

Functions | |

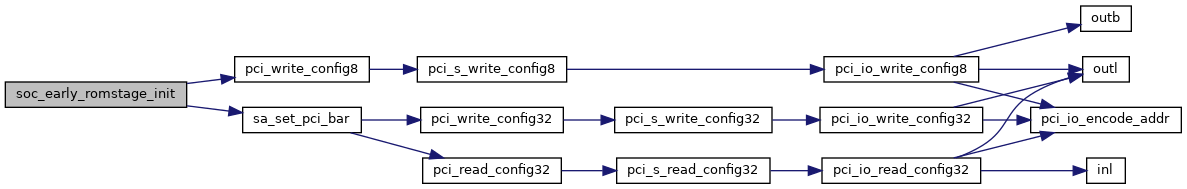

| static void | soc_early_romstage_init (void) |

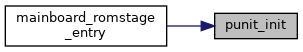

| static bool | punit_init (void) |

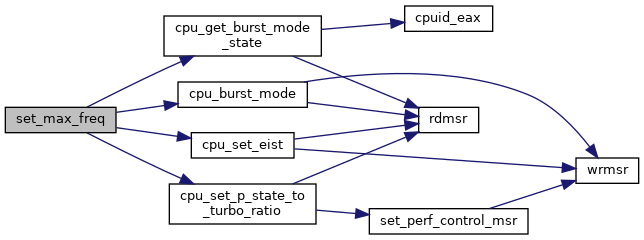

| void | set_max_freq (void) |

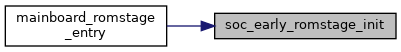

| void | mainboard_romstage_entry (void) |

| static void | fill_console_params (FSPM_UPD *mupd) |

| static void | check_full_retrain (const FSPM_UPD *mupd) |

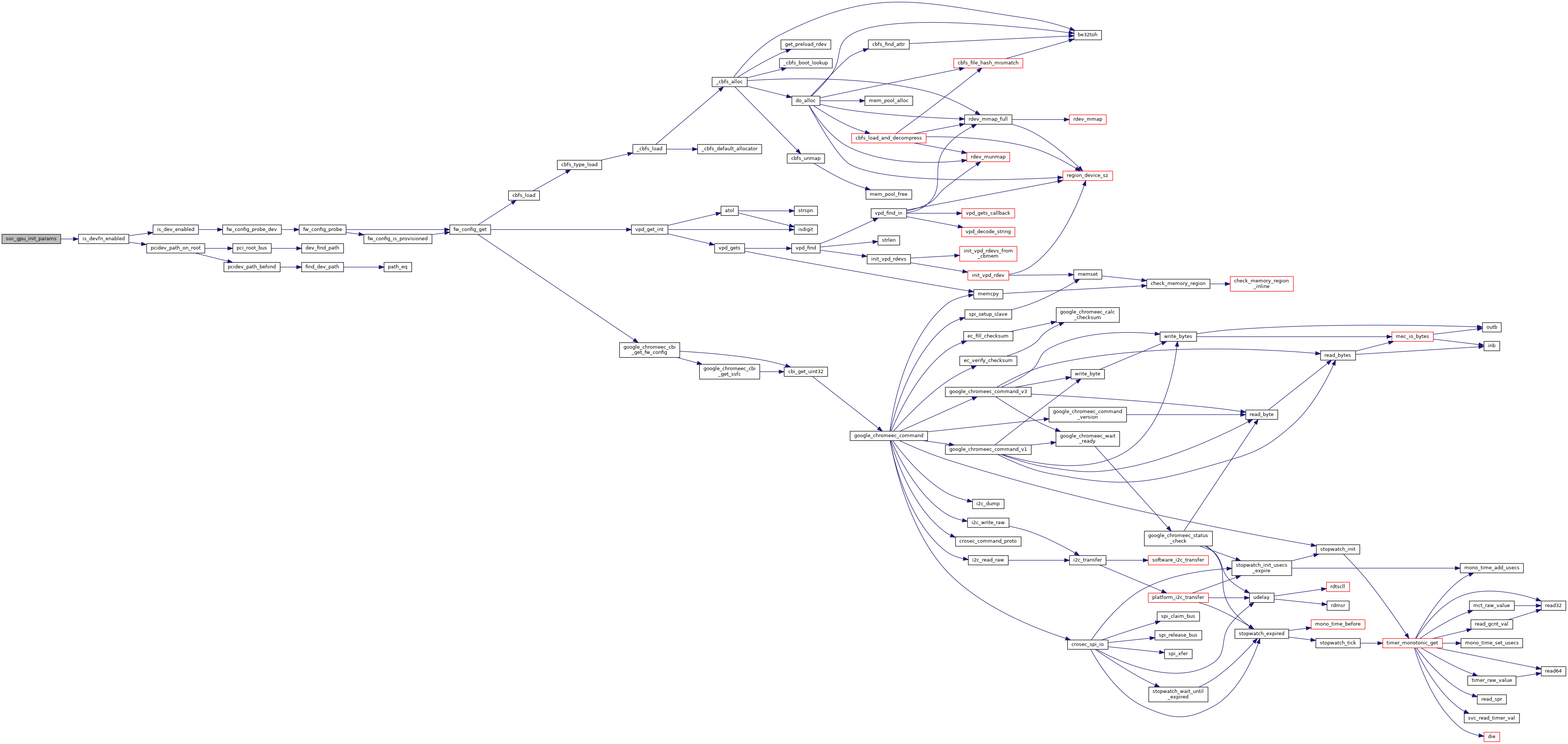

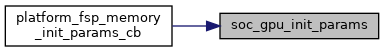

| static void | soc_gpu_init_params (FSPM_UPD *mupd) |

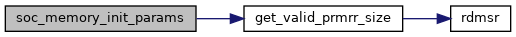

| static void | soc_memory_init_params (FSPM_UPD *mupd) |

| static void | parse_devicetree_setting (FSPM_UPD *m_upd) |

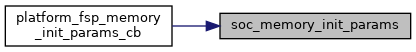

| void | platform_fsp_memory_init_params_cb (FSPM_UPD *mupd, uint32_t version) |

| __weak void | mainboard_memory_init_params (FSPM_UPD *mupd) |

| __weak void | mainboard_save_dimm_info (void) |

Variables | |

| static const uint8_t | hob_variable_guid [16] |

| static uint32_t | fsp_version |

| #define P2SB_HPTC 0x60 |

Definition at line 41 of file romstage.c.

| #define P2SB_HPTC_ADDRESS_ENABLE (1 << 7) |

Definition at line 42 of file romstage.c.

| #define P2SB_HPTC_ADDRESS_SELECT_0 (0 << 0) |

Definition at line 50 of file romstage.c.

| #define P2SB_HPTC_ADDRESS_SELECT_1 (1 << 0) |

Definition at line 51 of file romstage.c.

| #define P2SB_HPTC_ADDRESS_SELECT_2 (2 << 0) |

Definition at line 52 of file romstage.c.

| #define P2SB_HPTC_ADDRESS_SELECT_3 (3 << 0) |

Definition at line 53 of file romstage.c.

|

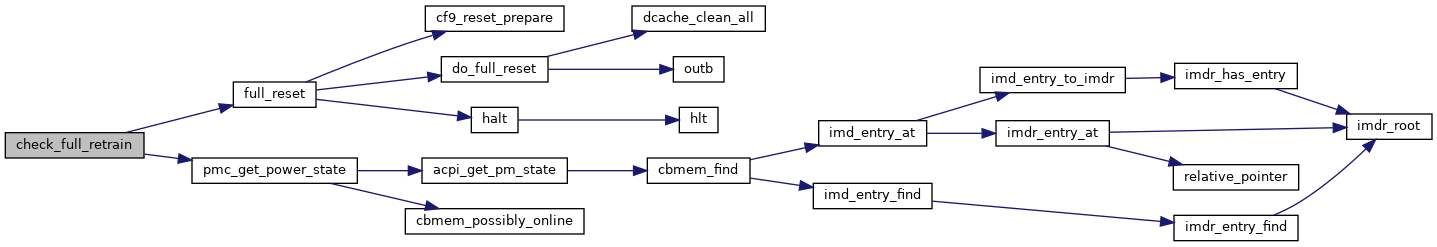

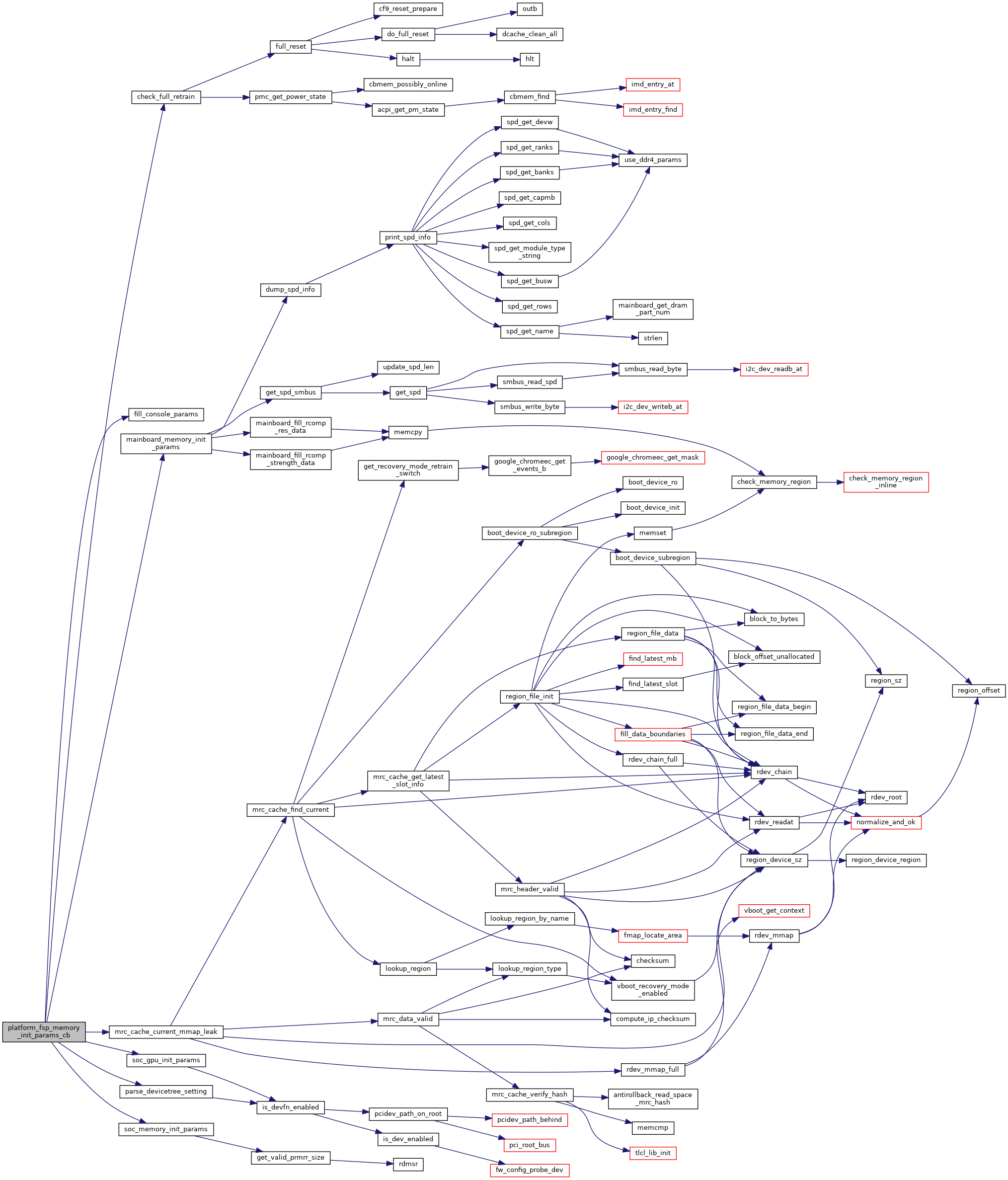

static |

Definition at line 217 of file romstage.c.

References BIOS_INFO, FSP_BOOT_WITH_FULL_CONFIGURATION, full_reset(), chipset_power_state::gen_pmcon1, pmc_get_power_state(), printk, and WARM_RESET_STS.

Referenced by platform_fsp_memory_init_params_cb().

|

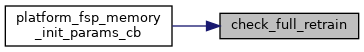

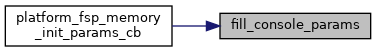

static |

Definition at line 189 of file romstage.c.

References CONFIG.

Referenced by platform_fsp_memory_init_params_cb().

Definition at line 327 of file romstage.c.

References BIOS_DEBUG, and printk.

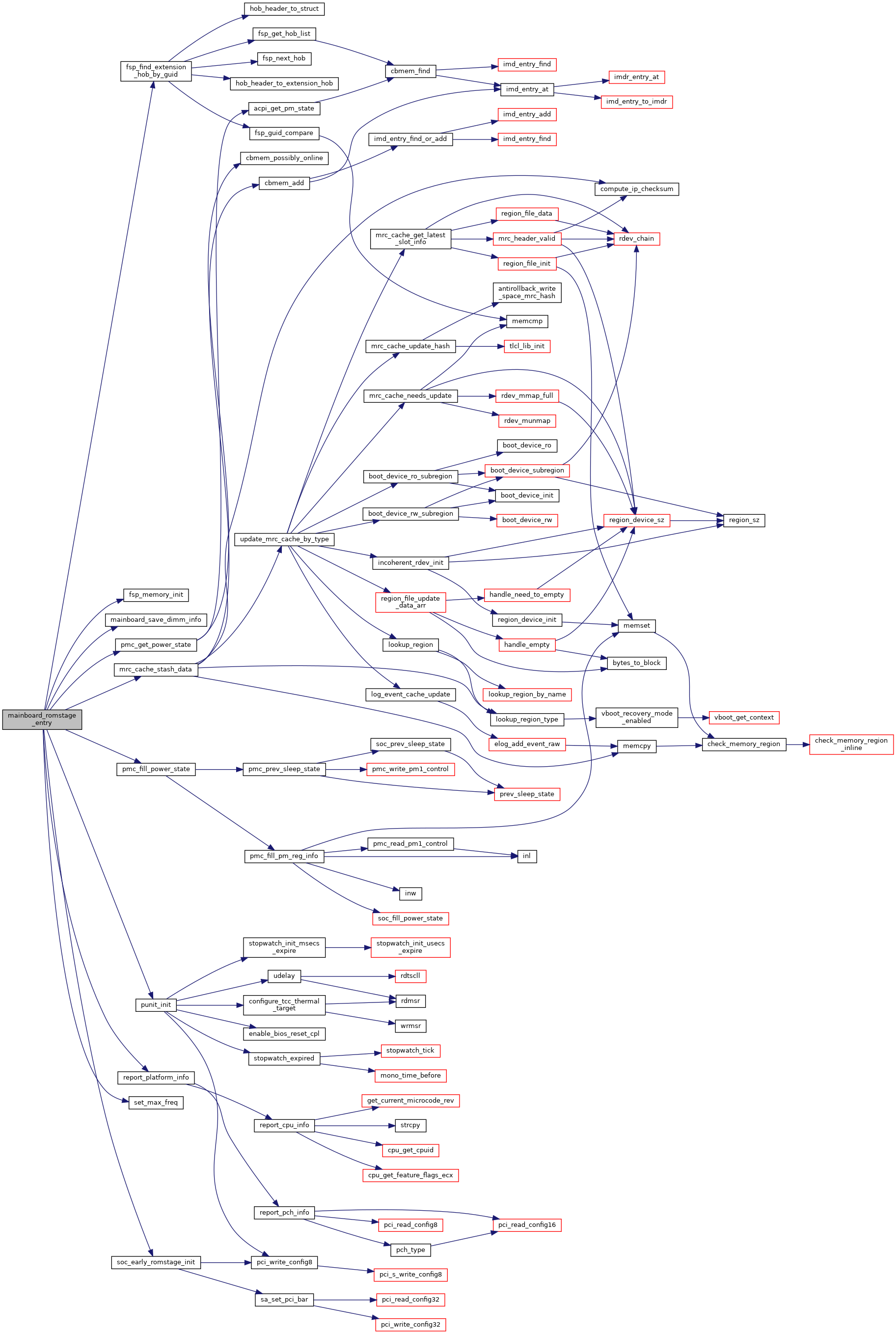

Definition at line 158 of file romstage.c.

References ACPI_S3, BIOS_DEBUG, BIOS_ERR, fsp_find_extension_hob_by_guid(), fsp_memory_init(), fsp_version, hob_variable_guid, mainboard_save_dimm_info(), mrc_cache_stash_data(), MRC_VARIABLE_DATA, pmc_fill_power_state(), pmc_get_power_state(), printk, punit_init(), report_platform_info(), set_max_freq(), and soc_early_romstage_init().

Definition at line 333 of file romstage.c.

References BIOS_DEBUG, and printk.

|

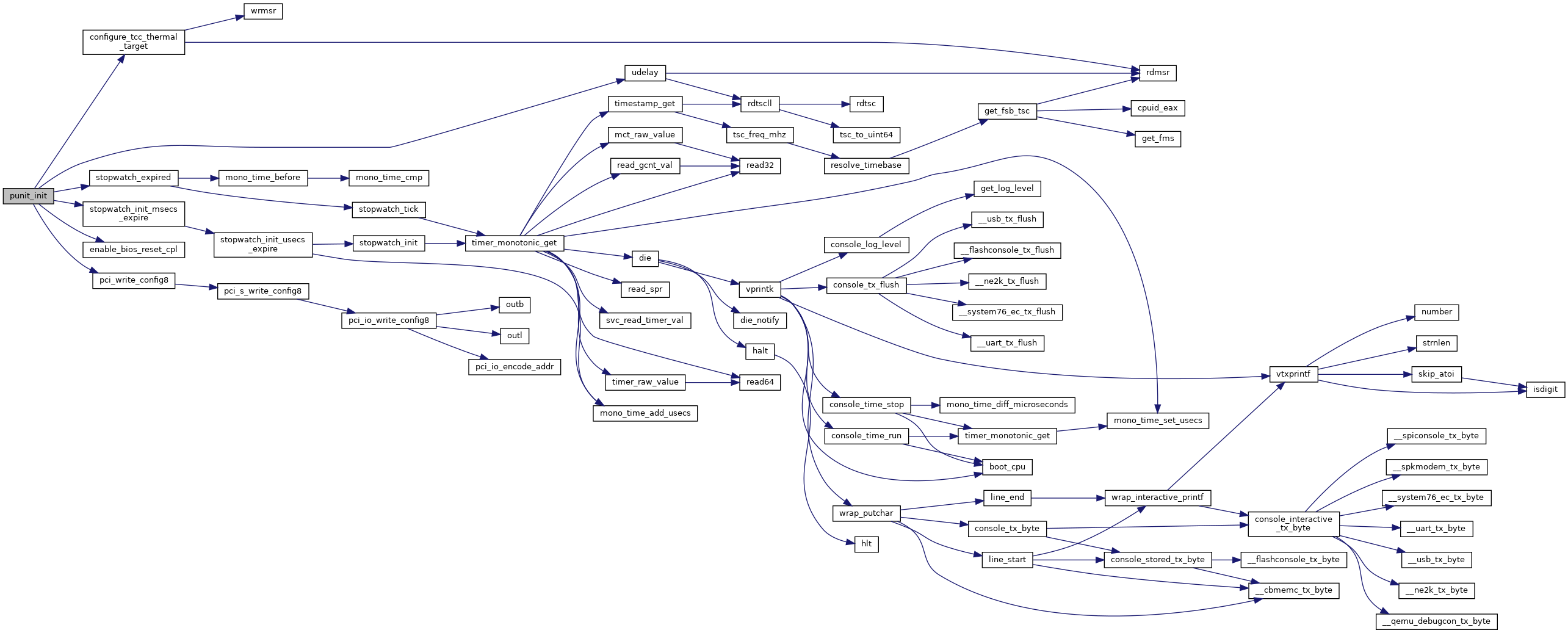

static |

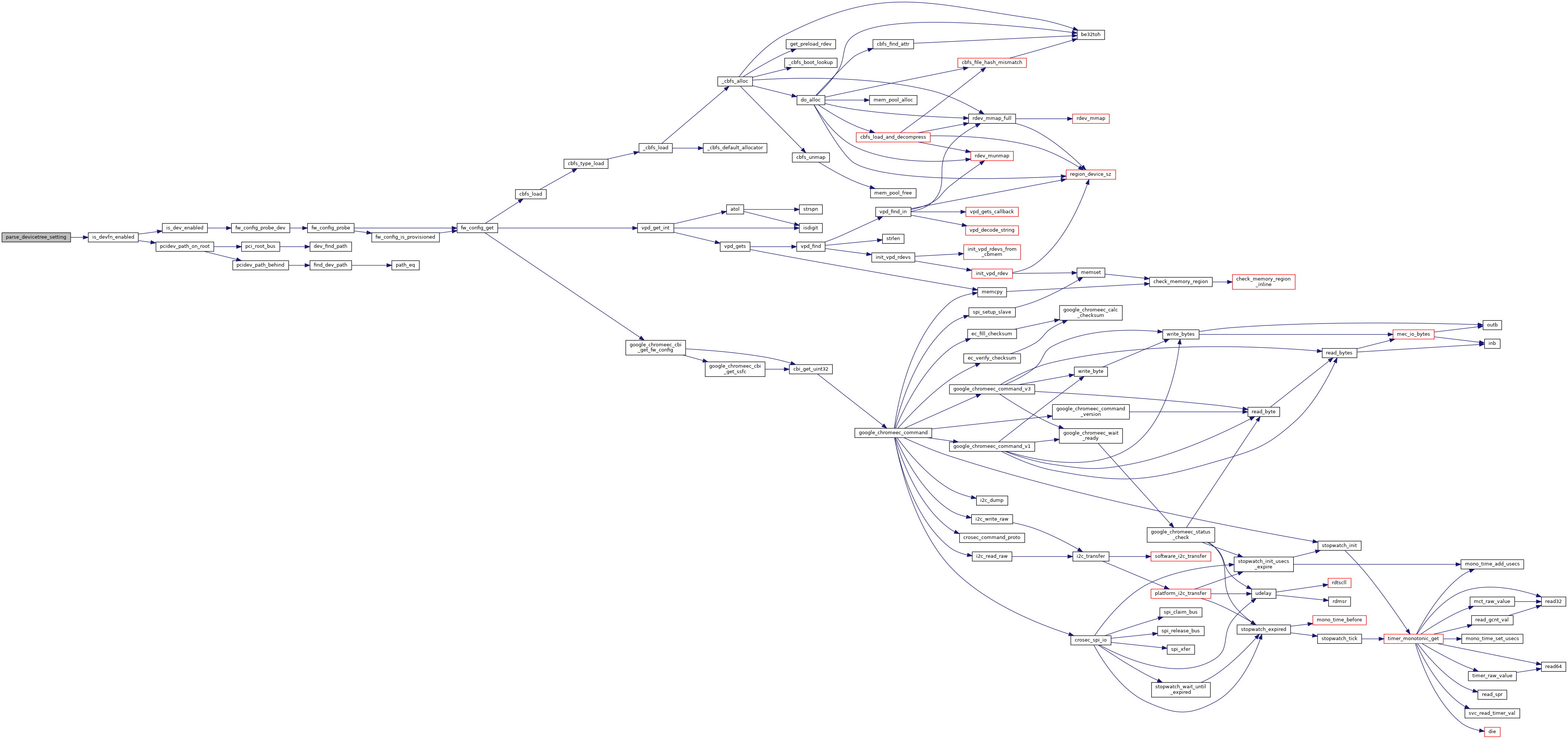

Definition at line 270 of file romstage.c.

References is_devfn_enabled(), and PCH_DEVFN_NPK.

Referenced by platform_fsp_memory_init_params_cb().

Definition at line 279 of file romstage.c.

References assert, check_full_retrain(), CONFIG, fill_console_params(), fsp_version, mainboard_memory_init_params(), mrc_cache_current_mmap_leak(), MRC_VARIABLE_DATA, NULL, parse_devicetree_setting(), soc_gpu_init_params(), soc_memory_init_params(), and version.

Definition at line 80 of file romstage.c.

References BIOS_DEBUG, BIOS_RESET_CPL, CONFIG, configure_tcc_thermal_target(), CORE_DISABLE_MASK, enable_bios_reset_cpl(), MCHBAR32, PCI_INTERRUPT_PIN, pci_write_config8(), PCODE_INIT_DONE, printk, PUINT_THERMAL_DEVICE_IRQ_LOCK, PUINT_THERMAL_DEVICE_IRQ_VEC_NUMBER, PUNIT_THERMAL_DEVICE_IRQ, SA_DEV_PUNIT, stopwatch_expired(), stopwatch_init_msecs_expire(), and udelay().

Referenced by mainboard_romstage_entry().

Definition at line 137 of file romstage.c.

References BIOS_DEBUG, BURST_MODE_UNAVAILABLE, cpu_burst_mode(), cpu_get_burst_mode_state(), cpu_set_eist(), cpu_set_p_state_to_turbo_ratio(), and printk.

Definition at line 61 of file romstage.c.

References ARRAY_SIZE, MCH_BASE_ADDRESS, MCH_BASE_SIZE, MCHBAR, P2SB_HPTC, P2SB_HPTC_ADDRESS_ENABLE, P2SB_HPTC_ADDRESS_SELECT_0, PCH_DEV_P2SB, pci_write_config8(), and sa_set_pci_bar().

Referenced by mainboard_romstage_entry().

|

static |

Definition at line 232 of file romstage.c.

References CONFIG, is_devfn_enabled(), and SA_DEVFN_IGD.

Referenced by platform_fsp_memory_init_params_cb().

|

static |

Definition at line 245 of file romstage.c.

References FSP_M_CONFIG, and get_valid_prmrr_size().

Referenced by platform_fsp_memory_init_params_cb().

|

static |

Definition at line 38 of file romstage.c.

Referenced by cache_as_ram_stage_main(), check_region_overlap(), do_fsp_memory_init(), do_fsp_post_memory_init(), lb_string_platform_blob_version(), mainboard_romstage_entry(), platform_fsp_memory_init_params_cb(), and save_memory_training_data().

|

static |

Definition at line 33 of file romstage.c.

Referenced by mainboard_romstage_entry().