|

coreboot

coreboot is an Open Source project aimed at replacing the proprietary BIOS found in most computers.

|

|

coreboot

coreboot is an Open Source project aimed at replacing the proprietary BIOS found in most computers.

|

Go to the source code of this file.

Data Structures | |

| struct | config_data |

Typedefs | |

| typedef struct config_data | config_data |

Enumerations | |

| enum | gpio_group_sel { GPIOA = 0 , GPIOB , GPIOC , GPIOD , GPIOE , GPIOF , GPIOG , GPIOH , GPIOI , GPIOJ , GPIOK , GPIOL , GPIOM , GPION , GPIOO , GPIOP , GPIOQ , GPIOR , GPIOS , GPIOT , GPIOU , GPIOV , GPIOW , GPIOX , GPIOY , GPIOZ , GPIOAA , GPIOAB } |

| enum | { Step1 = 0 , Step2 , Step3 , Step4 , Step5 , Step6 , Step7 , Step8 , Step9 , Step10 , Step11 , Step12 , Step13 , Step14 , Step15 , Step16 , Step17 , Step18 , Step19 , Step20 } |

| enum | { ARM = 0 , LPC , CoprocessorCPU , Reserved } |

| enum | config_type { PCIE_CONFIG_UNKNOWN = 0x0 , PCIE_CONFIG_A = 0x1 , PCIE_CONFIG_B = 0x2 , PCIE_CONFIG_C = 0x3 , PCIE_CONFIG_D = 0x4 , SIO = 0 , MEM , NOP } |

Functions | |

| void | aspeed_enable_serial (pnp_devfn_t dev, uint16_t iobase) |

| void | aspeed_early_config (pnp_devfn_t dev, config_data *table, uint8_t count) |

| void | aspeed_enable_port80_direct_gpio (pnp_devfn_t dev, gpio_group_sel g) |

| void | aspeed_enable_uart_pin (pnp_devfn_t dev) |

| void | pnp_enter_conf_state (pnp_devfn_t dev) |

| void | pnp_exit_conf_state (pnp_devfn_t dev) |

| void | lpc_read (uint8_t port, uint32_t addr, uint32_t *value) |

| void | lpc_write (uint8_t port, uint32_t addr, uint32_t data) |

| #define AndMask32 | ( | HighBit, | |

| LowBit | |||

| ) | ~((((uint32_t) 1 << (HighBit - LowBit + 1)) - 1) << LowBit) |

| #define ASPEED_ADC_BASE (ASPEED_MEM_BASE1 + 0x9000) |

| #define ASPEED_APB2PCI_BASE (ASPEED_MEM_BASE2 + 0xC000) |

| #define ASPEED_BAT_BASE (ASPEED_MEM_BASE1 + 0xF000) |

| #define ASPEED_ESPI_BASE (ASPEED_MEM_BASE1 + 0xE000) |

| #define ASPEED_GFX_BASE (ASPEED_MEM_BASE1 + 0x6000) |

| #define ASPEED_GPIO_BASE (ASPEED_MEM_BASE2) |

| #define ASPEED_HACE_BASE (ASPEED_MEM_BASE1 + 0x3000) |

| #define ASPEED_I2C_BASE (ASPEED_MEM_BASE2 + 0xA000) |

| #define ASPEED_JTAG_BASE (ASPEED_MEM_BASE1 + 0x4000) |

| #define ASPEED_LPC_BASE (ASPEED_MEM_BASE2 + 0x9000) |

| #define ASPEED_LPC_PLUS_BASE (ASPEED_MEM_BASE1 + 0xC000) |

| #define ASPEED_MCTP_BASE (ASPEED_MEM_BASE1 + 0x8000) |

| #define ASPEED_MMC_BASE (ASPEED_MEM_BASE1) |

| #define ASPEED_PCIE_BASE (ASPEED_MEM_BASE1 + 0xD000) |

| #define ASPEED_PECI_BASE (ASPEED_MEM_BASE2 + 0xB000) |

| #define ASPEED_PUART_BASE (ASPEED_MEM_BASE2 + 0x8000) |

| #define ASPEED_PWM_FAN_BASE (ASPEED_MEM_BASE2 + 0x6000) |

| #define ASPEED_RTC_BASE (ASPEED_MEM_BASE2 + 0x1000) |

| #define ASPEED_SCU_BASE (ASPEED_MEM_BASE1 + 0x2000) |

| #define ASPEED_TIMER_BASE (ASPEED_MEM_BASE2 + 0x2000) |

| #define ASPEED_UART1_BASE (ASPEED_MEM_BASE2 + 0x3000) |

| #define ASPEED_UART2_BASE (ASPEED_MEM_BASE2 + 0xD000) |

| #define ASPEED_UART3_BASE (ASPEED_MEM_BASE2 + 0xE000) |

| #define ASPEED_UART4_BASE (ASPEED_MEM_BASE2 + 0xF000) |

| #define ASPEED_UART5_BASE (ASPEED_MEM_BASE2 + 0x4000) |

| #define ASPEED_USB_BASE (ASPEED_MEM_BASE1 + 0x1000) |

| #define ASPEED_VUART_BASE (ASPEED_MEM_BASE2 + 0x7000) |

| #define ASPEED_WDT_BASE (ASPEED_MEM_BASE2 + 0x5000) |

| #define ASPEED_X_DMA_BASE (ASPEED_MEM_BASE1 + 0x7000) |

| typedef struct config_data config_data |

| anonymous enum |

| enum config_type |

| enum gpio_group_sel |

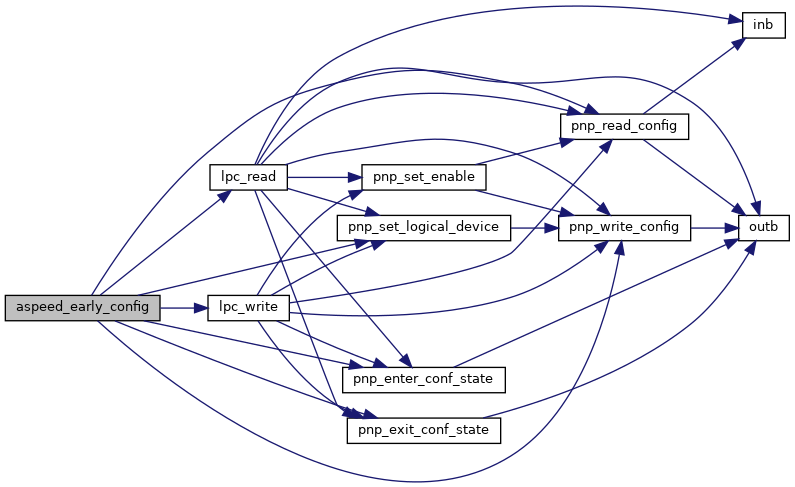

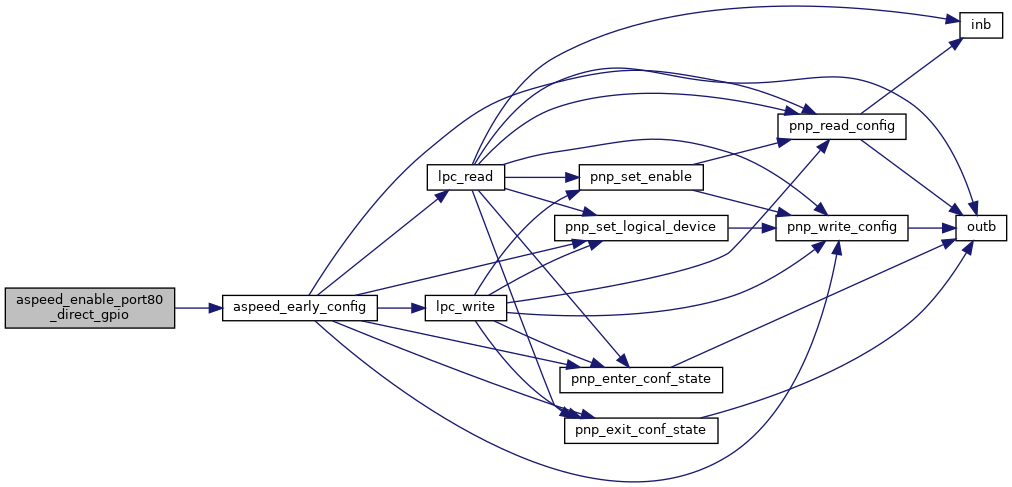

| void aspeed_early_config | ( | pnp_devfn_t | dev, |

| config_data * | table, | ||

| uint8_t | count | ||

| ) |

Definition at line 76 of file early_config.c.

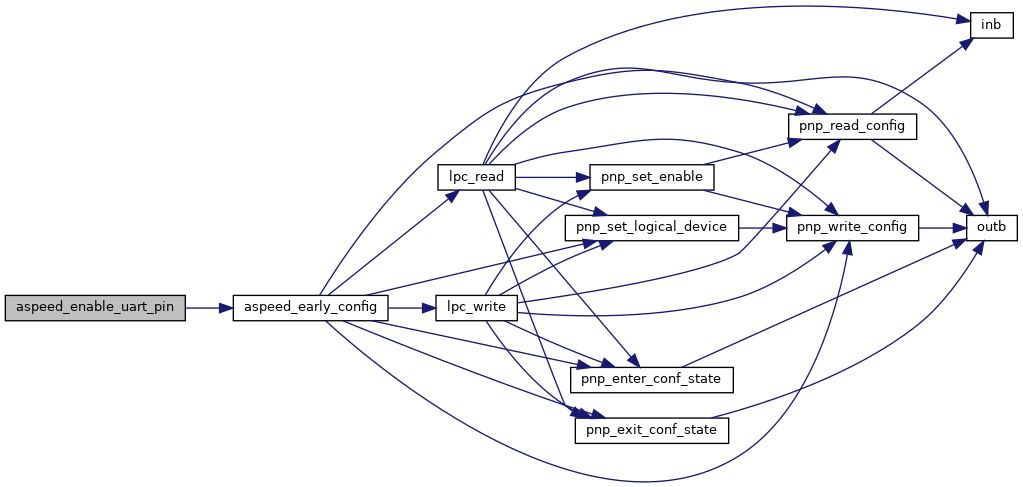

References ACT_REG, ACTIVATE_VALUE, addr, config_data::and, base, count, lpc_read(), lpc_write(), MEM, config_data::or, pnp_enter_conf_state(), pnp_exit_conf_state(), pnp_read_config(), pnp_set_logical_device(), pnp_write_config(), SIO, and type.

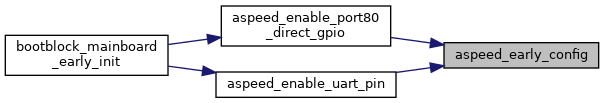

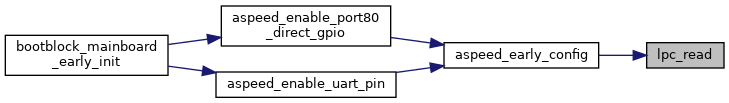

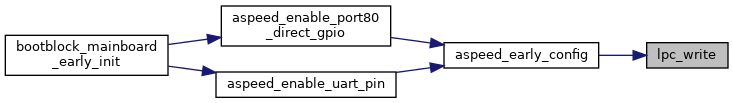

Referenced by aspeed_enable_port80_direct_gpio(), and aspeed_enable_uart_pin().

| void aspeed_enable_port80_direct_gpio | ( | pnp_devfn_t | dev, |

| gpio_group_sel | g | ||

| ) |

Definition at line 105 of file early_config.c.

References A_B_C_D_CMD_SOURCE0_REG, A_B_C_D_CMD_SOURCE1_REG, A_B_C_D_DIRECTION_REG, ACT_REG, config_data::and, AndMask32, ARRAY_SIZE, aspeed_early_config(), ASPEED_GPIO_BASE, ASPEED_LPC_BASE, ASPEED_SCU_BASE, config_data::base, E_F_G_H_CMD_SOURCE0_REG, E_F_G_H_CMD_SOURCE1_REG, E_F_G_H_DIRECTION_REG, FRQ_CNT_CTL_REG, GPIOA, GPIOAA, GPIOAB, GPIOB, GPIOC, GPIOD, GPIOE, GPIOF, GPIOG, GPIOH, GPIOI, GPIOJ, GPIOK, GPIOL, GPIOM, GPION, GPIOO, GPIOP, GPIOQ, GPIOR, GPIOS, GPIOT, GPIOU, GPIOV, GPIOW, GPIOX, GPIOY, GPIOZ, HICR5_REG, HW_STRAP_REG, I_J_K_L_CMD_SOURCE0_REG, I_J_K_L_CMD_SOURCE1_REG, I_J_K_L_DIRECTION_REG, LHCR0_REG, LPC, M_N_O_P_CMD_SOURCE0_REG, M_N_O_P_CMD_SOURCE1_REG, M_N_O_P_DIRECTION_REG, MEM, MISC_CTL_REG, MUL_FUNC_PIN_CTL1_REG, MUL_FUNC_PIN_CTL2_REG, MUL_FUNC_PIN_CTL3_REG, MUL_FUNC_PIN_CTL4_REG, MUL_FUNC_PIN_CTL5_REG, MUL_FUNC_PIN_CTL6_REG, MUL_FUNC_PIN_CTL7_REG, MUL_FUNC_PIN_CTL8_REG, MUL_FUNC_PIN_CTL9_REG, NOP, config_data::or, PORT80_GPIO_EN, PORT80_GPIO_SEL_REG, PRO_KEY_PASSWORD, PRO_KEY_REG, Q_R_S_T_CMD_SOURCE0_REG, Q_R_S_T_CMD_SOURCE1_REG, Q_R_S_T_DIRECTION_REG, config_data::reg, SIO, SNOOP_ADDR_EN, SNOOP_ADDR_PORT80, SNPWADR_REG, Step1, Step10, Step11, Step12, Step13, Step2, Step3, Step4, Step5, Step6, Step7, Step8, Step9, TO_BE_UPDATE, config_data::type, U_V_W_X_CMD_SOURCE0_REG, U_V_W_X_CMD_SOURCE1_REG, U_V_W_X_DIRECTION_REG, Y_Z_AA_AB_CMD_SOURCE0_REG, Y_Z_AA_AB_CMD_SOURCE1_REG, and Y_Z_AA_AB_DIRECTION_REG.

Referenced by bootblock_mainboard_early_init().

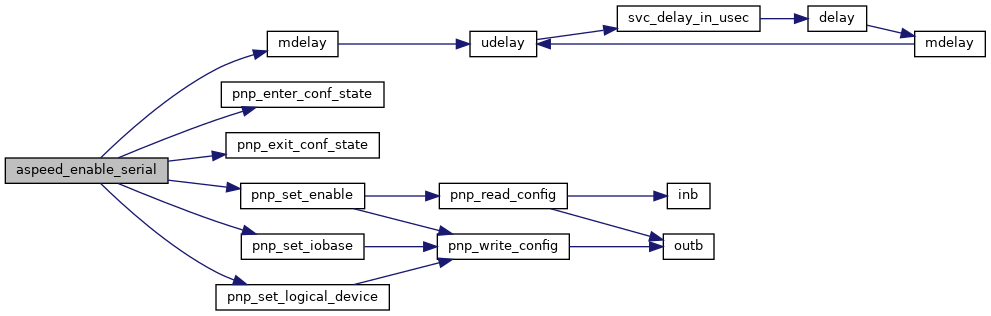

| void aspeed_enable_serial | ( | pnp_devfn_t | dev, |

| uint16_t | iobase | ||

| ) |

Definition at line 45 of file early_serial.c.

References CONFIG, mdelay(), pnp_enter_conf_state(), pnp_exit_conf_state(), PNP_IDX_IO0, pnp_set_enable(), pnp_set_iobase(), and pnp_set_logical_device().

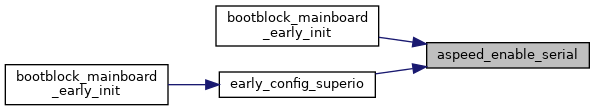

Referenced by bootblock_mainboard_early_init(), and early_config_superio().

| void aspeed_enable_uart_pin | ( | pnp_devfn_t | dev | ) |

Definition at line 508 of file early_config.c.

References config_data::and, AndMask32, ARRAY_SIZE, aspeed_early_config(), ASPEED_SCU_BASE, DIGI_VIDEO_OUT_PINS_DIS, LDN_SUART1, LDN_SUART2, LDN_SUART3, LDN_SUART4, MEM, MUL_FUNC_PIN_CTL1_REG, MUL_FUNC_PIN_CTL2_REG, MUL_FUNC_PIN_CTL6_REG, NOP, config_data::or, PRO_KEY_PASSWORD, PRO_KEY_REG, config_data::reg, Step1, Step2, Step3, Step4, TO_BE_UPDATE, config_data::type, UART1_RXD1_EN_BIT, UART1_TXD1_EN_BIT, UART2_RXD2_EN_BIT, UART2_TXD2_EN_BIT, UART3_RXD3_EN_BIT, UART3_TXD3_EN_BIT, UART4_RXD4_EN_BIT, and UART4_TXD4_EN_BIT.

Referenced by bootblock_mainboard_early_init().

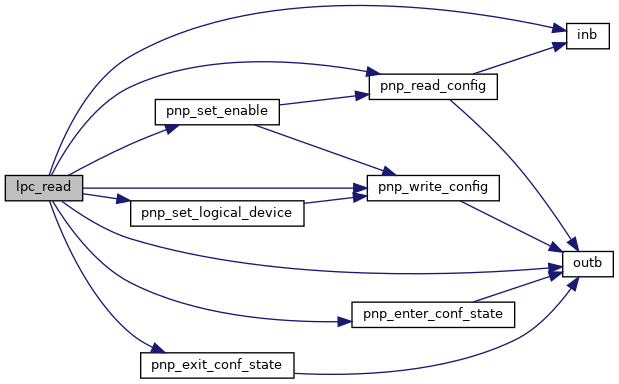

Definition at line 9 of file early_config.c.

References addr, inb(), LDN_ILPC2AHB, LPC2AHB_4_BYTE, LPC2AHB_ADD0_REG, LPC2AHB_ADD1_REG, LPC2AHB_ADD2_REG, LPC2AHB_ADD3_REG, LPC2AHB_DAT0_REG, LPC2AHB_DAT1_REG, LPC2AHB_DAT2_REG, LPC2AHB_DAT3_REG, LPC2AHB_LEN_REG, LPC2AHB_RW_REG, outb(), PNP_DEV, pnp_enter_conf_state(), pnp_exit_conf_state(), pnp_read_config(), pnp_set_enable(), pnp_set_logical_device(), pnp_write_config(), and value.

Referenced by aspeed_early_config().

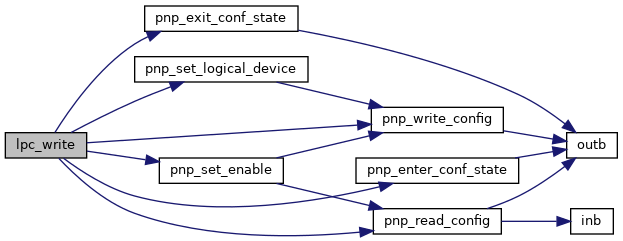

Definition at line 44 of file early_config.c.

References addr, LDN_ILPC2AHB, LPC2AHB_4_BYTE, LPC2AHB_ADD0_REG, LPC2AHB_ADD1_REG, LPC2AHB_ADD2_REG, LPC2AHB_ADD3_REG, LPC2AHB_DAT0_REG, LPC2AHB_DAT1_REG, LPC2AHB_DAT2_REG, LPC2AHB_DAT3_REG, LPC2AHB_LEN_REG, LPC2AHB_RW_REG, PNP_DEV, pnp_enter_conf_state(), pnp_exit_conf_state(), pnp_read_config(), pnp_set_enable(), pnp_set_logical_device(), and pnp_write_config().

Referenced by aspeed_early_config().

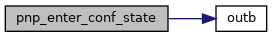

| void pnp_enter_conf_state | ( | pnp_devfn_t | dev | ) |

Definition at line 30 of file early_serial.c.

References ASPEED_ENTRY_KEY, and outb().

| void pnp_exit_conf_state | ( | pnp_devfn_t | dev | ) |

Definition at line 38 of file early_serial.c.

References ASPEED_EXIT_KEY, and outb().