|

coreboot

coreboot is an Open Source project aimed at replacing the proprietary BIOS found in most computers.

|

|

coreboot

coreboot is an Open Source project aimed at replacing the proprietary BIOS found in most computers.

|

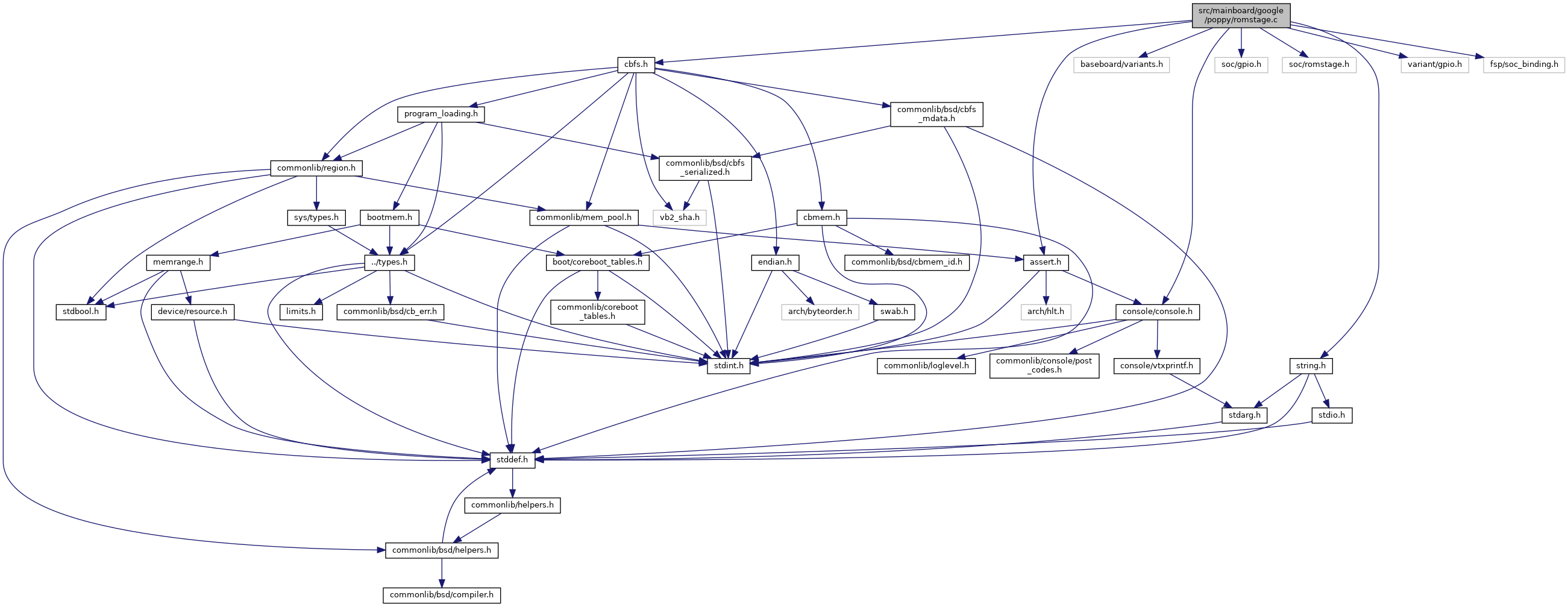

#include <assert.h>#include <baseboard/variants.h>#include <cbfs.h>#include <console/console.h>#include <soc/gpio.h>#include <soc/romstage.h>#include <string.h>#include <variant/gpio.h>#include <fsp/soc_binding.h>

Go to the source code of this file.

Data Structures | |

| struct | dram_info |

Macros | |

| #define | SPD_DRAM_TYPE_OFF 2 |

| #define | SPD_DRAM_LPDDR3 0xf1 |

| #define | SPD_DRAM_DDR4 0x0c |

| #define | SPD_LEN_LPDDR3 256 |

| #define | SPD_LEN_DDR4 512 |

| #define | SPD_DENSITY_BANKS_OFF 4 |

| #define | SPD_ADDRESSING_OFF 5 |

| #define | SPD_PART_LEN 18 |

| #define | SPD_ORG_OFF_LPDDR3 7 |

| #define | SPD_BUSW_OFF_LPDDR3 8 |

| #define | SPD_PART_OFF_LPDDR3 128 |

| #define | SPD_ORG_OFF_DDR4 12 |

| #define | SPD_BUSW_OFF_DDR4 13 |

| #define | SPD_PART_OFF_DDR4 329 |

| #define | SPD_INFO(_type) |

Functions | |

| static void | mainboard_print_spd_info (const uint8_t *spd, enum memory_type type) |

| static uintptr_t | mainboard_get_spd_data (enum memory_type type, bool use_sec_spd) |

| void | mainboard_memory_init_params (FSPM_UPD *mupd) |

Variables | |

| static const struct dram_info | spd_info [MEMORY_COUNT] |

| #define SPD_ADDRESSING_OFF 5 |

Definition at line 25 of file romstage.c.

| #define SPD_BUSW_OFF_DDR4 13 |

Definition at line 34 of file romstage.c.

| #define SPD_BUSW_OFF_LPDDR3 8 |

Definition at line 30 of file romstage.c.

| #define SPD_DENSITY_BANKS_OFF 4 |

Definition at line 24 of file romstage.c.

| #define SPD_DRAM_DDR4 0x0c |

Definition at line 17 of file romstage.c.

| #define SPD_DRAM_LPDDR3 0xf1 |

Definition at line 16 of file romstage.c.

| #define SPD_DRAM_TYPE_OFF 2 |

Definition at line 15 of file romstage.c.

| #define SPD_INFO | ( | _type | ) |

Definition at line 37 of file romstage.c.

| #define SPD_LEN_DDR4 512 |

Definition at line 21 of file romstage.c.

| #define SPD_LEN_LPDDR3 256 |

Definition at line 20 of file romstage.c.

| #define SPD_ORG_OFF_DDR4 12 |

Definition at line 33 of file romstage.c.

| #define SPD_ORG_OFF_LPDDR3 7 |

Definition at line 29 of file romstage.c.

| #define SPD_PART_LEN 18 |

Definition at line 26 of file romstage.c.

| #define SPD_PART_OFF_DDR4 329 |

Definition at line 35 of file romstage.c.

| #define SPD_PART_OFF_LPDDR3 128 |

Definition at line 31 of file romstage.c.

|

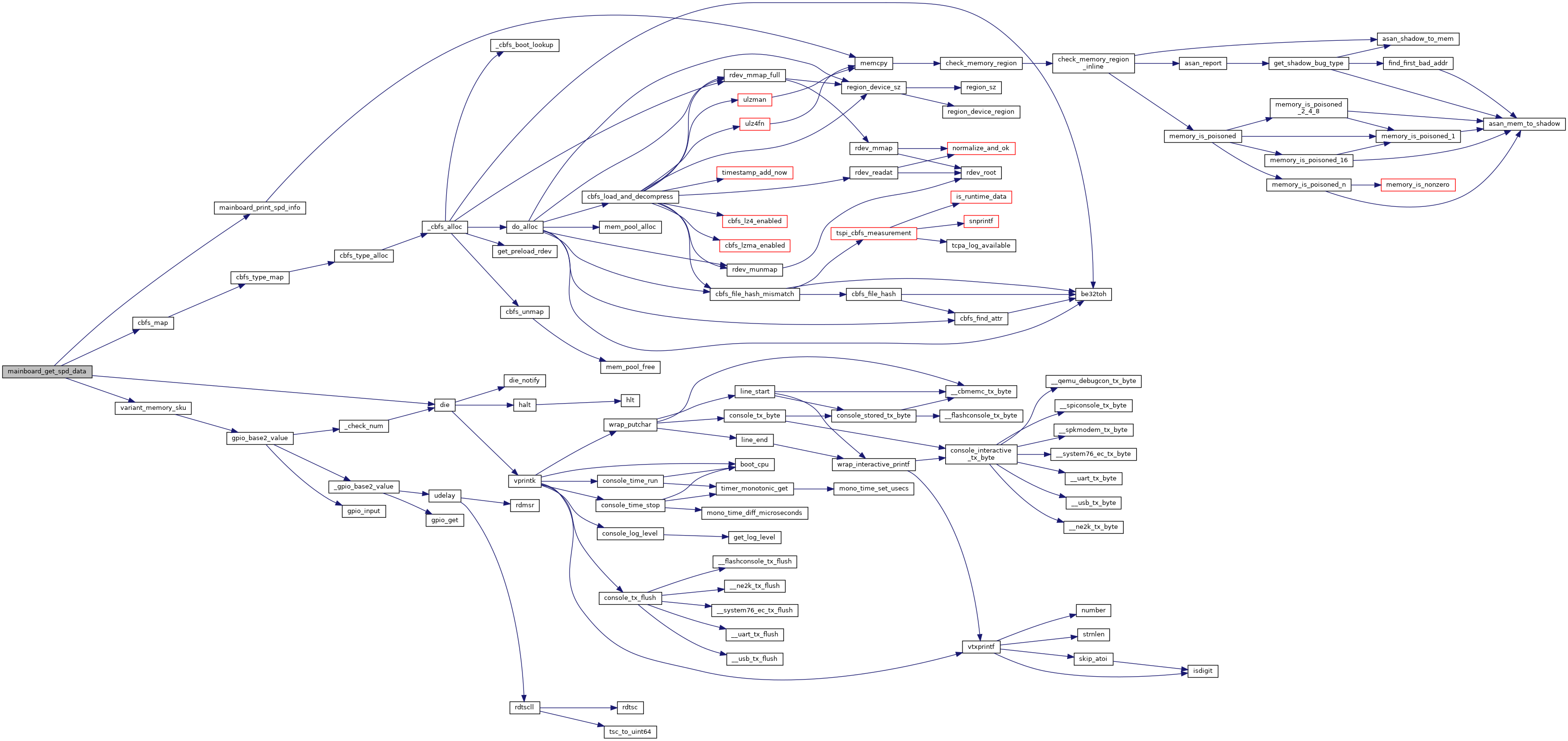

static |

Definition at line 102 of file romstage.c.

References assert, BIOS_INFO, cbfs_map(), die(), mainboard_print_spd_info(), printk, spd_index, type, and variant_memory_sku().

Referenced by mainboard_memory_init_params().

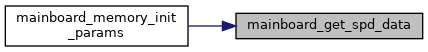

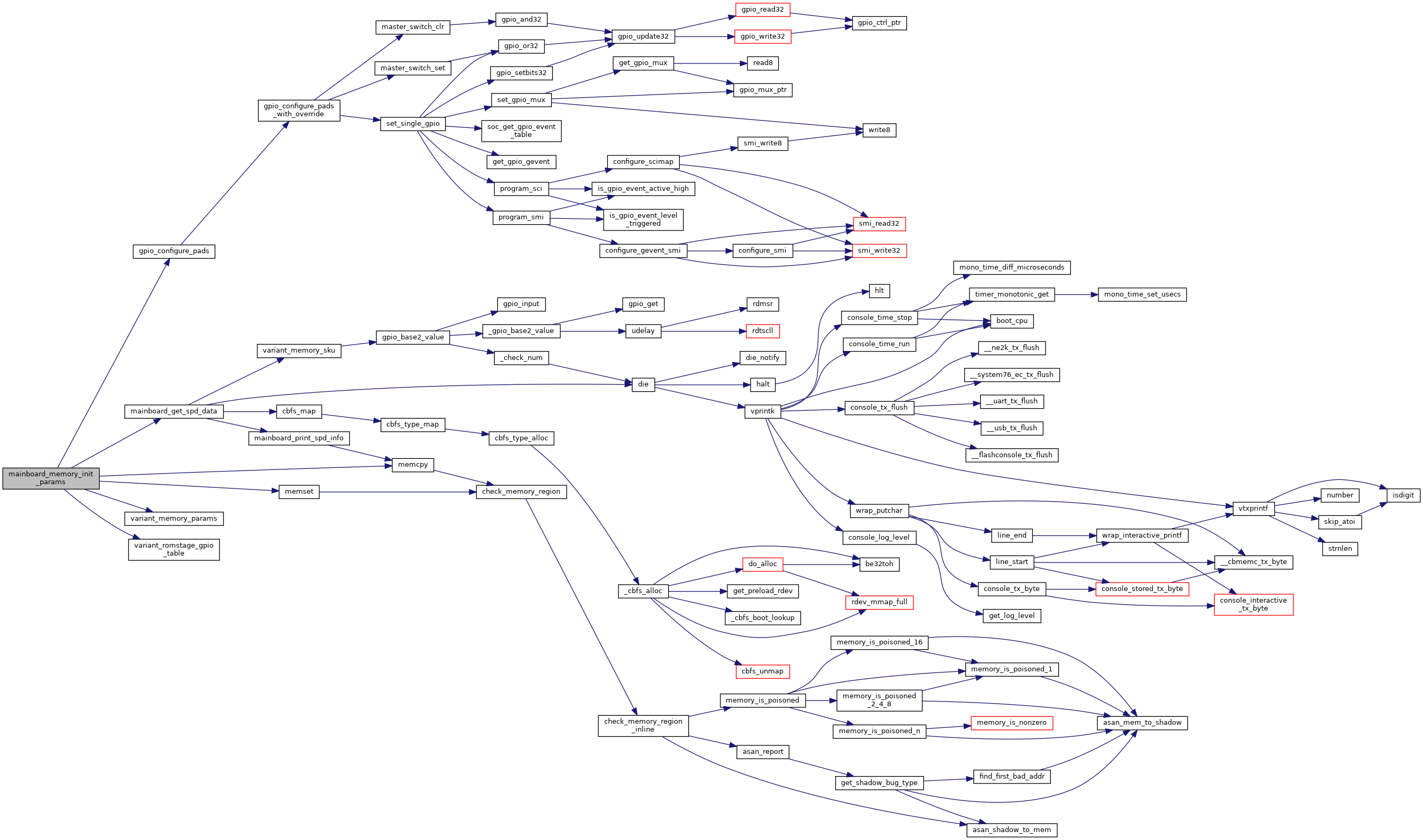

| void mainboard_memory_init_params | ( | FSPM_UPD * | mupd | ) |

Definition at line 133 of file romstage.c.

References assert, memory_params::dq_map, memory_params::dq_map_size, memory_params::dqs_map, memory_params::dqs_map_size, memory_params::enable_sa_oc_support, FSP_M_CONFIG, gpio_configure_pads(), mainboard_get_spd_data(), memcpy(), MEMORY_COUNT, memset(), memory_params::rcomp_resistor, memory_params::rcomp_resistor_size, memory_params::rcomp_target, memory_params::rcomp_target_size, memory_params::sa_voltage_offset_val, memory_params::single_channel, memory_params::type, memory_params::use_sec_spd, variant_memory_params(), and variant_romstage_gpio_table().

|

static |

Definition at line 59 of file romstage.c.

References assert, BIOS_INFO, info, memcpy(), printk, SPD_ADDRESSING_OFF, SPD_DENSITY_BANKS_OFF, SPD_DRAM_TYPE_OFF, SPD_PART_LEN, and type.

Referenced by mainboard_get_spd_data().

|

static |