|

coreboot

coreboot is an Open Source project aimed at replacing the proprietary BIOS found in most computers.

|

|

coreboot

coreboot is an Open Source project aimed at replacing the proprietary BIOS found in most computers.

|

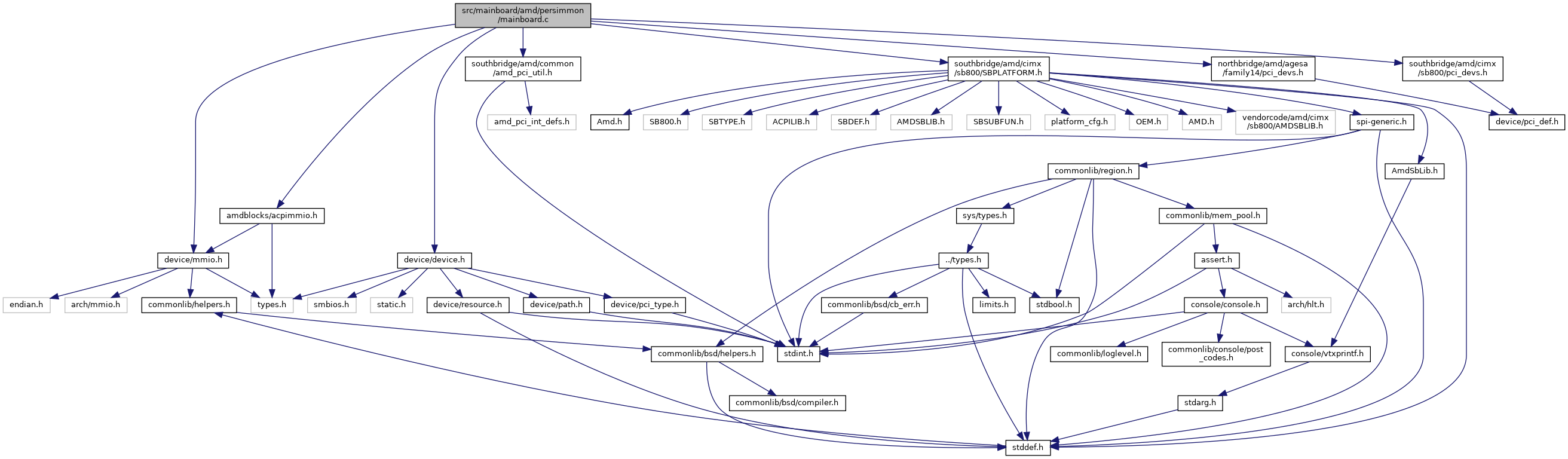

#include <amdblocks/acpimmio.h>#include <device/device.h>#include <device/mmio.h>#include <southbridge/amd/common/amd_pci_util.h>#include <southbridge/amd/cimx/sb800/SBPLATFORM.h>#include <southbridge/amd/cimx/sb800/pci_devs.h>#include <northbridge/amd/agesa/family14/pci_devs.h>

Go to the source code of this file.

Functions | |

| static void | pirq_setup (void) |

| static void | mainboard_enable (struct device *dev) |

Variables | |

| static const u8 | mainboard_picr_data [FCH_INT_TABLE_SIZE] |

| static const u8 | mainboard_intr_data [FCH_INT_TABLE_SIZE] |

| static const struct pirq_struct | mainboard_pirq_data [] |

| struct chip_operations | mainboard_ops |

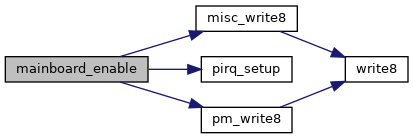

Definition at line 108 of file mainboard.c.

References misc_write8(), pirq_setup(), and pm_write8().

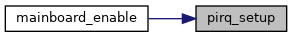

Definition at line 97 of file mainboard.c.

References ARRAY_SIZE, intr_data_ptr, mainboard_intr_data, mainboard_picr_data, mainboard_pirq_data, picr_data_ptr, pirq_data_ptr, and pirq_data_size.

Referenced by mainboard_enable().

|

static |

Definition at line 43 of file mainboard.c.

Referenced by pirq_setup().

| struct chip_operations mainboard_ops |

Definition at line 108 of file mainboard.c.

|

static |

Definition at line 26 of file mainboard.c.

Referenced by pirq_setup().

|

static |