|

coreboot

coreboot is an Open Source project aimed at replacing the proprietary BIOS found in most computers.

|

|

coreboot

coreboot is an Open Source project aimed at replacing the proprietary BIOS found in most computers.

|

#include <soc/cpu.h>

Go to the source code of this file.

Data Structures | |

| struct | exynos_dp |

| struct | exynos_fb |

| struct | edp_disp_info |

| struct | edp_link_train_info |

| struct | edp_video_info |

| struct | edp_device_info |

| struct | exynos_dp_platform_data |

Variables | |

| static struct exynos_dp *const | exynos_dp0 = (void *)EXYNOS5_DP0_BASE |

| static struct exynos_dp *const | exynos_dp1 = (void *)EXYNOS5_DP1_BASE |

| anonymous enum |

| anonymous enum |

| anonymous enum |

| anonymous enum |

| anonymous enum |

| anonymous enum |

| anonymous enum |

| enum analog_power_block |

| enum pattern_type |

| enum pll_status |

| check_member | ( | exynos_dp | , |

| phy_ctrl | , | ||

| 0x924 | |||

| ) |

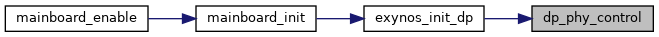

Definition at line 1141 of file dp_lowlevel.c.

References exynos5_power::dptx_phy_control, EXYNOS_DP_PHY_ENABLE, exynos_power, lread32, and lwrite32.

Referenced by exynos_init_dp().

Definition at line 368 of file dp_lowlevel.c.

References exynos_dp::common_int_mask1, exynos_dp::common_int_mask2, exynos_dp::common_int_mask3, exynos_dp::common_int_mask4, COMMON_INT_MASK_1, COMMON_INT_MASK_2, COMMON_INT_MASK_3, COMMON_INT_MASK_4, dp_regs, exynos_dp::int_sta_mask, INT_STA_MASK, and lwrite32.

| int exynos_dp_config_video_bist | ( | struct edp_device_info * | edp_info | ) |

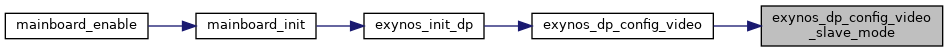

| void exynos_dp_config_video_slave_mode | ( | struct edp_video_info * | video_info | ) |

Definition at line 985 of file dp_lowlevel.c.

References AUDIO_MODE_SPDIF_MODE, BIOS_SPEW, dp_regs, exynos_dp::func_en1, H_S_POLARITY_CFG_SHIFT, video_info::h_sync_polarity, HSYNC_POLARITY_CFG, INTERACE_SCAN_CFG, INTERACE_SCAN_CFG_SHIFT, video_info::interlaced, lread32, lwrite32, MASTER_VID_FUNC_EN_N, printk, SLAVE_VID_FUNC_EN_N, exynos_dp::soc_general_ctl, V_S_POLARITY_CFG_SHIFT, video_info::v_sync_polarity, exynos_dp::video_ctl10, VIDEO_MODE_SLAVE_MODE, and VSYNC_POLARITY_CFG.

Referenced by exynos_dp_config_video().

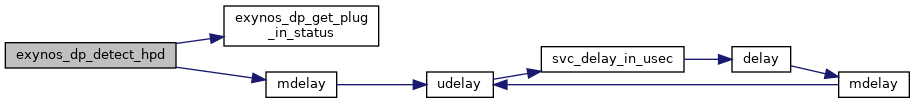

Definition at line 400 of file dp_lowlevel.c.

References DP_TIMEOUT_LOOP_COUNT, exynos_dp_get_plug_in_status(), EXYNOS_DP_SUCCESS, and mdelay().

Definition at line 54 of file dp_lowlevel.c.

References dp_regs, lread32, lwrite32, VIDEO_BIST_MASK, and exynos_dp::video_ctl4.

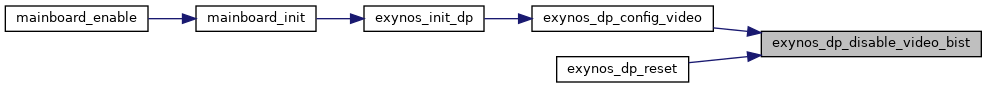

Referenced by exynos_dp_config_video(), and exynos_dp_reset().

Definition at line 946 of file dp_lowlevel.c.

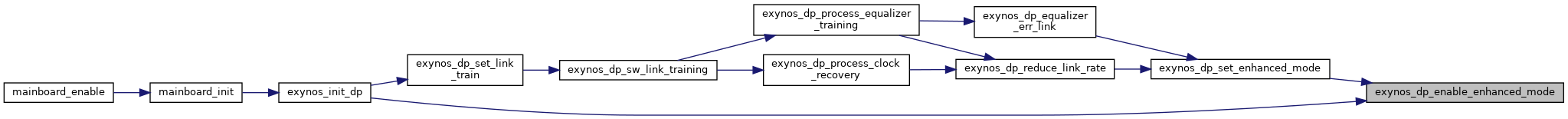

References dp_regs, ENHANCED, lread32, lwrite32, and exynos_dp::sys_ctl4.

Referenced by exynos_dp_set_enhanced_mode(), and exynos_init_dp().

Definition at line 959 of file dp_lowlevel.c.

References dp_regs, lread32, lwrite32, SCRAMBLING_DISABLE, and exynos_dp::training_ptn_set.

Referenced by exynos_dp_enable_scramble().

Definition at line 175 of file dp_lowlevel.c.

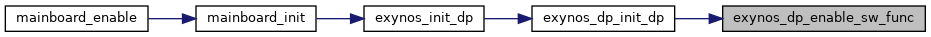

References dp_regs, exynos_dp::func_en1, lread32, lwrite32, and SW_FUNC_EN_N.

Referenced by exynos_dp_init_dp().

Definition at line 1099 of file dp_lowlevel.c.

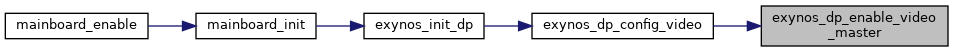

References dp_regs, lread32, lwrite32, exynos_dp::soc_general_ctl, VIDEO_MASTER_MODE_EN, VIDEO_MODE_MASK, VIDEO_MODE_MASTER_MODE, and VIDEO_MODE_SLAVE_MODE.

Referenced by exynos_dp_config_video().

Definition at line 62 of file dp_lowlevel.c.

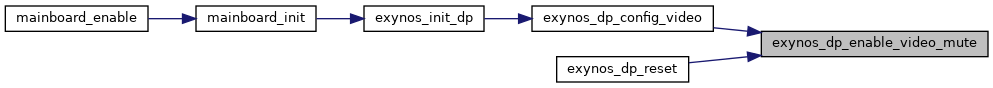

References dp_regs, lread32, lwrite32, exynos_dp::video_ctl1, and VIDEO_MUTE_MASK.

Referenced by exynos_dp_config_video(), and exynos_dp_reset().

Definition at line 861 of file dp_lowlevel.c.

References dp_regs, exynos_dp::lane_count_set, and lread32.

Referenced by exynos_dp_process_equalizer_training().

Definition at line 870 of file dp_lowlevel.c.

References DP_LANE_CNT_4, dp_regs, exynos_dp::ln0_link_training_ctl, exynos_dp::ln1_link_training_ctl, exynos_dp::ln2_link_training_ctl, exynos_dp::ln3_link_training_ctl, and lread32.

Referenced by exynos_dp_process_clock_recovery().

Definition at line 839 of file dp_lowlevel.c.

References dp_regs, exynos_dp::link_bw_set, and lread32.

Referenced by exynos_dp_process_equalizer_training().

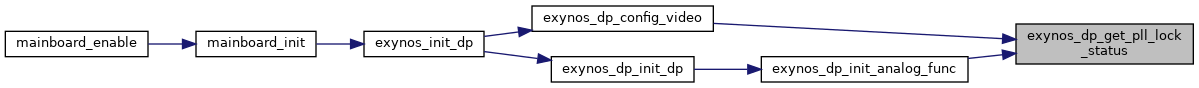

Definition at line 241 of file dp_lowlevel.c.

References exynos_dp::debug_ctl, dp_regs, lread32, PLL_LOCK, PLL_LOCKED, and PLL_UNLOCKED.

Referenced by exynos_dp_config_video(), and exynos_dp_init_analog_func().

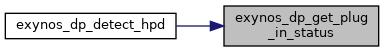

Definition at line 389 of file dp_lowlevel.c.

References dp_regs, HPD_STATUS, lread32, and exynos_dp::sys_ctl3.

Referenced by exynos_dp_detect_hpd().

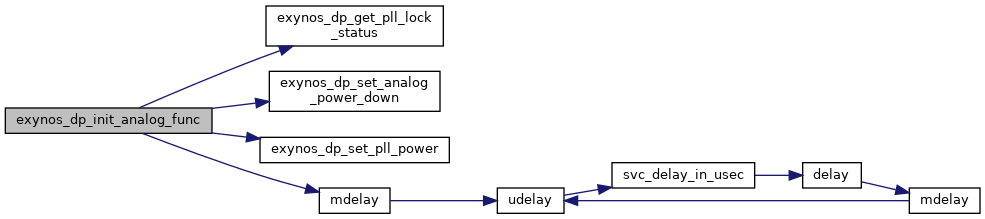

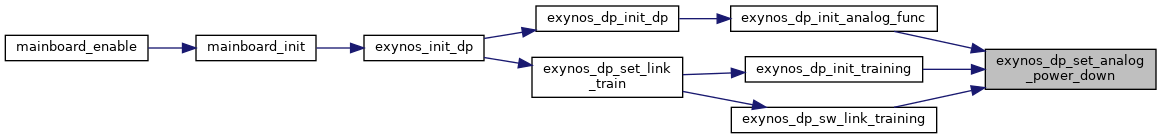

| int exynos_dp_init_analog_func | ( | void | ) |

Definition at line 266 of file dp_lowlevel.c.

References AUX_FUNC_EN_N, BIOS_DEBUG, BIOS_ERR, exynos_dp::common_int_sta1, exynos_dp::debug_ctl, DP_DISABLE, DP_ENABLE, DP_PLL_RESET, dp_regs, exynos_dp_get_pll_lock_status(), exynos_dp_set_analog_power_down(), exynos_dp_set_pll_power(), EXYNOS_DP_SUCCESS, F_PLL_LOCK, exynos_dp::func_en2, lread32, LS_CLK_DOMAIN_FUNC_EN_N, lwrite32, mdelay(), exynos_dp::pll_ctl, PLL_LOCK_CHG, PLL_LOCK_CTRL, PLL_UNLOCKED, POWER_ALL, printk, and SERDES_FIFO_FUNC_EN_N.

Referenced by exynos_dp_init_dp().

Definition at line 343 of file dp_lowlevel.c.

References AUX_BIT_PERIOD_EXPECTED_DELAY, exynos_dp::aux_ch_defer_ctl, AUX_ERR, AUX_FUNC_EN_N, AUX_HW_RETRY_COUNT_SEL, exynos_dp::aux_hw_retry_ctl, AUX_HW_RETRY_INTERVAL_600_MICROSECONDS, DEFER_COUNT, DEFER_CTRL_EN, dp_regs, exynos_dp_reset_aux(), exynos_dp::func_en2, exynos_dp::int_sta, lread32, lwrite32, and RPLY_RECEIV.

Referenced by exynos_dp_init_dp().

Definition at line 317 of file dp_lowlevel.c.

References exynos_dp::common_int_sta4, dp_regs, F_HPD, HOTPLUG_CHG, HPD_CTRL, HPD_LOST, INT_HPD, exynos_dp::int_sta, lread32, lwrite32, PLUG, and exynos_dp::sys_ctl3.

Referenced by exynos_dp_init_dp().

| int exynos_dp_init_video | ( | void | ) |

Definition at line 971 of file dp_lowlevel.c.

References exynos_dp::common_int_sta1, DET_CTRL, dp_regs, lwrite32, exynos_dp::sys_ctl1, VID_CLK_CHG, VID_FORMAT_CHG, and VSYNC_DET.

Referenced by exynos_init_dp().

Definition at line 1039 of file dp_lowlevel.c.

References BIOS_DEBUG, DET_STA, dp_regs, EXYNOS_DP_SUCCESS, lread32, lwrite32, printk, and exynos_dp::sys_ctl1.

Referenced by exynos_dp_config_video().

Definition at line 1125 of file dp_lowlevel.c.

References dp_regs, EXYNOS_DP_SUCCESS, lread32, lwrite32, STRM_VALID, and exynos_dp::sys_ctl3.

Referenced by exynos_dp_config_video().

Definition at line 502 of file dp_lowlevel.c.

References AUX_ADDR_15_8, exynos_dp::aux_addr_15_8, AUX_ADDR_19_16, exynos_dp::aux_addr_19_16, AUX_ADDR_7_0, exynos_dp::aux_addr_7_0, exynos_dp::aux_ch_ctl1, AUX_TX_COMM_DP_TRANSACTION, AUX_TX_COMM_READ, BIOS_DEBUG, BUF_CLR, exynos_dp::buf_data0, exynos_dp::buffer_data_ctl, dp_regs, exynos_dp_start_aux_transaction(), EXYNOS_DP_SUCCESS, lread32, lwrite32, and printk.

Referenced by exynos_dp_enable_rx_to_enhanced_mode(), exynos_dp_enable_scramble(), exynos_dp_process_equalizer_training(), exynos_dp_read_dpcd_adj_req(), and exynos_dp_read_edid().

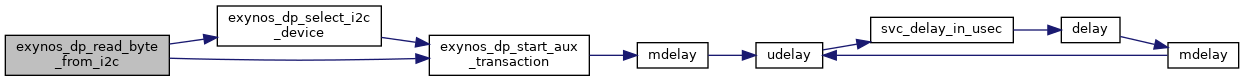

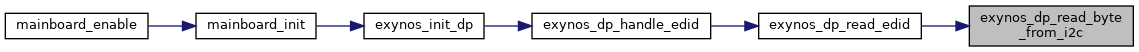

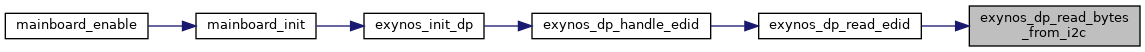

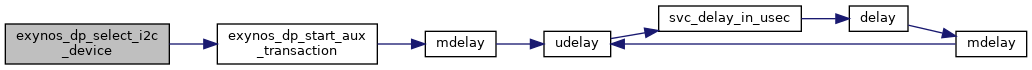

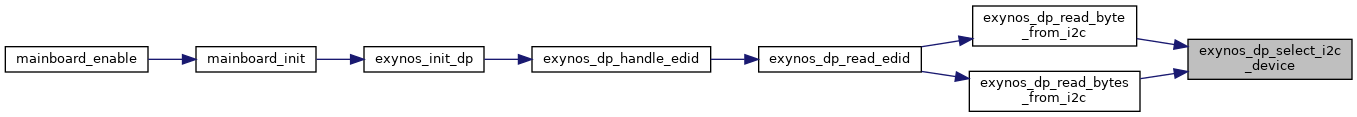

Definition at line 703 of file dp_lowlevel.c.

References exynos_dp::aux_ch_ctl1, AUX_TX_COMM_I2C_TRANSACTION, AUX_TX_COMM_READ, BIOS_DEBUG, BUF_CLR, exynos_dp::buf_data0, exynos_dp::buffer_data_ctl, dp_regs, exynos_dp_select_i2c_device(), exynos_dp_start_aux_transaction(), EXYNOS_DP_SUCCESS, lread32, lwrite32, and printk.

Referenced by exynos_dp_read_edid().

Definition at line 605 of file dp_lowlevel.c.

References AUX_ADDR_15_8, exynos_dp::aux_addr_15_8, AUX_ADDR_19_16, exynos_dp::aux_addr_19_16, AUX_ADDR_7_0, exynos_dp::aux_addr_7_0, exynos_dp::aux_ch_ctl1, AUX_LENGTH, AUX_TX_COMM_DP_TRANSACTION, AUX_TX_COMM_READ, BIOS_ERR, BUF_CLR, exynos_dp::buf_data0, exynos_dp::buffer_data_ctl, count, dp_regs, exynos_dp_start_aux_transaction(), EXYNOS_DP_SUCCESS, lread32, lwrite32, and printk.

Referenced by exynos_dp_handle_edid(), and exynos_dp_read_dpcd_lane_stat().

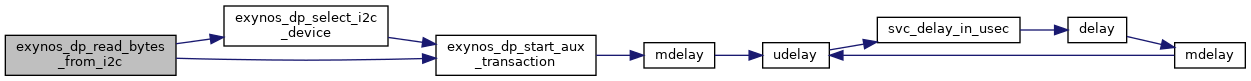

Definition at line 745 of file dp_lowlevel.c.

References ADDR_ONLY, exynos_dp::aux_ch_ctl1, exynos_dp::aux_ch_ctl2, AUX_LENGTH, exynos_dp::aux_rx_comm, AUX_RX_COMM_AUX_DEFER, AUX_RX_COMM_I2C_DEFER, AUX_TX_COMM_I2C_TRANSACTION, AUX_TX_COMM_READ, BIOS_ERR, BUF_CLR, exynos_dp::buf_data0, exynos_dp::buffer_data_ctl, count, dp_regs, exynos_dp_select_i2c_device(), exynos_dp_start_aux_transaction(), EXYNOS_DP_SUCCESS, lread32, lwrite32, and printk.

Referenced by exynos_dp_read_edid().

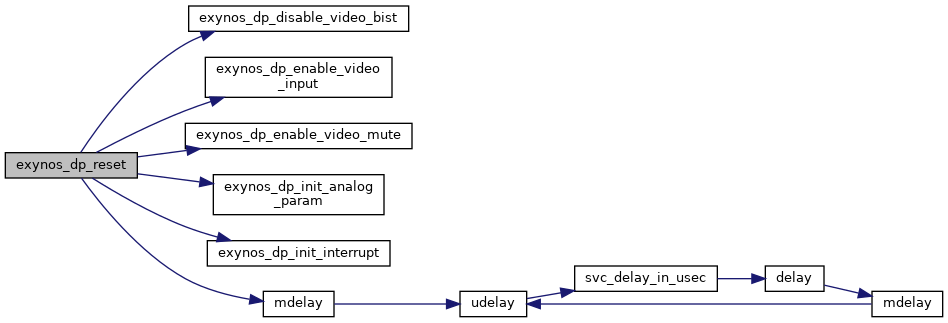

Definition at line 150 of file dp_lowlevel.c.

References AUD_FIFO_FUNC_EN_N, AUD_FUNC_EN_N, DP_DISABLE, dp_regs, exynos_dp_disable_video_bist(), exynos_dp_enable_video_input(), exynos_dp_enable_video_mute(), exynos_dp_init_analog_param(), exynos_dp_init_interrupt(), exynos_dp::func_en1, exynos_dp::func_en2, HDCP_FUNC_EN_N, lwrite32, MASTER_VID_FUNC_EN_N, mdelay(), RESET_DP_TX, SLAVE_VID_FUNC_EN_N, SW_FUNC_EN_N, and exynos_dp::tx_sw_reset.

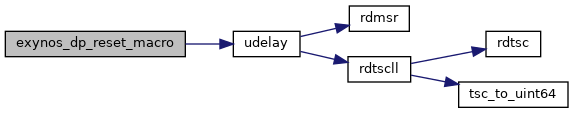

Definition at line 813 of file dp_lowlevel.c.

References dp_regs, lread32, lwrite32, MACRO_RST, exynos_dp::phy_test, and udelay().

Referenced by exynos_dp_init_training().

Definition at line 671 of file dp_lowlevel.c.

References exynos_dp::aux_addr_15_8, exynos_dp::aux_addr_19_16, exynos_dp::aux_addr_7_0, exynos_dp::aux_ch_ctl1, AUX_TX_COMM_I2C_TRANSACTION, AUX_TX_COMM_MOT, AUX_TX_COMM_WRITE, BIOS_DEBUG, exynos_dp::buf_data0, dp_regs, exynos_dp_start_aux_transaction(), lwrite32, and printk.

Referenced by exynos_dp_read_byte_from_i2c(), and exynos_dp_read_bytes_from_i2c().

Definition at line 188 of file dp_lowlevel.c.

References ANALOG_TOTAL, AUX_BLOCK, AUX_PD, BIOS_ERR, CH0_BLOCK, CH0_PD, CH1_BLOCK, CH1_PD, CH2_BLOCK, CH2_PD, CH3_BLOCK, CH3_PD, dp_regs, lread32, lwrite32, exynos_dp::phy_pd, PHY_PD, POWER_ALL, and printk.

Referenced by exynos_dp_init_analog_func(), exynos_dp_init_training(), and exynos_dp_sw_link_training().

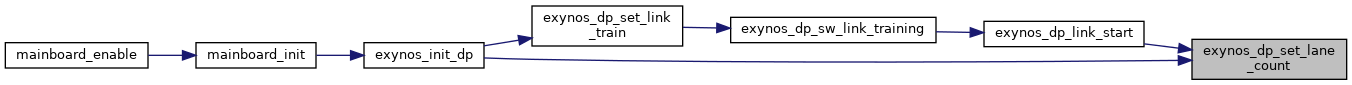

Definition at line 850 of file dp_lowlevel.c.

References count, DP_LANE_CNT_1, DP_LANE_CNT_2, DP_LANE_CNT_4, dp_regs, exynos_dp::lane_count_set, and lwrite32.

Referenced by exynos_dp_link_start(), and exynos_init_dp().

Definition at line 895 of file dp_lowlevel.c.

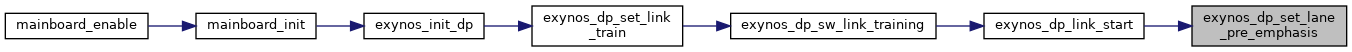

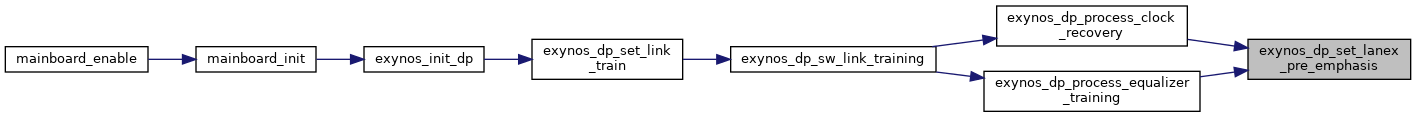

References DP_LANE_CNT_4, dp_regs, exynos_dp::ln0_link_training_ctl, exynos_dp::ln1_link_training_ctl, exynos_dp::ln2_link_training_ctl, exynos_dp::ln3_link_training_ctl, lwrite32, PRE_EMPHASIS_SET_0_SHIFT, PRE_EMPHASIS_SET_1_SHIFT, PRE_EMPHASIS_SET_2_SHIFT, and PRE_EMPHASIS_SET_3_SHIFT.

Referenced by exynos_dp_link_start().

Definition at line 882 of file dp_lowlevel.c.

References DP_LANE_CNT_4, dp_regs, exynos_dp::ln0_link_training_ctl, exynos_dp::ln1_link_training_ctl, exynos_dp::ln2_link_training_ctl, exynos_dp::ln3_link_training_ctl, and lwrite32.

Referenced by exynos_dp_process_clock_recovery(), and exynos_dp_process_equalizer_training().

Definition at line 828 of file dp_lowlevel.c.

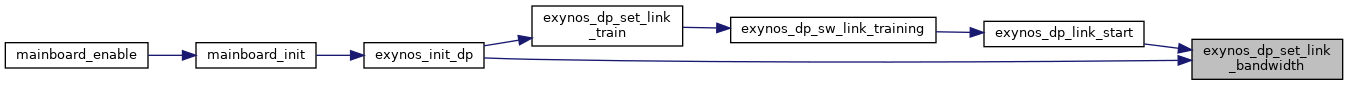

References DP_LANE_BW_1_62, DP_LANE_BW_2_70, dp_regs, exynos_dp::link_bw_set, and lwrite32.

Referenced by exynos_dp_link_start(), and exynos_init_dp().

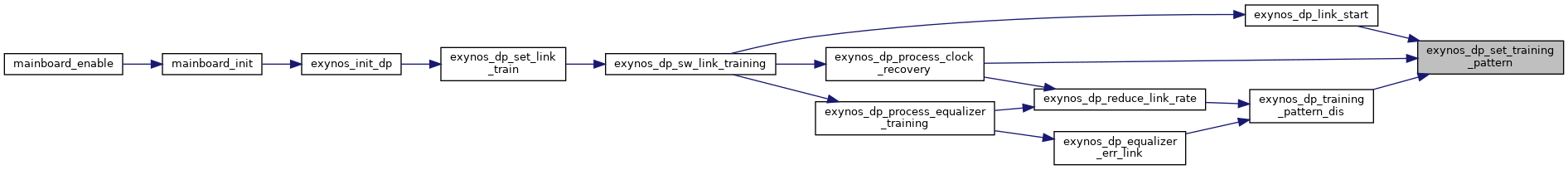

Definition at line 918 of file dp_lowlevel.c.

References D10_2, DP_NONE, dp_regs, LINK_QUAL_PATTERN_SET_D10_2, LINK_QUAL_PATTERN_SET_DISABLE, LINK_QUAL_PATTERN_SET_PRBS7, lwrite32, pattern, PRBS7, SCRAMBLING_DISABLE, SCRAMBLING_ENABLE, SW_TRAINING_PATTERN_SET_NORMAL, SW_TRAINING_PATTERN_SET_PTN1, SW_TRAINING_PATTERN_SET_PTN2, TRAINING_PTN1, TRAINING_PTN2, and exynos_dp::training_ptn_set.

Referenced by exynos_dp_link_start(), exynos_dp_process_clock_recovery(), and exynos_dp_training_pattern_dis().

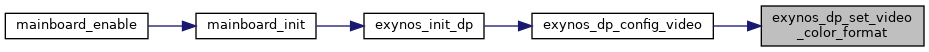

| void exynos_dp_set_video_color_format | ( | struct edp_video_info * | video_info | ) |

Definition at line 1019 of file dp_lowlevel.c.

References video_info::color_depth, video_info::color_space, dp_regs, video_info::dynamic_range, IN_BPC_SHIFT, IN_COLOR_F_SHIFT, IN_D_RANGE_SHIFT, IN_YC_COEFFI_ITU601, IN_YC_COEFFI_ITU709, IN_YC_COEFFI_MASK, lread32, lwrite32, exynos_dp::video_ctl2, exynos_dp::video_ctl3, and video_info::ycbcr_coeff.

Referenced by exynos_dp_config_video().

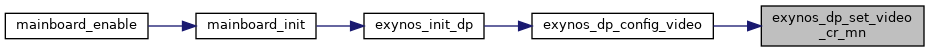

Definition at line 1057 of file dp_lowlevel.c.

References dp_regs, FIX_M_VID, lread32, lwrite32, exynos_dp::m_vid0, M_VID0_CFG, exynos_dp::m_vid1, M_VID1_CFG, exynos_dp::m_vid2, M_VID2_CFG, exynos_dp::n_vid0, N_VID0_CFG, exynos_dp::n_vid1, N_VID1_CFG, exynos_dp::n_vid2, N_VID2_CFG, REGISTER_M, exynos_dp::sys_ctl4, and type.

Referenced by exynos_dp_config_video().

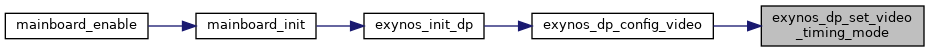

Definition at line 1086 of file dp_lowlevel.c.

References dp_regs, FORMAT_SEL, lread32, lwrite32, type, exynos_dp::video_ctl10, and VIDEO_TIMING_FROM_CAPTURE.

Referenced by exynos_dp_config_video().

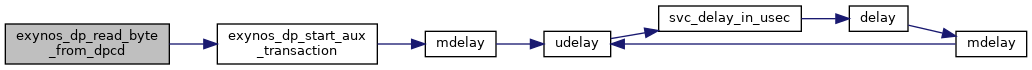

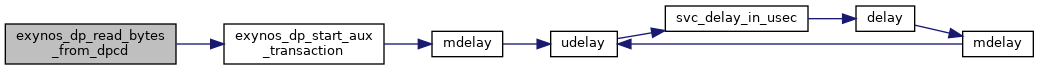

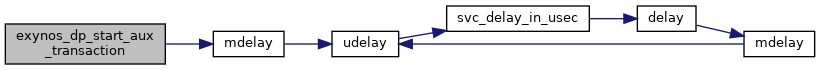

Definition at line 416 of file dp_lowlevel.c.

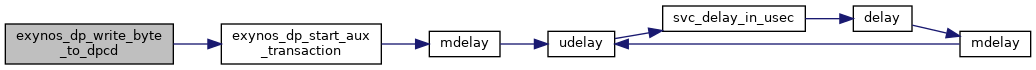

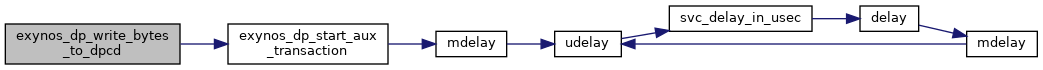

References exynos_dp::aux_ch_ctl2, exynos_dp::aux_ch_sta, AUX_EN, AUX_ERR, AUX_STATUS_MASK, BIOS_DEBUG, BIOS_ERR, dp_regs, EXYNOS_DP_SUCCESS, exynos_dp::int_sta, lread32, lwrite32, mdelay(), printk, and RPLY_RECEIV.

Referenced by exynos_dp_read_byte_from_dpcd(), exynos_dp_read_byte_from_i2c(), exynos_dp_read_bytes_from_dpcd(), exynos_dp_read_bytes_from_i2c(), exynos_dp_select_i2c_device(), exynos_dp_write_byte_to_dpcd(), and exynos_dp_write_bytes_to_dpcd().

Definition at line 1115 of file dp_lowlevel.c.

References dp_regs, lread32, lwrite32, exynos_dp::video_ctl1, and VIDEO_EN.

Referenced by exynos_dp_config_video().

Definition at line 464 of file dp_lowlevel.c.

References AUX_ADDR_15_8, exynos_dp::aux_addr_15_8, AUX_ADDR_19_16, exynos_dp::aux_addr_19_16, AUX_ADDR_7_0, exynos_dp::aux_addr_7_0, exynos_dp::aux_ch_ctl1, AUX_TX_COMM_DP_TRANSACTION, AUX_TX_COMM_WRITE, BIOS_ERR, BUF_CLR, exynos_dp::buf_data0, exynos_dp::buffer_data_ctl, dp_regs, exynos_dp_start_aux_transaction(), EXYNOS_DP_SUCCESS, lwrite32, and printk.

Referenced by exynos_dp_enable_rx_to_enhanced_mode(), exynos_dp_enable_scramble(), exynos_dp_link_start(), exynos_dp_read_edid(), and exynos_dp_training_pattern_dis().

Definition at line 540 of file dp_lowlevel.c.

References AUX_ADDR_15_8, exynos_dp::aux_addr_15_8, AUX_ADDR_19_16, exynos_dp::aux_addr_19_16, AUX_ADDR_7_0, exynos_dp::aux_addr_7_0, exynos_dp::aux_ch_ctl1, AUX_LENGTH, AUX_TX_COMM_DP_TRANSACTION, AUX_TX_COMM_WRITE, BIOS_ERR, BUF_CLR, exynos_dp::buf_data0, exynos_dp::buffer_data_ctl, count, dp_regs, exynos_dp_start_aux_transaction(), EXYNOS_DP_SUCCESS, lwrite32, and printk.

Referenced by exynos_dp_link_start(), exynos_dp_process_clock_recovery(), and exynos_dp_process_equalizer_training().

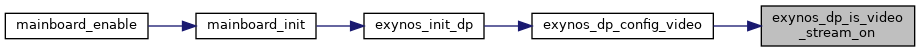

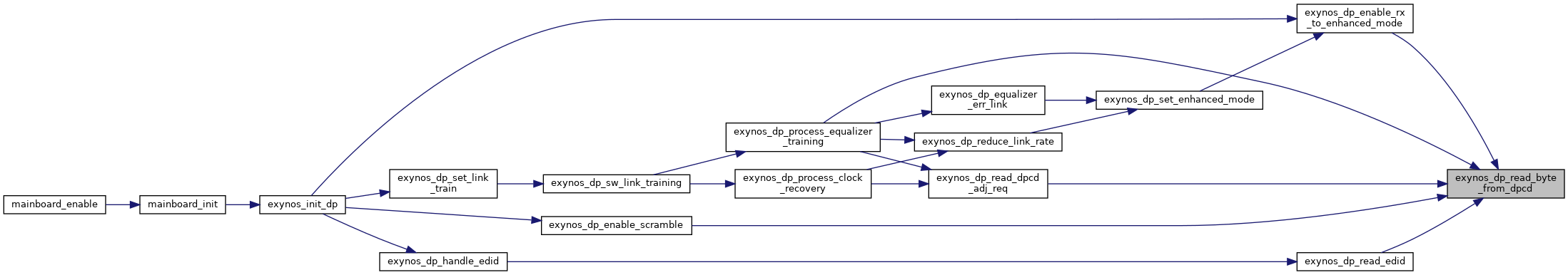

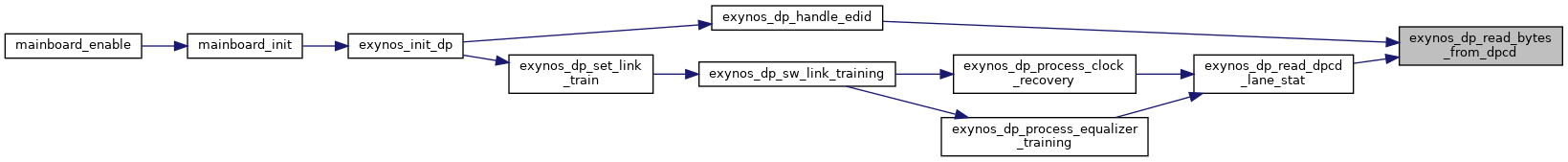

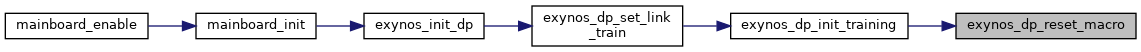

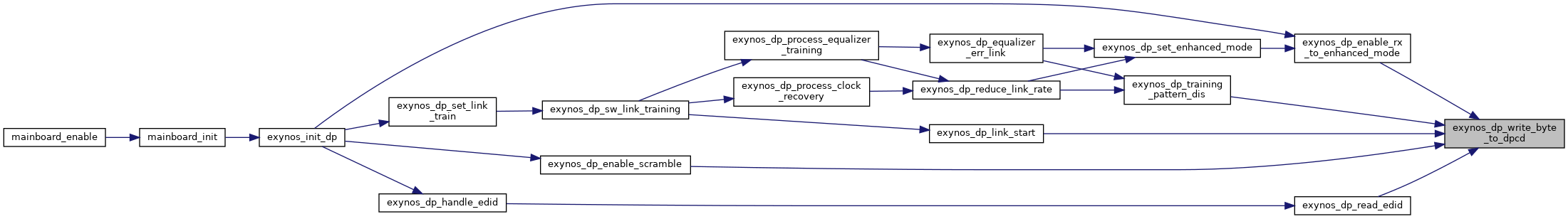

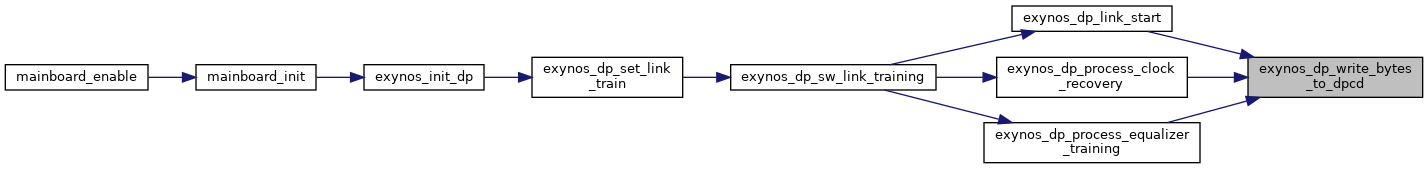

| int exynos_init_dp | ( | struct edp_device_info * | edp_info | ) |

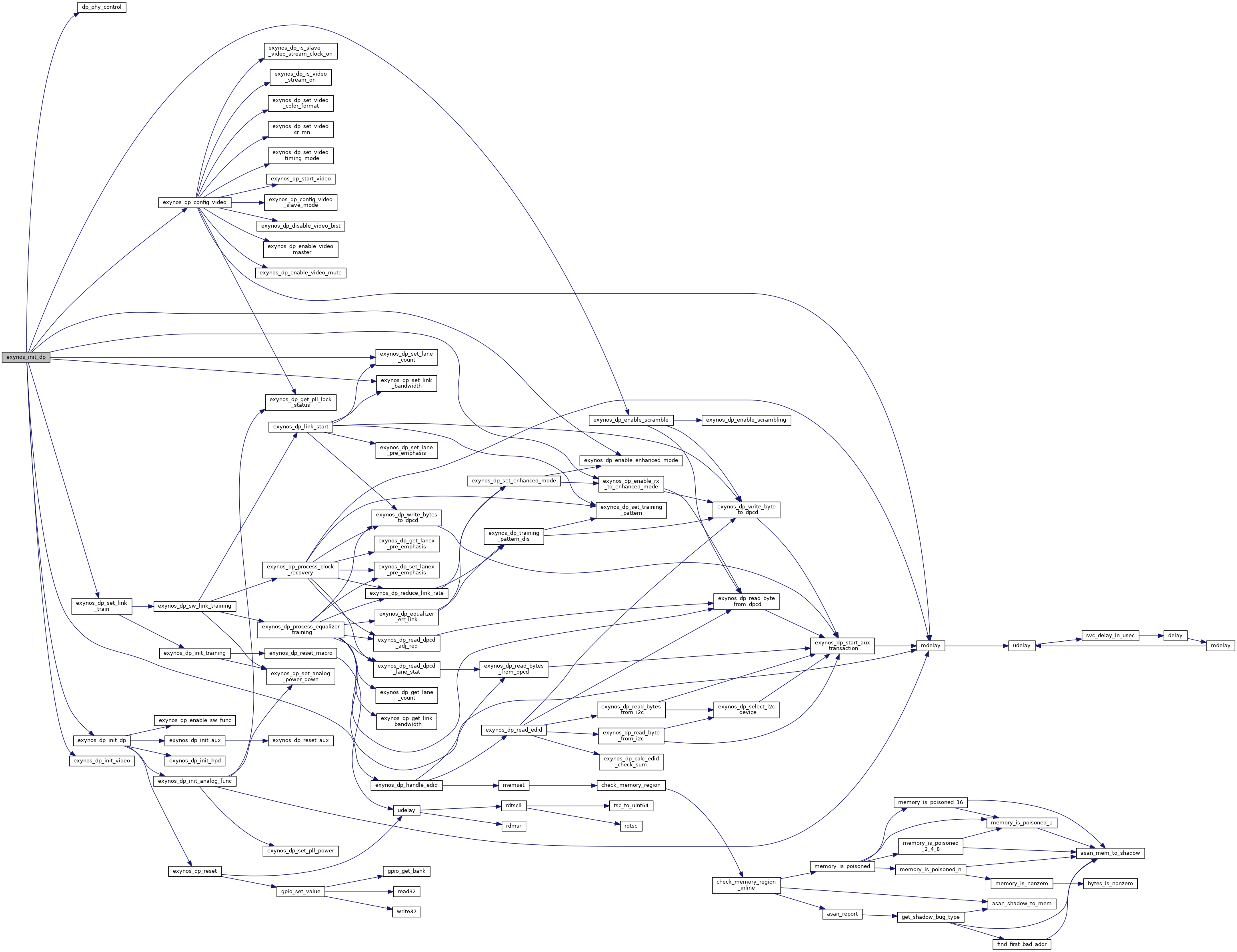

Definition at line 841 of file dp.c.

References BIOS_DEBUG, BIOS_ERR, DP_ENABLE, dp_phy_control(), exynos_dp_config_video(), exynos_dp_enable_enhanced_mode(), exynos_dp_enable_rx_to_enhanced_mode(), exynos_dp_enable_scramble(), exynos_dp_handle_edid(), exynos_dp_init_dp(), exynos_dp_init_video(), exynos_dp_set_lane_count(), exynos_dp_set_link_bandwidth(), exynos_dp_set_link_train(), EXYNOS_DP_SUCCESS, edp_device_info::lane_bw, edp_device_info::lane_cnt, and printk.

Referenced by mainboard_init().

| void exynos_set_dp_platform_data | ( | struct exynos_dp_platform_data * | pd | ) |

|

static |

|

static |