|

coreboot

coreboot is an Open Source project aimed at replacing the proprietary BIOS found in most computers.

|

|

coreboot

coreboot is an Open Source project aimed at replacing the proprietary BIOS found in most computers.

|

#include <edid.h>

Go to the source code of this file.

Data Structures | |

| struct | rk_edp_regs |

| struct | link_train |

| struct | rk_edp |

Macros | |

| #define | VID_CAP_FUNC_EN_N (0x1 << 6) |

| #define | VID_FIFO_FUNC_EN_N (0x1 << 5) |

| #define | AUD_FIFO_FUNC_EN_N (0x1 << 4) |

| #define | AUD_FUNC_EN_N (0x1 << 3) |

| #define | HDCP_FUNC_EN_N (0x1 << 2) |

| #define | SW_FUNC_EN_N (0x1 << 0) |

| #define | SSC_FUNC_EN_N (0x1 << 7) |

| #define | AUX_FUNC_EN_N (0x1 << 2) |

| #define | SERDES_FIFO_FUNC_EN_N (0x1 << 1) |

| #define | LS_CLK_DOMAIN_FUNC_EN_N (0x1 << 0) |

| #define | VIDEO_EN (0x1 << 7) |

| #define | VIDEO_MUTE (0x1 << 6) |

| #define | IN_D_RANGE_MASK (0x1 << 7) |

| #define | IN_D_RANGE_SHIFT (7) |

| #define | IN_D_RANGE_CEA (0x1 << 7) |

| #define | IN_D_RANGE_VESA (0x0 << 7) |

| #define | IN_BPC_MASK (0x7 << 4) |

| #define | IN_BPC_SHIFT (4) |

| #define | IN_BPC_12_BITS (0x3 << 4) |

| #define | IN_BPC_10_BITS (0x2 << 4) |

| #define | IN_BPC_8_BITS (0x1 << 4) |

| #define | IN_BPC_6_BITS (0x0 << 4) |

| #define | IN_COLOR_F_MASK (0x3 << 0) |

| #define | IN_COLOR_F_SHIFT (0) |

| #define | IN_COLOR_F_YCBCR444 (0x2 << 0) |

| #define | IN_COLOR_F_YCBCR422 (0x1 << 0) |

| #define | IN_COLOR_F_RGB (0x0 << 0) |

| #define | IN_YC_COEFFI_MASK (0x1 << 7) |

| #define | IN_YC_COEFFI_SHIFT (7) |

| #define | IN_YC_COEFFI_ITU709 (0x1 << 7) |

| #define | IN_YC_COEFFI_ITU601 (0x0 << 7) |

| #define | VID_CHK_UPDATE_TYPE_MASK (0x1 << 4) |

| #define | VID_CHK_UPDATE_TYPE_SHIFT (4) |

| #define | VID_CHK_UPDATE_TYPE_1 (0x1 << 4) |

| #define | VID_CHK_UPDATE_TYPE_0 (0x0 << 4) |

| #define | BIST_EN (0x1 << 3) |

| #define | BIST_WH_64 (0x1 << 2) |

| #define | BIST_WH_32 (0x0 << 2) |

| #define | BIST_TYPE_COLR_BAR (0x0 << 0) |

| #define | BIST_TYPE_GRAY_BAR (0x1 << 0) |

| #define | BIST_TYPE_MOBILE_BAR (0x2 << 0) |

| #define | VID_HRES_TH(x) (((x) & 0xf) << 4) |

| #define | VID_VRES_TH(x) (((x) & 0xf) << 0) |

| #define | F_SEL (0x1 << 4) |

| #define | INTERACE_SCAN_CFG (0x1 << 2) |

| #define | INTERACD_SCAN_CFG_OFFSET 2 |

| #define | VSYNC_POLARITY_CFG (0x1 << 1) |

| #define | VSYNC_POLARITY_CFG_OFFSET 1 |

| #define | HSYNC_POLARITY_CFG (0x1 << 0) |

| #define | HSYNC_POLARITY_CFG_OFFSET 0 |

| #define | PD_INC_BG (0x1 << 7) |

| #define | PD_EXP_BG (0x1 << 6) |

| #define | PD_AUX (0x1 << 5) |

| #define | PD_PLL (0x1 << 4) |

| #define | PD_CH3 (0x1 << 3) |

| #define | PD_CH2 (0x1 << 2) |

| #define | PD_CH1 (0x1 << 1) |

| #define | PD_CH0 (0x1 << 0) |

| #define | LANE3_MAP_LOGIC_LANE_0 (0x0 << 6) |

| #define | LANE3_MAP_LOGIC_LANE_1 (0x1 << 6) |

| #define | LANE3_MAP_LOGIC_LANE_2 (0x2 << 6) |

| #define | LANE3_MAP_LOGIC_LANE_3 (0x3 << 6) |

| #define | LANE2_MAP_LOGIC_LANE_0 (0x0 << 4) |

| #define | LANE2_MAP_LOGIC_LANE_1 (0x1 << 4) |

| #define | LANE2_MAP_LOGIC_LANE_2 (0x2 << 4) |

| #define | LANE2_MAP_LOGIC_LANE_3 (0x3 << 4) |

| #define | LANE1_MAP_LOGIC_LANE_0 (0x0 << 2) |

| #define | LANE1_MAP_LOGIC_LANE_1 (0x1 << 2) |

| #define | LANE1_MAP_LOGIC_LANE_2 (0x2 << 2) |

| #define | LANE1_MAP_LOGIC_LANE_3 (0x3 << 2) |

| #define | LANE0_MAP_LOGIC_LANE_0 (0x0 << 0) |

| #define | LANE0_MAP_LOGIC_LANE_1 (0x1 << 0) |

| #define | LANE0_MAP_LOGIC_LANE_2 (0x2 << 0) |

| #define | LANE0_MAP_LOGIC_LANE_3 (0x3 << 0) |

| #define | SEL_24M (0x1 << 3) |

| #define | VSYNC_DET (0x1 << 7) |

| #define | PLL_LOCK_CHG (0x1 << 6) |

| #define | SPDIF_ERR (0x1 << 5) |

| #define | SPDIF_UNSTBL (0x1 << 4) |

| #define | VID_FORMAT_CHG (0x1 << 3) |

| #define | AUD_CLK_CHG (0x1 << 2) |

| #define | VID_CLK_CHG (0x1 << 1) |

| #define | SW_INT (0x1 << 0) |

| #define | ENC_EN_CHG (0x1 << 6) |

| #define | HW_BKSV_RDY (0x1 << 3) |

| #define | HW_SHA_DONE (0x1 << 2) |

| #define | HW_AUTH_STATE_CHG (0x1 << 1) |

| #define | HW_AUTH_DONE (0x1 << 0) |

| #define | AFIFO_UNDER (0x1 << 7) |

| #define | AFIFO_OVER (0x1 << 6) |

| #define | R0_CHK_FLAG (0x1 << 5) |

| #define | PSR_ACTIVE (0x1 << 7) |

| #define | PSR_INACTIVE (0x1 << 6) |

| #define | SPDIF_BI_PHASE_ERR (0x1 << 5) |

| #define | HOTPLUG_CHG (0x1 << 2) |

| #define | HPD_LOST (0x1 << 1) |

| #define | PLUG (0x1 << 0) |

| #define | INT_HPD (0x1 << 6) |

| #define | HW_LT_DONE (0x1 << 5) |

| #define | SINK_LOST (0x1 << 3) |

| #define | LINK_LOST (0x1 << 2) |

| #define | RPLY_RECEIV (0x1 << 1) |

| #define | AUX_ERR (0x1 << 0) |

| #define | SOFT_INT_CTRL (0x1 << 2) |

| #define | INT_POL (0x1 << 0) |

| #define | DET_STA (0x1 << 2) |

| #define | FORCE_DET (0x1 << 1) |

| #define | DET_CTRL (0x1 << 0) |

| #define | CHA_CRI(x) (((x) & 0xf) << 4) |

| #define | CHA_STA (0x1 << 2) |

| #define | FORCE_CHA (0x1 << 1) |

| #define | CHA_CTRL (0x1 << 0) |

| #define | HPD_STATUS (0x1 << 6) |

| #define | F_HPD (0x1 << 5) |

| #define | HPD_CTRL (0x1 << 4) |

| #define | HDCP_RDY (0x1 << 3) |

| #define | STRM_VALID (0x1 << 2) |

| #define | F_VALID (0x1 << 1) |

| #define | VALID_CTRL (0x1 << 0) |

| #define | FIX_M_AUD (0x1 << 4) |

| #define | ENHANCED (0x1 << 3) |

| #define | FIX_M_VID (0x1 << 2) |

| #define | M_VID_UPDATE_CTRL (0x3 << 0) |

| #define | LDO_OUTPUT_V_SEL_145 (2 << 6) |

| #define | KVCO_DEFALUT (1 << 4) |

| #define | CHG_PUMP_CUR_SEL_5US (1 << 2) |

| #define | V2L_CUR_SEL_1MA (1 << 0) |

| #define | LOCK_DET_CNT_SEL_256 (2 << 5) |

| #define | LOOP_FILTER_RESET (0 << 4) |

| #define | PALL_SSC_RESET (0 << 3) |

| #define | LOCK_DET_BYPASS (0 << 2) |

| #define | PLL_LOCK_DET_MODE (0 << 1) |

| #define | PLL_LOCK_DET_FORCE (0 << 0) |

| #define | REGULATOR_V_SEL_950MV (2 << 4) |

| #define | STANDBY_CUR_SEL (0 << 3) |

| #define | CHG_PUMP_INOUT_CTRL_1200MV (1 << 1) |

| #define | CHG_PUMP_INPUT_CTRL_OP (0 << 0) |

| #define | SSC_OFFSET (0 << 6) |

| #define | SSC_MODE (1 << 4) |

| #define | SSC_DEPTH (9 << 0) |

| #define | TX_SWING_PRE_EMP_MODE (1 << 7) |

| #define | PRE_DRIVER_PW_CTRL1 (0 << 5) |

| #define | LP_MODE_CLK_REGULATOR (0 << 4) |

| #define | RESISTOR_MSB_CTRL (0 << 3) |

| #define | RESISTOR_CTRL (7 << 0) |

| #define | DP_AUX_COMMON_MODE (0 << 4) |

| #define | DP_AUX_EN (0 << 3) |

| #define | AUX_TERM_50OHM (3 << 0) |

| #define | DP_BG_OUT_SEL (4 << 4) |

| #define | DP_DB_CUR_CTRL (0 << 3) |

| #define | DP_BG_SEL (1 << 2) |

| #define | DP_RESISTOR_TUNE_BG (2 << 0) |

| #define | CH1_CH3_SWING_EMP_CTRL (5 << 4) |

| #define | CH0_CH2_SWING_EMP_CTRL (5 << 0) |

| #define | SCRAMBLING_DISABLE (0x1 << 5) |

| #define | SCRAMBLING_ENABLE (0x0 << 5) |

| #define | LINK_QUAL_PATTERN_SET_MASK (0x7 << 2) |

| #define | LINK_QUAL_PATTERN_SET_HBR2 (0x5 << 2) |

| #define | LINK_QUAL_PATTERN_SET_80BIT (0x4 << 2) |

| #define | LINK_QUAL_PATTERN_SET_PRBS7 (0x3 << 2) |

| #define | LINK_QUAL_PATTERN_SET_D10_2 (0x1 << 2) |

| #define | LINK_QUAL_PATTERN_SET_DISABLE (0x0 << 2) |

| #define | SW_TRAINING_PATTERN_SET_MASK (0x3 << 0) |

| #define | SW_TRAINING_PATTERN_SET_PTN2 (0x2 << 0) |

| #define | SW_TRAINING_PATTERN_SET_PTN1 (0x1 << 0) |

| #define | SW_TRAINING_PATTERN_SET_DISABLE (0x0 << 0) |

| #define | HW_LT_ERR_CODE_MASK 0x70 |

| #define | HW_LT_ERR_CODE_SHIFT 4 |

| #define | HW_LT_EN (0x1 << 0) |

| #define | PLL_LOCK (0x1 << 4) |

| #define | F_PLL_LOCK (0x1 << 3) |

| #define | PLL_LOCK_CTRL (0x1 << 2) |

| #define | POLL_EN (0x1 << 1) |

| #define | PN_INV (0x1 << 0) |

| #define | AUX_BUSY (0x1 << 4) |

| #define | AUX_STATUS_MASK (0xf << 0) |

| #define | DEFER_CTRL_EN (0x1 << 7) |

| #define | DEFER_COUNT(x) (((x) & 0x7f) << 0) |

| #define | AUX_RX_COMM_I2C_DEFER (0x2 << 2) |

| #define | AUX_RX_COMM_AUX_DEFER (0x2 << 0) |

| #define | BUF_CLR (0x1 << 7) |

| #define | BUF_HAVE_DATA (0x1 << 4) |

| #define | BUF_DATA_COUNT(x) (((x) & 0xf) << 0) |

| #define | AUX_LENGTH(x) (((x - 1) & 0xf) << 4) |

| #define | AUX_TX_COMM_MASK (0xf << 0) |

| #define | AUX_TX_COMM_DP_TRANSACTION (0x1 << 3) |

| #define | AUX_TX_COMM_I2C_TRANSACTION (0x0 << 3) |

| #define | AUX_TX_COMM_MOT (0x1 << 2) |

| #define | AUX_TX_COMM_WRITE (0x0 << 0) |

| #define | AUX_TX_COMM_READ (0x1 << 0) |

| #define | PD_AUX_IDLE (0x1 << 3) |

| #define | ADDR_ONLY (0x1 << 1) |

| #define | AUX_EN (0x1 << 0) |

| #define | RST_DP_TX (0x1 << 0) |

| #define | TX_TERMINAL_CTRL_50_OHM (0x1 << 4) |

| #define | DRIVE_DVDD_BIT_1_0625V (0x4 << 5) |

| #define | VCO_BIT_600_MICRO (0x5 << 0) |

| #define | PD_RING_OSC (0x1 << 6) |

| #define | AUX_TERMINAL_CTRL_37_5_OHM (0x0 << 4) |

| #define | AUX_TERMINAL_CTRL_45_OHM (0x1 << 4) |

| #define | AUX_TERMINAL_CTRL_50_OHM (0x2 << 4) |

| #define | AUX_TERMINAL_CTRL_65_OHM (0x3 << 4) |

| #define | TX_CUR1_2X (0x1 << 2) |

| #define | TX_CUR_16_MA (0x3 << 0) |

| #define | DPCD_DPCD_REV (0x0000) |

| #define | DPCD_MAX_LINK_RATE (0x0001) |

| #define | DPCD_MAX_LANE_COUNT (0x0002) |

| #define | DP_MAX_LANE_COUNT_MASK 0x1f |

| #define | DP_TPS3_SUPPORTED (1 << 6) |

| #define | DP_ENHANCED_FRAME_CAP (1 << 7) |

| #define | DPCD_LINK_BW_SET (0x0100) |

| #define | DPCD_LANE_COUNT_SET (0x0101) |

| #define | DPCD_TRAINING_PATTERN_SET (0x0102) |

| #define | DP_TRAINING_PATTERN_DISABLE 0 |

| #define | DP_TRAINING_PATTERN_1 1 |

| #define | DP_TRAINING_PATTERN_2 2 |

| #define | DP_TRAINING_PATTERN_3 3 |

| #define | DP_TRAINING_PATTERN_MASK 0x3 |

| #define | DPCD_TRAINING_LANE0_SET (0x0103) |

| #define | DP_TRAIN_VOLTAGE_SWING_MASK 0x3 |

| #define | DP_TRAIN_VOLTAGE_SWING_SHIFT 0 |

| #define | DP_TRAIN_MAX_SWING_REACHED (1 << 2) |

| #define | DP_TRAIN_VOLTAGE_SWING_400 (0 << 0) |

| #define | DP_TRAIN_VOLTAGE_SWING_600 (1 << 0) |

| #define | DP_TRAIN_VOLTAGE_SWING_800 (2 << 0) |

| #define | DP_TRAIN_VOLTAGE_SWING_1200 (3 << 0) |

| #define | DP_TRAIN_PRE_EMPHASIS_MASK (3 << 3) |

| #define | DP_TRAIN_PRE_EMPHASIS_0 (0 << 3) |

| #define | DP_TRAIN_PRE_EMPHASIS_3_5 (1 << 3) |

| #define | DP_TRAIN_PRE_EMPHASIS_6 (2 << 3) |

| #define | DP_TRAIN_PRE_EMPHASIS_9_5 (3 << 3) |

| #define | DP_TRAIN_PRE_EMPHASIS_SHIFT 3 |

| #define | DP_TRAIN_MAX_PRE_EMPHASIS_REACHED (1 << 5) |

| #define | DPCD_LANE0_1_STATUS (0x0202) |

| #define | DPCD_LANE2_3_STATUS (0x0203) |

| #define | DP_LANE_CR_DONE (1 << 0) |

| #define | DP_LANE_CHANNEL_EQ_DONE (1 << 1) |

| #define | DP_LANE_SYMBOL_LOCKED (1 << 2) |

| #define | DP_CHANNEL_EQ_BITS |

| #define | DPCD_LANE_ALIGN_STATUS_UPDATED (0x0204) |

| #define | DP_INTERLANE_ALIGN_DONE (1 << 0) |

| #define | DP_DOWNSTREAM_PORT_STATUS_CHANGED (1 << 6) |

| #define | DP_LINK_STATUS_UPDATED (1 << 7) |

| #define | DPCD_ADJUST_REQUEST_LANE0_1 (0x0206) |

| #define | DPCD_ADJUST_REQUEST_LANE2_3 (0x0207) |

| #define | DP_ADJUST_VOLTAGE_SWING_LANE0_MASK 0x03 |

| #define | DP_ADJUST_VOLTAGE_SWING_LANE0_SHIFT 0 |

| #define | DP_ADJUST_PRE_EMPHASIS_LANE0_MASK 0x0c |

| #define | DP_ADJUST_PRE_EMPHASIS_LANE0_SHIFT 2 |

| #define | DP_ADJUST_VOLTAGE_SWING_LANE1_MASK 0x30 |

| #define | DP_ADJUST_VOLTAGE_SWING_LANE1_SHIFT 4 |

| #define | DP_ADJUST_PRE_EMPHASIS_LANE1_MASK 0xc0 |

| #define | DP_ADJUST_PRE_EMPHASIS_LANE1_SHIFT 6 |

| #define | DPCD_TEST_REQUEST (0x0218) |

| #define | DPCD_TEST_RESPONSE (0x0260) |

| #define | DPCD_TEST_EDID_CHECKSUM (0x0261) |

| #define | DPCD_LINK_POWER_STATE (0x0600) |

| #define | DP_SET_POWER_D0 0x1 |

| #define | DP_SET_POWER_D3 0x2 |

| #define | DP_SET_POWER_MASK 0x3 |

| #define | AUX_ADDR_7_0(x) (((x) >> 0) & 0xff) |

| #define | AUX_ADDR_15_8(x) (((x) >> 8) & 0xff) |

| #define | AUX_ADDR_19_16(x) (((x) >> 16) & 0x0f) |

| #define | STREAM_ON_TIMEOUT 100 |

| #define | PLL_LOCK_TIMEOUT 10 |

| #define | DP_INIT_TRIES 10 |

| #define | EDID_ADDR 0x50 |

| #define | EDID_LENGTH 0x80 |

| #define | EDID_HEADER 0x00 |

| #define | EDID_EXTENSION_FLAG 0x7e |

Functions | |

| check_member (rk_edp_regs, pll_reg_5, 0xa00) | |

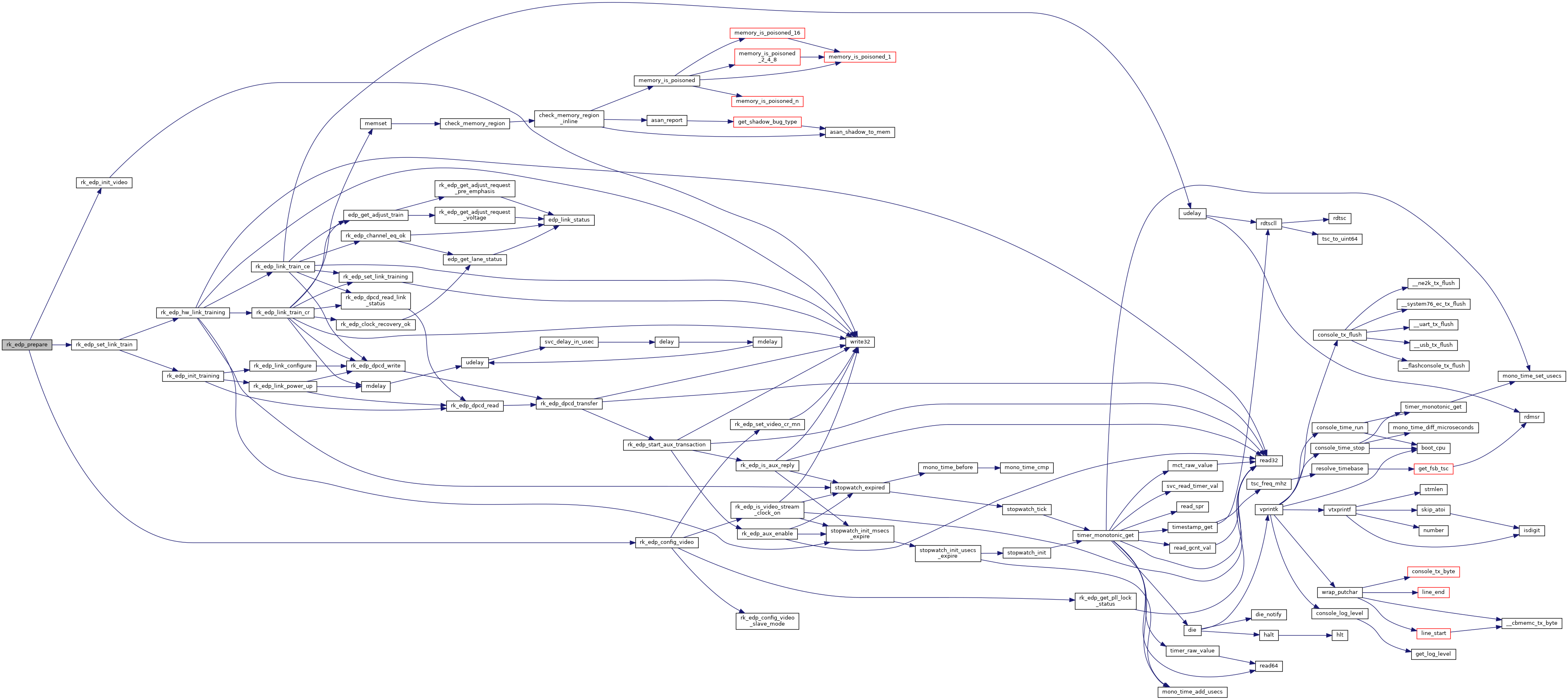

| int | rk_edp_prepare (void) |

| int | rk_edp_enable (void) |

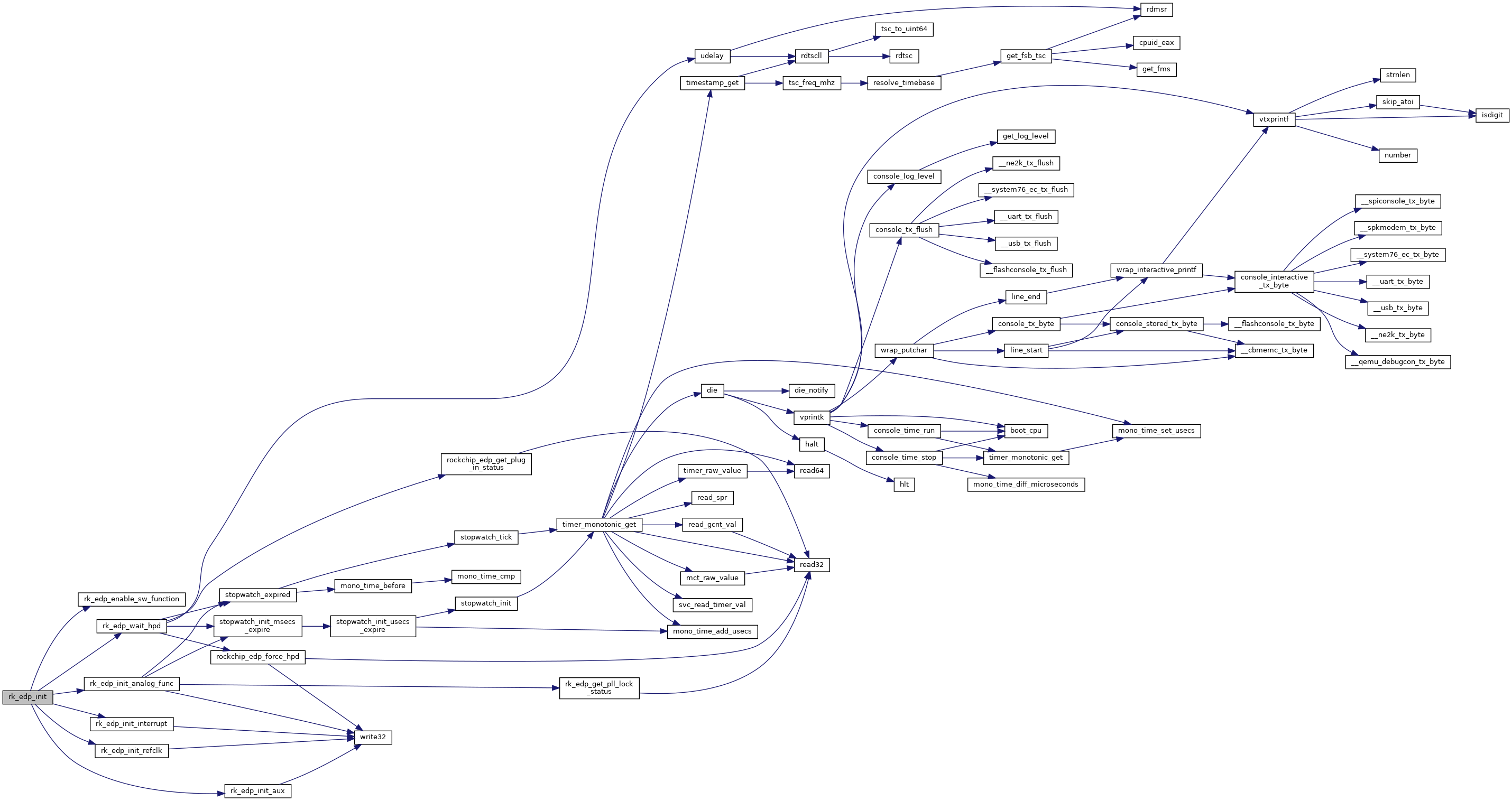

| void | rk_edp_init (void) |

| int | rk_edp_get_edid (struct edid *edid) |

| #define DP_CHANNEL_EQ_BITS |

| enum analog_power_block |

| enum color_coefficient |

| enum color_depth |

| enum color_space |

| enum dp_irq_type |

| enum dpcd_request |

| enum dynamic_range |

| enum link_lane_count_type |

| enum link_rate_type |

| enum link_training_state |

| enum pattern_set |

| enum pll_status |

| enum pre_emphasis_level |

| enum voltage_swing_level |

| check_member | ( | rk_edp_regs | , |

| pll_reg_5 | , | ||

| 0xa00 | |||

| ) |

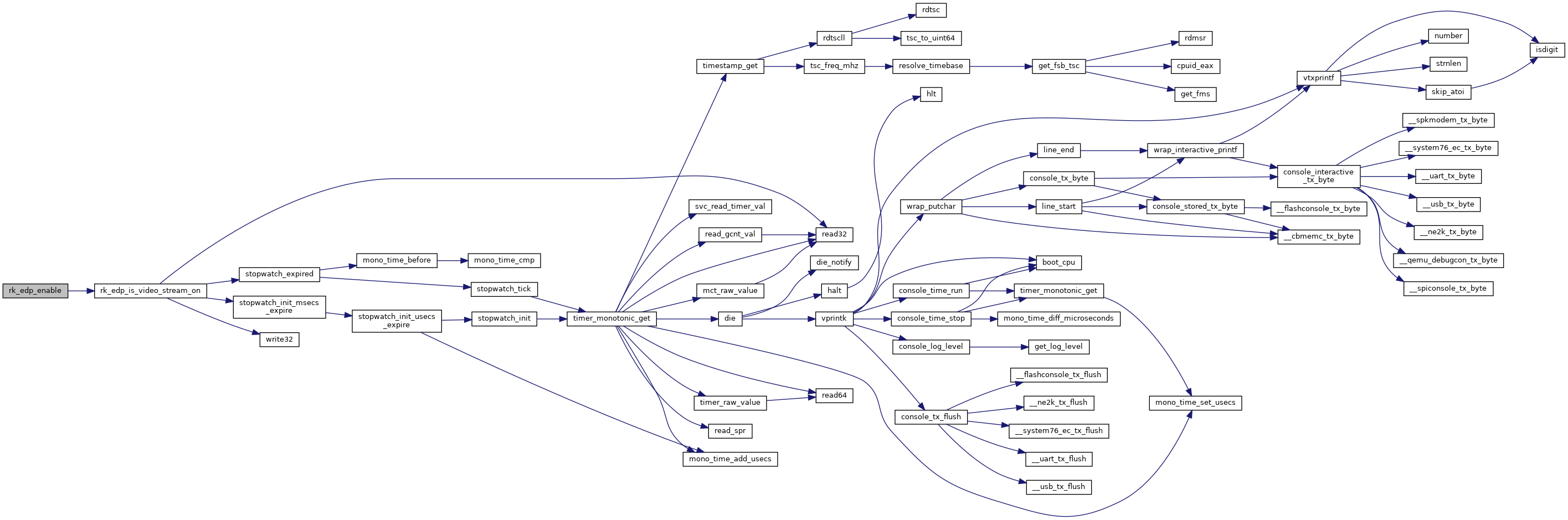

| int rk_edp_enable | ( | void | ) |

Definition at line 986 of file edp.c.

References rk_edp::regs, rk_edp_is_video_stream_on(), setbits32, rk_edp_regs::video_ctl_1, and VIDEO_EN.

Referenced by rk_display_init().

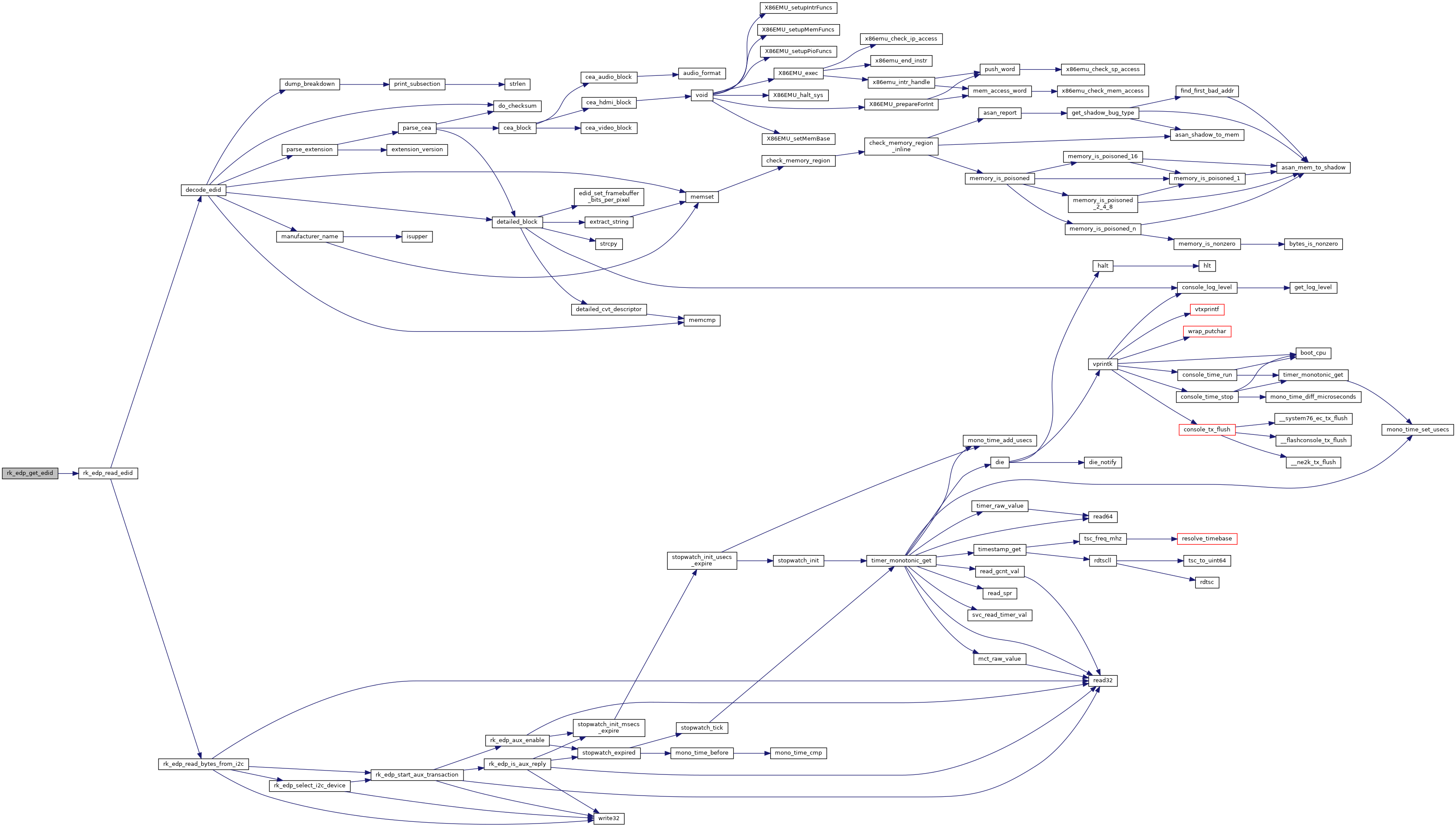

| int rk_edp_get_edid | ( | struct edid * | edid | ) |

Definition at line 954 of file edp.c.

References rk_edp_read_edid().

Referenced by rk_display_init().

Definition at line 994 of file edp.c.

References EDP_BASE, rk_edp::regs, rk_edp_enable_sw_function(), rk_edp_init_analog_func(), rk_edp_init_aux(), rk_edp_init_interrupt(), rk_edp_init_refclk(), and rk_edp_wait_hpd().

Referenced by rk_display_init().

| int rk_edp_prepare | ( | void | ) |

Definition at line 969 of file edp.c.

References BIOS_ERR, printk, rk_edp_config_video(), rk_edp_init_video(), and rk_edp_set_link_train().

Referenced by rk_display_init().