|

coreboot

coreboot is an Open Source project aimed at replacing the proprietary BIOS found in most computers.

|

|

coreboot

coreboot is an Open Source project aimed at replacing the proprietary BIOS found in most computers.

|

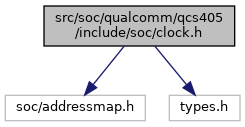

#include <soc/addressmap.h>#include <types.h>

Go to the source code of this file.

Data Structures | |

| struct | qcs405_rcg |

| struct | qcs405_clock |

| struct | qcs405_bcr |

| struct | qcs405_gpll |

| struct | qcs405_gcc |

| struct | mdss_clock_config |

| struct | clock_config |

Macros | |

| #define | BLSP1_AHB_CLK_ENA 10 |

| #define | BLSP2_AHB_CLK_ENA 20 |

| #define | SRC_XO_19_2MHZ 0 |

| #define | SRC_GPLL0_MAIN_800MHZ 1 |

| #define | GCC_USB_HS_PHY_CFG_AHB_BCR 0x180000C |

| USB BCR registers. More... | |

| #define | GCC_USB_HS_BCR 0x1841000 |

| #define | GCC_USB_30_BCR 0x1839000 |

| #define | GCC_USB2A_PHY_BCR 0x180000C |

| #define | GCC_USB2_HS_PHY_ONLY_BCR 0x1841034 |

| #define | GCC_QUSB2_PHY_BCR 0x184103C |

Functions | |

| void | clock_init (void) |

| void | clock_reset_aop (void) |

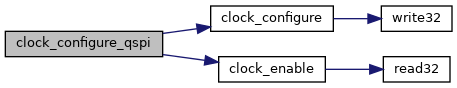

| int | clock_configure_qspi (uint32_t hz) |

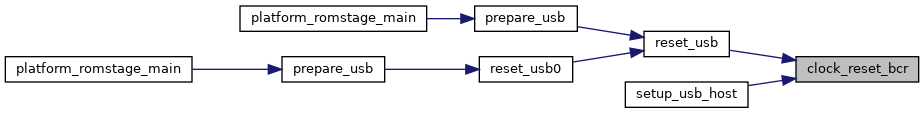

| int | clock_reset_bcr (void *bcr_addr, bool reset) |

| void | clock_configure_uart (uint32_t hz) |

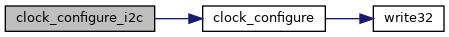

| void | clock_configure_i2c (uint32_t hz) |

| void | clock_configure_spi (int blsp, int qup, uint32_t hz) |

| void | clock_enable_uart (void) |

| void | clock_disable_uart (void) |

| void | clock_enable_spi (int blsp, int qup) |

| void | clock_disable_spi (int blsp, int qup) |

| void | clock_enable_i2c (void) |

| void | clock_disable_i2c (void) |

Variables | |

| static struct qcs405_gcc *const | gcc = (void *)GCC_BASE |

| #define GCC_USB_HS_PHY_CFG_AHB_BCR 0x180000C |

| enum clk_ctl_bcr |

| enum clk_ctl_cbcr |

| enum clk_ctl_cfg_rcgr |

| enum clk_ctl_cmd_rcgr |

| enum clk_ctl_rcg_mnd |

Definition at line 238 of file clock.c.

References ARRAY_SIZE, qcs405_gcc::blsp1_qup1_i2c_clk, clock_configure(), gcc, and i2c_cfg.

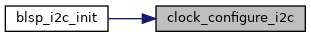

Referenced by blsp_i2c_init().

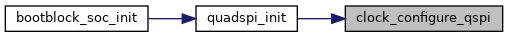

| int clock_configure_qspi | ( | uint32_t | hz | ) |

Definition at line 117 of file clock.c.

References ARRAY_SIZE, clock_configure(), clock_enable(), gcc, and qspi_core_cfg.

Referenced by quadspi_init().

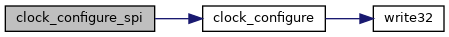

Definition at line 198 of file clock.c.

References ARRAY_SIZE, BIOS_ERR, qcs405_gcc::blsp1_qup0_spi_clk, qcs405_gcc::blsp1_qup1_spi_clk, qcs405_gcc::blsp1_qup2_spi_clk, qcs405_gcc::blsp1_qup3_spi_clk, qcs405_gcc::blsp1_qup4_spi_clk, qcs405_gcc::blsp2_qup0_spi_clk, clock_configure(), gcc, and printk.

Referenced by spi_ctrlr_setup().

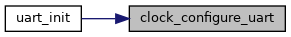

Definition at line 190 of file clock.c.

References ARRAY_SIZE, qcs405_gcc::blsp1_uart2_apps_clk, clock_configure(), gcc, and uart_cfg.

Referenced by uart_init().

Definition at line 314 of file clock.c.

References qcs405_gcc::blsp1_qup1_i2c_apps_cbcr, clock_disable(), and gcc.

| void clock_disable_spi | ( | int | blsp, |

| int | qup | ||

| ) |

Definition at line 282 of file clock.c.

References BIOS_ERR, qcs405_gcc::blsp1_qup0_spi_apps_cbcr, qcs405_gcc::blsp1_qup1_spi_apps_cbcr, qcs405_gcc::blsp1_qup2_spi_apps_cbcr, qcs405_gcc::blsp1_qup3_spi_apps_cbcr, qcs405_gcc::blsp1_qup4_spi_apps_cbcr, qcs405_gcc::blsp2_qup0_spi_apps_cbcr, clock_enable(), gcc, and printk.

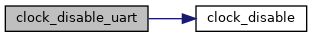

Definition at line 251 of file clock.c.

References qcs405_gcc::blsp1_uart2_apps_cbcr, clock_disable(), and gcc.

Definition at line 309 of file clock.c.

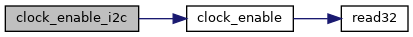

References qcs405_gcc::blsp1_qup1_i2c_apps_cbcr, clock_enable(), and gcc.

Referenced by blsp_i2c_init().

| void clock_enable_spi | ( | int | blsp, |

| int | qup | ||

| ) |

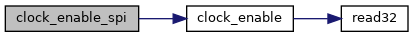

Definition at line 256 of file clock.c.

References BIOS_ERR, qcs405_gcc::blsp1_qup0_spi_apps_cbcr, qcs405_gcc::blsp1_qup1_spi_apps_cbcr, qcs405_gcc::blsp1_qup2_spi_apps_cbcr, qcs405_gcc::blsp1_qup3_spi_apps_cbcr, qcs405_gcc::blsp1_qup4_spi_apps_cbcr, qcs405_gcc::blsp2_qup0_spi_apps_cbcr, clock_enable(), gcc, and printk.

Referenced by spi_ctrlr_setup().

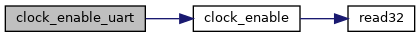

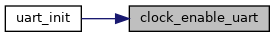

Definition at line 246 of file clock.c.

References qcs405_gcc::blsp1_uart2_apps_cbcr, clock_enable(), and gcc.

Referenced by uart_init().

Definition at line 54 of file clock.c.

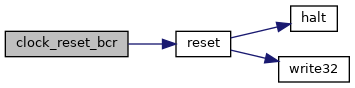

References assert, qcs405_bcr::bcr, BIT, CLK_CTL_BCR_BLK_ARES_SHFT, CLK_CTL_BCR_BLK_SHFT, clrbits32, reset(), and setbits32.

Referenced by reset_usb(), and setup_usb_host().

|

static |

Definition at line 165 of file clock.h.

Referenced by agera_pll_enable(), clock_configure_gpll0(), clock_configure_i2c(), clock_configure_qspi(), clock_configure_sdcc1(), clock_configure_sdcc2(), clock_configure_spi(), clock_configure_uart(), clock_disable_i2c(), clock_disable_spi(), clock_disable_uart(), clock_enable_i2c(), clock_enable_qup(), clock_enable_spi(), clock_enable_uart(), and clock_init().