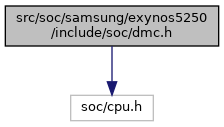

#include <soc/cpu.h>

Go to the source code of this file.

|

| enum | ddr_mode {

DDR_MODE_DDR2

, DDR_MODE_DDR3

, DDR_MODE_LPDDR2

, DDR_MODE_LPDDR3

,

DDR_MODE_COUNT

, DDR_MODE_DDR2 = 0x0

, DDR_MODE_DDR3 = 0x1

, DDR_MODE_LPDDR2 = 0x2

,

DDR_MODE_LPDDR3 = 0x3

, DDR_MODE_COUNT

} |

| |

| enum | mem_manuf {

MEM_MANUF_AUTODETECT

, MEM_MANUF_ELPIDA = 0xe7b1da

, MEM_MANUF_SAMSUNG = 0x5a5096

, MEM_MANUF_COUNT = 2

,

MEM_MANUF_AUTODETECT

, MEM_MANUF_ELPIDA = 0xe7b1da

, MEM_MANUF_SAMSUNG = 0x5a5096

, MEM_MANUF_COUNT = 2

} |

| |

| enum | { MEM_TIMINGS_MSR_COUNT = 4

} |

| |

◆ CONCONTROL_AREF_EN_SHIFT

| #define CONCONTROL_AREF_EN_SHIFT 5 |

◆ CONCONTROL_DFI_INIT_START_SHIFT

| #define CONCONTROL_DFI_INIT_START_SHIFT 28 |

◆ CONCONTROL_RD_FETCH_MASK

◆ CONCONTROL_RD_FETCH_SHIFT

| #define CONCONTROL_RD_FETCH_SHIFT 12 |

◆ DMC_INTERLEAVE_SIZE

| #define DMC_INTERLEAVE_SIZE 0x1f |

◆ PHY_CON0_CTRL_DDR_MODE_SHIFT

| #define PHY_CON0_CTRL_DDR_MODE_SHIFT 11 |

◆ PHY_CON0_T_WRRDCMD_MASK

◆ PHY_CON0_T_WRRDCMD_SHIFT

| #define PHY_CON0_T_WRRDCMD_SHIFT 17 |

◆ PHY_CON12_CTRL_DLL_ON_MASK

◆ PHY_CON12_CTRL_DLL_ON_SHIFT

| #define PHY_CON12_CTRL_DLL_ON_SHIFT 5 |

◆ PHY_CON12_CTRL_FORCE_SHIFT

| #define PHY_CON12_CTRL_FORCE_SHIFT 8 |

◆ PHY_CON12_CTRL_INC_SHIFT

| #define PHY_CON12_CTRL_INC_SHIFT 16 |

◆ PHY_CON12_CTRL_REF_SHIFT

| #define PHY_CON12_CTRL_REF_SHIFT 1 |

◆ PHY_CON12_CTRL_START_MASK

◆ PHY_CON12_CTRL_START_POINT_SHIFT

| #define PHY_CON12_CTRL_START_POINT_SHIFT 24 |

◆ PHY_CON12_CTRL_START_SHIFT

| #define PHY_CON12_CTRL_START_SHIFT 6 |

◆ PHY_CON16_ZQ_MODE_DDS_MASK

◆ PHY_CON16_ZQ_MODE_DDS_SHIFT

| #define PHY_CON16_ZQ_MODE_DDS_SHIFT 24 |

◆ PHY_CON16_ZQ_MODE_NOTERM_MASK

| #define PHY_CON16_ZQ_MODE_NOTERM_MASK (1 << 19) |

◆ PHY_CON16_ZQ_MODE_TERM_MASK

◆ PHY_CON16_ZQ_MODE_TERM_SHIFT

| #define PHY_CON16_ZQ_MODE_TERM_SHIFT 21 |

◆ PHY_CON1_RDLVL_RDDATA_ADJ_SHIFT

| #define PHY_CON1_RDLVL_RDDATA_ADJ_SHIFT 0 |

◆ PHY_CON42_CTRL_BSTLEN_MASK

◆ PHY_CON42_CTRL_BSTLEN_SHIFT

| #define PHY_CON42_CTRL_BSTLEN_SHIFT 8 |

◆ PHY_CON42_CTRL_RDLAT_MASK

◆ PHY_CON42_CTRL_RDLAT_SHIFT

| #define PHY_CON42_CTRL_RDLAT_SHIFT 0 |

◆ PRECHCONFIG_TP_CNT_SHIFT

| #define PRECHCONFIG_TP_CNT_SHIFT 24 |

◆ PWRDNCONFIG_DPWRDN_CYC_SHIFT

| #define PWRDNCONFIG_DPWRDN_CYC_SHIFT 0 |

◆ PWRDNCONFIG_DSREF_CYC_SHIFT

| #define PWRDNCONFIG_DSREF_CYC_SHIFT 16 |

◆ anonymous enum

| Enumerator |

|---|

| MEM_TIMINGS_MSR_COUNT | |

Definition at line 192 of file dmc.h.

◆ ddr_mode

| Enumerator |

|---|

| DDR_MODE_DDR2 | |

| DDR_MODE_DDR3 | |

| DDR_MODE_LPDDR2 | |

| DDR_MODE_LPDDR3 | |

| DDR_MODE_COUNT | |

| DDR_MODE_DDR2 | |

| DDR_MODE_DDR3 | |

| DDR_MODE_LPDDR2 | |

| DDR_MODE_LPDDR3 | |

| DDR_MODE_COUNT | |

Definition at line 160 of file dmc.h.

◆ mem_manuf

| Enumerator |

|---|

| MEM_MANUF_AUTODETECT | |

| MEM_MANUF_ELPIDA | |

| MEM_MANUF_SAMSUNG | |

| MEM_MANUF_COUNT | |

| MEM_MANUF_AUTODETECT | |

| MEM_MANUF_ELPIDA | |

| MEM_MANUF_SAMSUNG | |

| MEM_MANUF_COUNT | |

Definition at line 184 of file dmc.h.

◆ check_member() [1/2]

◆ check_member() [2/2]

◆ get_mem_timings()

Get the correct memory timings for our selected memory type and speed.

- Returns

- pointer to the memory timings that we should use

Definition at line 483 of file memory.c.

◆ exynos_dmc

◆ exynos_phy0_control

◆ exynos_phy1_control