|

coreboot

coreboot is an Open Source project aimed at replacing the proprietary BIOS found in most computers.

|

|

coreboot

coreboot is an Open Source project aimed at replacing the proprietary BIOS found in most computers.

|

Go to the source code of this file.

Macros | |

| #define | NOT_AVAILABLE 0 |

| #define | DATA_MASK 0xFFFFF |

| #define | ENABLE_BIT 0x1 |

| #define | DISABLE_BIT 0x0 |

| #define | CA_SWAP_EN (1 << 0) |

| #define | TZPC0_BASE 0x10100000 |

| #define | TZPC1_BASE 0x10110000 |

| #define | TZPC2_BASE 0x10120000 |

| #define | TZPC3_BASE 0x10130000 |

| #define | TZPC4_BASE 0x10140000 |

| #define | TZPC5_BASE 0x10150000 |

| #define | TZPC6_BASE 0x10160000 |

| #define | TZPC7_BASE 0x10170000 |

| #define | TZPC8_BASE 0x10180000 |

| #define | TZPC9_BASE 0x10190000 |

| #define | APLL_FOUT (1 << 0) |

| #define | KPLL_FOUT (1 << 0) |

| #define | CLK_DIV_CPERI1_VAL 0x3f3f0000 |

| #define | APLL_CON1_VAL (0x0020f300) |

| #define | MPLL_CON1_VAL (0x0020f300) |

| #define | CPLL_CON1_VAL (0x0020f300) |

| #define | DPLL_CON1_VAL (0x0020f300) |

| #define | GPLL_CON1_VAL (NOT_AVAILABLE) |

| #define | EPLL_CON1_VAL 0x00000000 |

| #define | EPLL_CON2_VAL 0x00000080 |

| #define | VPLL_CON1_VAL 0x0020f300 |

| #define | VPLL_CON2_VAL NOT_AVAILABLE |

| #define | RPLL_CON1_VAL 0x00000000 |

| #define | RPLL_CON2_VAL 0x00000080 |

| #define | BPLL_CON1_VAL 0x0020f300 |

| #define | SPLL_CON1_VAL 0x0020f300 |

| #define | IPLL_CON1_VAL 0x00000080 |

| #define | KPLL_CON1_VAL 0x200000 |

| #define | set_pll(mdiv, pdiv, sdiv) (1<<31 | mdiv<<16 | pdiv<<8 | sdiv) |

| #define | MUX_HPM_SEL 1 |

| #define | MUX_CPU_SEL 0 |

| #define | MUX_APLL_SEL 1 |

| #define | CLK_SRC_CPU_VAL |

| #define | DMC_MEMCONTROL_CLK_STOP_DISABLE (0 << 0) |

| #define | DMC_MEMCONTROL_DPWRDN_DISABLE (0 << 1) |

| #define | DMC_MEMCONTROL_DPWRDN_ACTIVE_PRECHARGE (0 << 2) |

| #define | DMC_MEMCONTROL_DSREF_DISABLE (0 << 5) |

| #define | DMC_MEMCONTROL_DSREF_ENABLE (1 << 5) |

| #define | DMC_MEMCONTROL_ADD_LAT_PALL_CYCLE(x) (x << 6) |

| #define | DMC_MEMCONTROL_MEM_TYPE_LPDDR3 (7 << 8) |

| #define | DMC_MEMCONTROL_MEM_TYPE_DDR3 (6 << 8) |

| #define | DMC_MEMCONTROL_MEM_TYPE_LPDDR2 (5 << 8) |

| #define | DMC_MEMCONTROL_MEM_WIDTH_32BIT (2 << 12) |

| #define | DMC_MEMCONTROL_NUM_CHIP_1 (0 << 16) |

| #define | DMC_MEMCONTROL_NUM_CHIP_2 (1 << 16) |

| #define | DMC_MEMCONTROL_BL_8 (3 << 20) |

| #define | DMC_MEMCONTROL_BL_4 (2 << 20) |

| #define | DMC_MEMCONTROL_PZQ_DISABLE (0 << 24) |

| #define | DMC_MEMCONTROL_MRR_BYTE_7_0 (0 << 25) |

| #define | DMC_MEMCONTROL_MRR_BYTE_15_8 (1 << 25) |

| #define | DMC_MEMCONTROL_MRR_BYTE_23_16 (2 << 25) |

| #define | DMC_MEMCONTROL_MRR_BYTE_31_24 (3 << 25) |

| #define | DMC_MEMCONFIGx_CHIP_MAP_INTERLEAVED (1 << 12) |

| #define | DMC_MEMCONFIG_CHIP_MAP_SPLIT (2 << 12) |

| #define | DMC_MEMCONFIGx_CHIP_COL_10 (3 << 8) |

| #define | DMC_MEMCONFIGx_CHIP_ROW_14 (2 << 4) |

| #define | DMC_MEMCONFIGx_CHIP_ROW_15 (3 << 4) |

| #define | DMC_MEMCONFIGx_CHIP_ROW_16 (4 << 4) |

| #define | DMC_MEMCONFIGx_CHIP_BANK_8 (3 << 0) |

| #define | DMC_MEMBASECONFIG0_VAL DMC_MEMBASECONFIG_VAL(0x40) |

| #define | DMC_MEMBASECONFIG1_VAL DMC_MEMBASECONFIG_VAL(0x80) |

| #define | DMC_PRECHCONFIG_VAL 0xFF000000 |

| #define | DMC_PWRDNCONFIG_VAL 0xFFFF00FF |

| #define | DMC_CONCONTROL_RESET_VAL 0x0FFF0000 |

| #define | DFI_INIT_START (1 << 28) |

| #define | EMPTY (1 << 8) |

| #define | AREF_EN (1 << 5) |

| #define | DFI_INIT_COMPLETE_CHO (1 << 2) |

| #define | DFI_INIT_COMPLETE_CH1 (1 << 3) |

| #define | RDLVL_COMPLETE_CHO (1 << 14) |

| #define | RDLVL_COMPLETE_CH1 (1 << 15) |

| #define | CLK_STOP_EN (1 << 0) |

| #define | DPWRDN_EN (1 << 1) |

| #define | DSREF_EN (1 << 5) |

| #define | DMC_CONCONTROL_IO_PD_CON_DISABLE (0 << 3) |

| #define | DMC_CONCONTROL_AREF_EN_DISABLE (0 << 5) |

| #define | DMC_CONCONTROL_RD_FETCH_DISABLE (0x0 << 12) |

| #define | DMC_CONCONTROL_TIMEOUT_LEVEL0 (0xFFF << 16) |

| #define | DMC_CONCONTROL_DFI_INIT_START_DISABLE (0 << 28) |

| #define | CLK_SRC_FSYS0_VAL 0x33033300 |

| #define | CLK_DIV_FSYS0_VAL 0x0 |

| #define | CLK_DIV_FSYS1_VAL 0x04f13c4f |

| #define | CLK_DIV_FSYS2_VAL 0x041d0000 |

| #define | DMC_CONCONTROL_IO_PD_CON(x) (x << 6) |

| #define | HPM_RATIO 0x2 |

| #define | COPY_RATIO 0x0 |

| #define | CLK_DIV_CPU1_VAL |

| #define | CLK_SRC_CORE0_VAL 0x00000000 |

| #define | CLK_SRC_CORE1_VAL 0x100 |

| #define | CLK_DIV_CORE0_VAL 0x00120000 |

| #define | CLK_DIV_CORE1_VAL 0x07070700 |

| #define | CLK_DIV_SYSRGT_VAL 0x00000111 |

| #define | CLK_DIV_ACP_VAL 0x12 |

| #define | CLK_DIV_SYSLFT_VAL 0x00000311 |

| #define | CLK_SRC_CDREX_VAL 0x00000001 |

| #define | MUX_MCLK_CDR_MSPLL (1 << 4) |

| #define | MUX_BPLL_SEL_FOUTBPLL (1 << 0) |

| #define | BPLL_SEL_MASK 0x7 |

| #define | FOUTBPLL 2 |

| #define | CLK_DIV_CDREX0_VAL 0x30010100 |

| #define | CLK_DIV_CDREX1_VAL 0x300 |

| #define | CLK_DIV_CDREX_VAL 0x17010100 |

| #define | CLK_DIV_CPU0_VAL 0x01440020 |

| #define | CLK_SRC_TOP0_VAL 0x11101102 |

| #define | CLK_SRC_TOP1_VAL 0x00200000 |

| #define | CLK_SRC_TOP2_VAL 0x11101010 |

| #define | CLK_SRC_TOP3_VAL 0x11111111 |

| #define | CLK_SRC_TOP4_VAL 0x11110111 |

| #define | CLK_SRC_TOP5_VAL 0x11111111 |

| #define | CLK_SRC_TOP6_VAL 0x11110111 |

| #define | CLK_SRC_TOP7_VAL 0x00022200 |

| #define | CLK_DIV_TOP0_VAL 0x22512211 |

| #define | CLK_DIV_TOP1_VAL 0x13200900 |

| #define | CLK_DIV_TOP2_VAL 0x11101110 |

| #define | APLL_LOCK_VAL (0x320) |

| #define | MPLL_LOCK_VAL (0x258) |

| #define | BPLL_LOCK_VAL (0x258) |

| #define | CPLL_LOCK_VAL (0x190) |

| #define | DPLL_LOCK_VAL (0x190) |

| #define | GPLL_LOCK_VAL NOT_AVAILABLE |

| #define | IPLL_LOCK_VAL (0x320) |

| #define | KPLL_LOCK_VAL (0x258) |

| #define | SPLL_LOCK_VAL (0x320) |

| #define | RPLL_LOCK_VAL (0x2328) |

| #define | EPLL_LOCK_VAL (0x2328) |

| #define | VPLL_LOCK_VAL (0x258) |

| #define | MUX_APLL_SEL_MASK (1 << 0) |

| #define | MUX_MPLL_SEL_MASK (1 << 8) |

| #define | MPLL_SEL_MOUT_MPLLFOUT (2 << 8) |

| #define | MUX_CPLL_SEL_MASK (1 << 8) |

| #define | MUX_EPLL_SEL_MASK (1 << 12) |

| #define | MUX_VPLL_SEL_MASK (1 << 16) |

| #define | MUX_GPLL_SEL_MASK (1 << 28) |

| #define | MUX_BPLL_SEL_MASK (1 << 0) |

| #define | MUX_HPM_SEL_MASK (1 << 20) |

| #define | HPM_SEL_SCLK_MPLL (1 << 21) |

| #define | PLL_LOCKED (1 << 29) |

| #define | APLL_CON0_LOCKED (1 << 29) |

| #define | MPLL_CON0_LOCKED (1 << 29) |

| #define | BPLL_CON0_LOCKED (1 << 29) |

| #define | CPLL_CON0_LOCKED (1 << 29) |

| #define | EPLL_CON0_LOCKED (1 << 29) |

| #define | GPLL_CON0_LOCKED (1 << 29) |

| #define | VPLL_CON0_LOCKED (1 << 29) |

| #define | CLK_REG_DISABLE 0x0 |

| #define | TOP2_VAL 0x0110000 |

| #define | CLK_SRC_LEX_VAL 0x0 |

| #define | CLK_DIV_LEX_VAL 0x10 |

| #define | CLK_DIV_R0X_VAL 0x10 |

| #define | CLK_DIV_R1X_VAL 0x10 |

| #define | CLK_DIV_ISP2_VAL 0x1 |

| #define | SRC_KFC_HPM_SEL (1 << 15) |

| #define | CLK_SRC_KFC_VAL 0x00008001 |

| #define | CLK_DIV_KFC_VAL 0x03300110 |

| #define | CLK_DIV2_RATIO 0x10111150 |

| #define | CLK_DIV4_RATIO 0x00000003 |

| #define | CLK_DIV_G2D 0x00000010 |

| #define | SPDIF_SEL 1 |

| #define | PWM_SEL 3 |

| #define | UART4_SEL 3 |

| #define | UART3_SEL 3 |

| #define | UART2_SEL 3 |

| #define | UART1_SEL 3 |

| #define | UART0_SEL 3 |

| #define | CLK_SRC_PERIC0_VAL |

| #define | SPI0_SEL 3 |

| #define | SPI1_SEL 3 |

| #define | SPI2_SEL 3 |

| #define | AUDIO0_SEL 6 |

| #define | AUDIO1_SEL 6 |

| #define | AUDIO2_SEL 6 |

| #define | CLK_SRC_PERIC1_VAL |

| #define | CLK_SRC_ISP_VAL 0x33366000 |

| #define | CLK_DIV_ISP0_VAL 0x13131300 |

| #define | CLK_DIV_ISP1_VAL 0xbb110202 |

| #define | SPI0_ISP_RATIO 0xf |

| #define | SPI1_ISP_RATIO 0xf |

| #define | SCLK_DIV_ISP_VAL |

| #define | PWM_RATIO 8 |

| #define | UART4_RATIO 9 |

| #define | UART3_RATIO 9 |

| #define | UART2_RATIO 9 |

| #define | UART1_RATIO 9 |

| #define | UART0_RATIO 9 |

| #define | CLK_DIV_PERIC0_VAL |

| #define | SPI2_RATIO 0x1 |

| #define | SPI1_RATIO 0x1 |

| #define | SPI0_RATIO 0x1 |

| #define | CLK_DIV_PERIC1_VAL |

| #define | PCM2_RATIO 0x3 |

| #define | PCM1_RATIO 0x3 |

| #define | CLK_DIV_PERIC2_VAL |

| #define | AUDIO2_RATIO 0x5 |

| #define | AUDIO1_RATIO 0x5 |

| #define | AUDIO0_RATIO 0x5 |

| #define | CLK_DIV_PERIC3_VAL |

| #define | SPI2_PRE_RATIO 0x3 |

| #define | SPI1_PRE_RATIO 0x3 |

| #define | SPI0_PRE_RATIO 0x3 |

| #define | CLK_DIV_PERIC4_VAL |

| #define | MMC2_RATIO_MASK 0xf |

| #define | MMC2_RATIO_VAL 0x3 |

| #define | MMC2_RATIO_OFFSET 0 |

| #define | MMC2_PRE_RATIO_MASK 0xff |

| #define | MMC2_PRE_RATIO_VAL 0x9 |

| #define | MMC2_PRE_RATIO_OFFSET 8 |

| #define | MMC3_RATIO_MASK 0xf |

| #define | MMC3_RATIO_VAL 0x1 |

| #define | MMC3_RATIO_OFFSET 16 |

| #define | MMC3_PRE_RATIO_MASK 0xff |

| #define | MMC3_PRE_RATIO_VAL 0x0 |

| #define | MMC3_PRE_RATIO_OFFSET 24 |

| #define | CLK_SRC_LEX_VAL 0x0 |

| #define | CLK_DIV_LEX_VAL 0x10 |

| #define | CLK_DIV_R0X_VAL 0x10 |

| #define | CLK_DIV_R1X_VAL 0x10 |

| #define | CLK_DIV_ISP2_VAL 0x1 |

| #define | CLK_SRC_DISP1_0_VAL 0x10006000 |

| #define | CLK_DIV_DISP1_0_VAL 0x01050210 |

| #define | CLK_DIV_DISP1_0_FIMD1 (2 << 0) |

| #define | CLK_GATE_DP1_ALLOW (1 << 4) |

| #define | CLK_C2C_MASK (1 << 1) |

| #define | CLK_SMMUG2D_MASK (1 << 7) |

| #define | CLK_SMMUSSS_MASK (1 << 6) |

| #define | CLK_SMMUMDMA_MASK (1 << 5) |

| #define | CLK_ID_REMAPPER_MASK (1 << 4) |

| #define | CLK_G2D_MASK (1 << 3) |

| #define | CLK_SSS_MASK (1 << 2) |

| #define | CLK_MDMA_MASK (1 << 1) |

| #define | CLK_SECJTAG_MASK (1 << 0) |

| #define | CLK_EFCLK_MASK (1 << 16) |

| #define | CLK_UART_ISP_MASK (1 << 31) |

| #define | CLK_WDT_ISP_MASK (1 << 30) |

| #define | CLK_PWM_ISP_MASK (1 << 28) |

| #define | CLK_MTCADC_ISP_MASK (1 << 27) |

| #define | CLK_I2C1_ISP_MASK (1 << 26) |

| #define | CLK_I2C0_ISP_MASK (1 << 25) |

| #define | CLK_MPWM_ISP_MASK (1 << 24) |

| #define | CLK_MCUCTL_ISP_MASK (1 << 23) |

| #define | CLK_INT_COMB_ISP_MASK (1 << 22) |

| #define | CLK_SMMU_MCUISP_MASK (1 << 13) |

| #define | CLK_SMMU_SCALERP_MASK (1 << 12) |

| #define | CLK_SMMU_SCALERC_MASK (1 << 11) |

| #define | CLK_SMMU_FD_MASK (1 << 10) |

| #define | CLK_SMMU_DRC_MASK (1 << 9) |

| #define | CLK_SMMU_ISP_MASK (1 << 8) |

| #define | CLK_GICISP_MASK (1 << 7) |

| #define | CLK_ARM9S_MASK (1 << 6) |

| #define | CLK_MCUISP_MASK (1 << 5) |

| #define | CLK_SCALERP_MASK (1 << 4) |

| #define | CLK_SCALERC_MASK (1 << 3) |

| #define | CLK_FD_MASK (1 << 2) |

| #define | CLK_DRC_MASK (1 << 1) |

| #define | CLK_ISP_MASK (1 << 0) |

| #define | CLK_SPI1_ISP_MASK (1 << 13) |

| #define | CLK_SPI0_ISP_MASK (1 << 12) |

| #define | CLK_SMMU3DNR_MASK (1 << 7) |

| #define | CLK_SMMUDIS1_MASK (1 << 6) |

| #define | CLK_SMMUDIS0_MASK (1 << 5) |

| #define | CLK_SMMUODC_MASK (1 << 4) |

| #define | CLK_3DNR_MASK (1 << 2) |

| #define | CLK_DIS_MASK (1 << 1) |

| #define | CLK_ODC_MASK (1 << 0) |

| #define | CLK_SMMUFIMC_LITE2_MASK (1 << 20) |

| #define | CLK_SMMUFIMC_LITE1_MASK (1 << 12) |

| #define | CLK_SMMUFIMC_LITE0_MASK (1 << 11) |

| #define | CLK_SMMUGSCL3_MASK (1 << 10) |

| #define | CLK_SMMUGSCL2_MASK (1 << 9) |

| #define | CLK_SMMUGSCL1_MASK (1 << 8) |

| #define | CLK_SMMUGSCL0_MASK (1 << 7) |

| #define | CLK_GSCL_WRAP_B_MASK (1 << 6) |

| #define | CLK_GSCL_WRAP_A_MASK (1 << 5) |

| #define | CLK_CAMIF_TOP_MASK (1 << 4) |

| #define | CLK_GSCL3_MASK (1 << 3) |

| #define | CLK_GSCL2_MASK (1 << 2) |

| #define | CLK_GSCL1_MASK (1 << 1) |

| #define | CLK_GSCL0_MASK (1 << 0) |

| #define | CLK_SMMUMFCR_MASK (1 << 2) |

| #define | CLK_SMMUMFCL_MASK (1 << 1) |

| #define | CLK_MFC_MASK (1 << 0) |

| #define | SCLK_MPWM_ISP_MASK (1 << 0) |

| #define | CLK_SMMUTVX_MASK (1 << 9) |

| #define | CLK_ASYNCTVX_MASK (1 << 7) |

| #define | CLK_HDMI_MASK (1 << 6) |

| #define | CLK_MIXER_MASK (1 << 5) |

| #define | CLK_DSIM1_MASK (1 << 3) |

| #define | AUDIO0_SEL_EPLL (0x6 << 28) |

| #define | AUDIO0_RATIO 0x5 |

| #define | PCM0_RATIO 0x3 |

| #define | DIV_MAU_VAL (PCM0_RATIO << 24 | AUDIO0_RATIO << 20) |

| #define | CLK_SMMUMDMA1_MASK (1 << 9) |

| #define | CLK_SMMUJPEG_MASK (1 << 7) |

| #define | CLK_SMMUROTATOR_MASK (1 << 6) |

| #define | CLK_MDMA1_MASK (1 << 4) |

| #define | CLK_JPEG_MASK (1 << 2) |

| #define | CLK_ROTATOR_MASK (1 << 1) |

| #define | CLK_WDT_IOP_MASK (1 << 30) |

| #define | CLK_SMMUMCU_IOP_MASK (1 << 26) |

| #define | CLK_SATA_PHY_I2C_MASK (1 << 25) |

| #define | CLK_SATA_PHY_CTRL_MASK (1 << 24) |

| #define | CLK_MCUCTL_MASK (1 << 23) |

| #define | CLK_NFCON_MASK (1 << 22) |

| #define | CLK_SMMURTIC_MASK (1 << 11) |

| #define | CLK_RTIC_MASK (1 << 9) |

| #define | CLK_MIPI_HSI_MASK (1 << 8) |

| #define | CLK_USBOTG_MASK (1 << 7) |

| #define | CLK_SATA_MASK (1 << 6) |

| #define | CLK_PDMA1_MASK (1 << 2) |

| #define | CLK_PDMA0_MASK (1 << 1) |

| #define | CLK_MCU_IOP_MASK (1 << 0) |

| #define | CLK_HS_I2C3_MASK (1 << 31) |

| #define | CLK_HS_I2C2_MASK (1 << 30) |

| #define | CLK_HS_I2C1_MASK (1 << 29) |

| #define | CLK_HS_I2C0_MASK (1 << 28) |

| #define | CLK_AC97_MASK (1 << 27) |

| #define | CLK_SPDIF_MASK (1 << 26) |

| #define | CLK_PCM2_MASK (1 << 23) |

| #define | CLK_PCM1_MASK (1 << 22) |

| #define | CLK_I2S2_MASK (1 << 21) |

| #define | CLK_I2S1_MASK (1 << 20) |

| #define | CLK_SPI2_MASK (1 << 18) |

| #define | CLK_SPI0_MASK (1 << 16) |

| #define | CLK_I2CHDMI_MASK (1 << 14) |

| #define | CLK_I2C7_MASK (1 << 13) |

| #define | CLK_I2C6_MASK (1 << 12) |

| #define | CLK_I2C5_MASK (1 << 11) |

| #define | CLK_I2C4_MASK (1 << 10) |

| #define | CLK_I2C3_MASK (1 << 9) |

| #define | CLK_I2C2_MASK (1 << 8) |

| #define | CLK_I2C1_MASK (1 << 7) |

| #define | CLK_I2C0_MASK (1 << 6) |

| #define | CLK_RTC_MASK (1 << 20) |

| #define | CLK_TZPC9_MASK (1 << 15) |

| #define | CLK_TZPC8_MASK (1 << 14) |

| #define | CLK_TZPC7_MASK (1 << 13) |

| #define | CLK_TZPC6_MASK (1 << 12) |

| #define | CLK_TZPC5_MASK (1 << 11) |

| #define | CLK_TZPC4_MASK (1 << 10) |

| #define | CLK_TZPC3_MASK (1 << 9) |

| #define | CLK_TZPC2_MASK (1 << 8) |

| #define | CLK_TZPC1_MASK (1 << 7) |

| #define | CLK_TZPC0_MASK (1 << 6) |

| #define | CLK_CHIPID_MASK (1 << 0) |

| #define | CLK_ACP_MASK (1 << 7) |

| #define | CLK_TZASC_DRBXW_MASK (1 << 23) |

| #define | CLK_TZASC_DRBXR_MASK (1 << 22) |

| #define | CLK_TZASC_XLBXW_MASK (1 << 21) |

| #define | CLK_TZASC_XLBXR_MASK (1 << 20) |

| #define | CLK_TZASC_XR1BXW_MASK (1 << 19) |

| #define | CLK_TZASC_XR1BXR_MASK (1 << 18) |

| #define | CLK_DPHY1_MASK (1 << 5) |

| #define | CLK_DPHY0_MASK (1 << 4) |

| #define | R0SIZE 0x0 |

| #define | DECPROTXSET 0xFF |

| #define | LPDDR3PHY_CTRL_PHY_RESET (1 << 0) |

| #define | LPDDR3PHY_CTRL_PHY_RESET_OFF (0 << 0) |

| #define | PHY_CON0_RESET_VAL 0x17020a40 |

| #define | P0_CMD_EN (1 << 14) |

| #define | BYTE_RDLVL_EN (1 << 13) |

| #define | CTRL_SHGATE (1 << 8) |

| #define | PHY_CON1_RESET_VAL 0x09210100 |

| #define | RDLVL_PASS_ADJ_VAL 0x6 |

| #define | RDLVL_PASS_ADJ_OFFSET 16 |

| #define | CTRL_GATEDURADJ_MASK (0xf << 20) |

| #define | READ_LEVELLING_DDR3 0x0100 |

| #define | PHY_CON2_RESET_VAL 0x00010004 |

| #define | INIT_DESKEW_EN (1 << 6) |

| #define | DLL_DESKEW_EN (1 << 12) |

| #define | RDLVL_GATE_EN (1 << 24) |

| #define | RDLVL_EN (1 << 25) |

| #define | RDLVL_INCR_ADJ (0x1 << 16) |

| #define | DREX_PAUSE_EN (1 << 0) |

| #define | BYPASS_EN (1 << 22) |

| #define | PHY_CON0_VAL 0x17021A00 |

| #define | PHY_CON12_RESET_VAL 0x10100070 |

| #define | PHY_CON12_VAL 0x10107F50 |

| #define | CTRL_START (1 << 6) |

| #define | CTRL_DLL_ON (1 << 5) |

| #define | CTRL_FORCE_MASK (0x7F << 8) |

| #define | CTRL_LOCK_COARSE_MASK (0x7F << 10) |

| #define | CTRL_OFFSETD_RESET_VAL 0x8 |

| #define | CTRL_OFFSETD_VAL 0x7F |

| #define | CTRL_OFFSETR0 0x7F |

| #define | CTRL_OFFSETR1 0x7F |

| #define | CTRL_OFFSETR2 0x7F |

| #define | CTRL_OFFSETR3 0x7F |

| #define | PHY_CON4_VAL |

| #define | PHY_CON4_RESET_VAL 0x08080808 |

| #define | CTRL_OFFSETW0 0x7F |

| #define | CTRL_OFFSETW1 0x7F |

| #define | CTRL_OFFSETW2 0x7F |

| #define | CTRL_OFFSETW3 0x7F |

| #define | PHY_CON6_VAL |

| #define | PHY_CON6_RESET_VAL 0x08080808 |

| #define | PHY_CON14_RESET_VAL 0x001F0000 |

| #define | CTRL_PULLD_DQS 0xF |

| #define | CTRL_PULLD_DQS_OFFSET 0 |

| #define | PHY_CON16_RESET_VAL 0x08000304 |

| #define | ZQ_CLK_EN (1 << 27) |

| #define | ZQ_CLK_DIV_EN (1 << 18) |

| #define | ZQ_MANUAL_MODE_OFFSET 2 |

| #define | ZQ_LONG_CALIBRATION 0x1 |

| #define | ZQ_MANUAL_STR (1 << 1) |

| #define | ZQ_DONE (1 << 0) |

| #define | ZQ_MODE_DDS_OFFSET 24 |

| #define | LONG_CALIBRATION (ZQ_LONG_CALIBRATION << ZQ_MANUAL_MODE_OFFSET) |

| #define | CTRL_RDLVL_GATE_ENABLE 1 |

| #define | CTRL_RDLVL_GATE_DISABLE 0 |

| #define | CTRL_RDLVL_DATA_ENABLE (1 << 1) |

| #define | DIRECT_CMD_NOP 0x07000000 |

| #define | DIRECT_CMD_PALL 0x01000000 |

| #define | DIRECT_CMD_ZQINIT 0x0a000000 |

| #define | DIRECT_CMD_CHANNEL_SHIFT 28 |

| #define | DIRECT_CMD_CHIP_SHIFT 20 |

| #define | DIRECT_CMD_BANK_SHIFT 16 |

| #define | DIRECT_CMD_REFA (5 << 24) |

| #define | DIRECT_CMD_MRS1 0x71C00 |

| #define | DIRECT_CMD_MRS2 0x10BFC |

| #define | DIRECT_CMD_MRS3 0x0050C |

| #define | DIRECT_CMD_MRS4 0x00868 |

| #define | DIRECT_CMD_MRS5 0x00C04 |

| #define | IMPEDANCE_48_OHM 4 |

| #define | IMPEDANCE_40_OHM 5 |

| #define | IMPEDANCE_34_OHM 6 |

| #define | IMPEDANCE_30_OHM 7 |

| #define | PHY_CON39_VAL_48_OHM 0x09240924 |

| #define | PHY_CON39_VAL_40_OHM 0x0B6D0B6D |

| #define | PHY_CON39_VAL_34_OHM 0x0DB60DB6 |

| #define | PHY_CON39_VAL_30_OHM 0x0FFF0FFF |

| #define | CTRL_BSTLEN_OFFSET 8 |

| #define | CTRL_RDLAT_OFFSET 0 |

| #define | CMD_DEFAULT_LPDDR3 0xF |

| #define | CMD_DEFAULT_OFFSET 0 |

| #define | T_WRDATA_EN 0x7 |

| #define | T_WRDATA_EN_DDR3 0x8 /* FIXME(dhendrix): 6 for DDR3? see T_wrdata_en */ |

| #define | T_WRDATA_EN_OFFSET 16 |

| #define | T_WRDATA_EN_MASK 0x1f |

| #define | PHY_CON31_VAL 0x0C183060 |

| #define | PHY_CON32_VAL 0x60C18306 |

| #define | PHY_CON33_VAL 0x00000030 |

| #define | PHY_CON31_RESET_VAL 0x0 |

| #define | PHY_CON32_RESET_VAL 0x0 |

| #define | PHY_CON33_RESET_VAL 0x0 |

| #define | SL_DLL_DYN_CON_EN (1 << 1) |

| #define | FP_RESYNC (1 << 3) |

| #define | CTRL_START (1 << 6) |

| #define | DMC_AREF_EN (1 << 5) |

| #define | DMC_CONCONTROL_EMPTY (1 << 8) |

| #define | DFI_INIT_START (1 << 28) |

| #define | DMC_MEMCONTROL_VAL 0x00312700 |

| #define | CLK_STOP_EN (1 << 0) |

| #define | DPWRDN_EN (1 << 1) |

| #define | DSREF_EN (1 << 5) |

| #define | DMC_CHIP_MASK_256MB 0x7f0 |

| #define | DMC_CHIP_MASK_512MB 0x7e0 |

| #define | DMC_CHIP_MASK_1GB 0x7c0 |

| #define | DMC_CHIP_MASK_2GB 0x780 |

| #define | DMC_CHIP_MASK_4GB 0x700 |

| #define | MEMCONFIG_VAL 0x1323 |

| #define | PRECHCONFIG_DEFAULT_VAL 0xFF000000 |

| #define | PWRDNCONFIG_DEFAULT_VAL 0xFFFF00FF |

| #define | DFI_INIT_COMPLETE (1 << 3) |

| #define | BRBRSVCONTROL_VAL 0x00000033 |

| #define | BRBRSVCONFIG_VAL 0x88778877 |

| #define | MEMIF_CG_EN (1 << 3) /* Memory interface clock gating */ |

| #define | SCG_CG_EN (1 << 2) /* Scheduler clock gating */ |

| #define | BUSIF_WR_CG_EN (1 << 1) /* Bus interface write channel clock gating */ |

| #define | BUSIF_RD_CG_EN (1 << 0) /* Bus interface read channel clock gating */ |

| #define | DMC_INTERNAL_CG |

| #define | PHY_CONTROL0_RESET_VAL 0x0 |

| #define | MEM_TERM_EN (1 << 31) /* Termination enable for memory */ |

| #define | PHY_TERM_EN (1 << 30) /* Termination enable for PHY */ |

| #define | DMC_CTRL_SHGATE (1 << 29) /* Duration of DQS gating signal */ |

| #define | CTRL_ATGATE (1 << 6) |

| #define | FP_RSYNC (1 << 3) /* Force DLL resynchronization */ |

| #define | IMP_OUTPUT_DRV_40_OHM 0x5 |

| #define | IMP_OUTPUT_DRV_30_OHM 0x7 |

| #define | DA_3_DS_OFFSET 25 |

| #define | DA_2_DS_OFFSET 22 |

| #define | DA_1_DS_OFFSET 19 |

| #define | DA_0_DS_OFFSET 16 |

| #define | CA_CK_DRVR_DS_OFFSET 9 |

| #define | CA_CKE_DRVR_DS_OFFSET 6 |

| #define | CA_CS_DRVR_DS_OFFSET 3 |

| #define | CA_ADR_DRVR_DS_OFFSET 0 |

| #define | PHY_CON42_CTRL_BSTLEN_SHIFT 8 |

| #define | PHY_CON42_CTRL_RDLAT_SHIFT 0 |

Enumerations | |

| enum | { SETUP_ERR_OK , SETUP_ERR_RDLV_COMPLETE_TIMEOUT = -1 , SETUP_ERR_ZQ_CALIBRATION_FAILURE = -2 } |

Functions | |

| void | cpu_info_init (void) |

| void | mem_ctrl_init (void) |

| int | ddr3_mem_ctrl_init (struct mem_timings *mem, int interleave_size, int reset) |

| int | lpddr3_mem_ctrl_init (int reset) |

| int | dmc_config_zq (struct mem_timings *mem, struct exynos5_phy_control *phy0_ctrl, struct exynos5_phy_control *phy1_ctrl) |

| void | dmc_config_mrs (struct mem_timings *mem, struct exynos5_dmc *dmc) |

| void | dmc_config_prech (struct mem_timings *mem, struct exynos5_dmc *dmc) |

| void | dmc_config_memory (struct mem_timings *mem, struct exynos5_dmc *dmc) |

| void | update_reset_dll (struct exynos5_dmc *, enum ddr_mode) |

| #define BUSIF_RD_CG_EN (1 << 0) /* Bus interface read channel clock gating */ |

| #define BUSIF_WR_CG_EN (1 << 1) /* Bus interface write channel clock gating */ |

| #define CLK_DIV_CPU1_VAL |

| #define CLK_DIV_PERIC0_VAL |

| #define CLK_DIV_PERIC1_VAL |

| #define CLK_DIV_PERIC2_VAL |

| #define CLK_DIV_PERIC3_VAL |

| #define CLK_DIV_PERIC4_VAL |

| #define CLK_SRC_CPU_VAL |

| #define CLK_SRC_PERIC0_VAL |

| #define CLK_SRC_PERIC1_VAL |

| #define DIV_MAU_VAL (PCM0_RATIO << 24 | AUDIO0_RATIO << 20) |

| #define DMC_CTRL_SHGATE (1 << 29) /* Duration of DQS gating signal */ |

| #define DMC_INTERNAL_CG |

| #define DMC_MEMBASECONFIG0_VAL DMC_MEMBASECONFIG_VAL(0x40) |

| #define DMC_MEMBASECONFIG1_VAL DMC_MEMBASECONFIG_VAL(0x80) |

| #define GPLL_CON1_VAL (NOT_AVAILABLE) |

| #define GPLL_LOCK_VAL NOT_AVAILABLE |

| #define LONG_CALIBRATION (ZQ_LONG_CALIBRATION << ZQ_MANUAL_MODE_OFFSET) |

| #define MEM_TERM_EN (1 << 31) /* Termination enable for memory */ |

| #define MEMIF_CG_EN (1 << 3) /* Memory interface clock gating */ |

| #define PHY_CON4_VAL |

| #define PHY_CON6_VAL |

| #define PHY_TERM_EN (1 << 30) /* Termination enable for PHY */ |

| #define SCLK_DIV_ISP_VAL |

| #define set_pll | ( | mdiv, | |

| pdiv, | |||

| sdiv | |||

| ) | (1<<31 | mdiv<<16 | pdiv<<8 | sdiv) |

| #define T_WRDATA_EN_DDR3 0x8 /* FIXME(dhendrix): 6 for DDR3? see T_wrdata_en */ |

| #define VPLL_CON2_VAL NOT_AVAILABLE |

| anonymous enum |

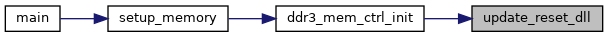

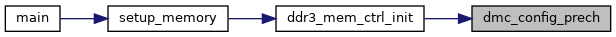

| int ddr3_mem_ctrl_init | ( | struct mem_timings * | mem, |

| int | interleave_size, | ||

| int | reset | ||

| ) |

Definition at line 15 of file dmc_init_ddr3.c.

References mem_timings::aref_en, exynos5_clock::bpll_con1, BPLL_SEL_MASK, BYPASS_EN, CA_ADR_DRVR_DS_OFFSET, CA_CK_DRVR_DS_OFFSET, CA_CKE_DRVR_DS_OFFSET, CA_CS_DRVR_DS_OFFSET, exynos5_dmc::cgcontrol, chip, mem_timings::chips_per_channel, mem_timings::chips_to_configure, clrbits32, exynos5_dmc::concontrol, mem_timings::concontrol, CONCONTROL_AREF_EN_SHIFT, CONCONTROL_DFI_INIT_START_SHIFT, CONCONTROL_RD_FETCH_SHIFT, mem_timings::ctrl_bstlen, CTRL_DLL_ON, CTRL_GATEDURADJ_MASK, CTRL_LOCK_COARSE_MASK, mem_timings::ctrl_rdlat, CTRL_RDLVL_GATE_DISABLE, CTRL_RDLVL_GATE_ENABLE, CTRL_SHGATE, DA_0_DS_OFFSET, DA_1_DS_OFFSET, DA_2_DS_OFFSET, DA_3_DS_OFFSET, DFI_INIT_COMPLETE, DFI_INIT_START, mem_timings::dfi_init_start, DIRECT_CMD_BANK_SHIFT, DIRECT_CMD_CHIP_SHIFT, DIRECT_CMD_REFA, exynos5_dmc::directcmd, DLL_DESKEW_EN, DMC_CONCONTROL_IO_PD_CON, dmc_config_mrs(), dmc_config_prech(), dmc_config_zq(), DMC_INTERNAL_CG, ENABLE_BIT, exynos_clock, exynos_drex0, exynos_drex1, exynos_phy0_control, exynos_phy1_control, exynos_power, exynos_tzasc0, exynos_tzasc1, FOUTBPLL, mem_timings::gate_leveling_enable, INIT_DESKEW_EN, MEM_TERM_EN, mem_timings::mem_type, mem_timings::membaseconfig0, exynos5_tzasc::membaseconfig0, mem_timings::membaseconfig1, exynos5_tzasc::membaseconfig1, mem_timings::memconfig, exynos5_tzasc::memconfig0, exynos5_tzasc::memconfig1, exynos5_dmc::memcontrol, mem_timings::memcontrol, MUX_BPLL_SEL_FOUTBPLL, P0_CMD_EN, PAD_RETENTION_DRAM_COREBLK_VAL, exynos5_power::padret_dram_cblk_opt, exynos5_power::padret_dram_status, mem_timings::phy0_pulld_dqs, mem_timings::phy1_pulld_dqs, exynos5_phy_control::phy_con0, PHY_CON0_CTRL_DDR_MODE_MASK, PHY_CON0_CTRL_DDR_MODE_SHIFT, PHY_CON0_RESET_VAL, exynos5_phy_control::phy_con1, exynos5_phy_control::phy_con12, PHY_CON12_RESET_VAL, exynos5_phy_control::phy_con13, exynos5_phy_control::phy_con14, exynos5_phy_control::phy_con16, exynos5_phy_control::phy_con2, exynos5_phy_control::phy_con26, PHY_CON2_RESET_VAL, exynos5_phy_control::phy_con39, exynos5_phy_control::phy_con42, PHY_CON42_CTRL_BSTLEN_SHIFT, PHY_CON42_CTRL_RDLAT_SHIFT, PHY_TERM_EN, exynos5_dmc::phycontrol0, exynos5_dmc::phystatus, exynos5_dmc::prechconfig0, mem_timings::prechconfig_tp_cnt, PRECHCONFIG_TP_CNT_SHIFT, mem_timings::rd_fetch, RDLVL_COMPLETE_CHO, exynos5_dmc::rdlvl_config, RDLVL_GATE_EN, RDLVL_PASS_ADJ_OFFSET, RDLVL_PASS_ADJ_VAL, read32(), reset(), setbits32, SETUP_ERR_RDLV_COMPLETE_TIMEOUT, SETUP_ERR_ZQ_CALIBRATION_FAILURE, T_WRDATA_EN_DDR3, T_WRDATA_EN_MASK, T_WRDATA_EN_OFFSET, TIMEOUT, mem_timings::timing_data, mem_timings::timing_power, mem_timings::timing_ref, mem_timings::timing_row, exynos5_dmc::timingdata, exynos5_dmc::timingpower, exynos5_dmc::timingref, exynos5_dmc::timingrow, udelay(), update_reset_dll(), val, write32(), and ZQ_CLK_DIV_EN.

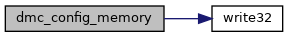

| void dmc_config_memory | ( | struct mem_timings * | mem, |

| struct exynos5_dmc * | dmc | ||

| ) |

Definition at line 157 of file dmc_common.c.

References DMC_MEMBASECONFIG0_VAL, DMC_MEMBASECONFIG1_VAL, exynos5_dmc::membaseconfig0, exynos5_dmc::membaseconfig1, mem_timings::memconfig, exynos5_dmc::memconfig0, exynos5_dmc::memconfig1, and write32().

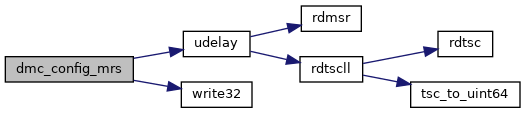

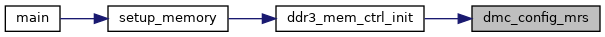

| void dmc_config_mrs | ( | struct mem_timings * | mem, |

| struct exynos5_dmc * | dmc | ||

| ) |

Definition at line 92 of file dmc_common.c.

References chip, mem_timings::chips_to_configure, DIRECT_CMD_CHANNEL_SHIFT, DIRECT_CMD_CHIP_SHIFT, mem_timings::direct_cmd_msr, DIRECT_CMD_NOP, DIRECT_CMD_ZQINIT, exynos5_dmc::directcmd, mem_timings::dmc_channels, mask, MEM_TIMINGS_MSR_COUNT, mem_timings::send_zq_init, udelay(), and write32().

Referenced by ddr3_mem_ctrl_init().

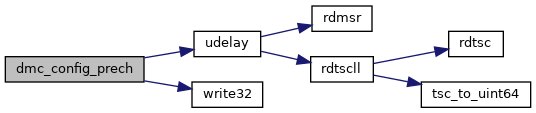

| void dmc_config_prech | ( | struct mem_timings * | mem, |

| struct exynos5_dmc * | dmc | ||

| ) |

Definition at line 139 of file dmc_common.c.

References chip, mem_timings::chips_per_channel, DIRECT_CMD_CHANNEL_SHIFT, DIRECT_CMD_CHIP_SHIFT, DIRECT_CMD_PALL, exynos5_dmc::directcmd, mem_timings::dmc_channels, mask, udelay(), and write32().

Referenced by ddr3_mem_ctrl_init().

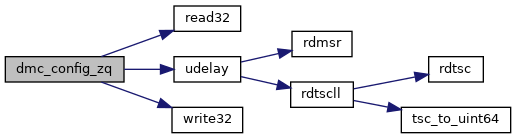

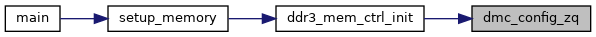

| int dmc_config_zq | ( | struct mem_timings * | mem, |

| struct exynos5_phy_control * | phy0_ctrl, | ||

| struct exynos5_phy_control * | phy1_ctrl | ||

| ) |

Definition at line 14 of file dmc_common.c.

References exynos5_phy_control::phy_con16, PHY_CON16_RESET_VAL, PHY_CON16_ZQ_MODE_DDS_SHIFT, PHY_CON16_ZQ_MODE_NOTERM_MASK, PHY_CON16_ZQ_MODE_TERM_SHIFT, exynos5_phy_control::phy_con17, read32(), udelay(), val, write32(), ZQ_CLK_DIV_EN, ZQ_DONE, ZQ_INIT_TIMEOUT, ZQ_MANUAL_STR, mem_timings::zq_mode_dds, mem_timings::zq_mode_noterm, and mem_timings::zq_mode_term.

Referenced by ddr3_mem_ctrl_init().

| int lpddr3_mem_ctrl_init | ( | int | reset | ) |

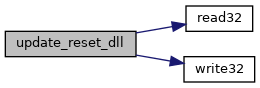

| void update_reset_dll | ( | struct exynos5_dmc * | dmc, |

| enum | ddr_mode | ||

| ) |

Definition at line 72 of file dmc_common.c.

References DDR_MODE_DDR3, DMC_CTRL_SHGATE, FP_RSYNC, MEM_TERM_EN, PHY_TERM_EN, exynos5_dmc::phycontrol0, read32(), val, and write32().

Referenced by ddr3_mem_ctrl_init().