|

coreboot

coreboot is an Open Source project aimed at replacing the proprietary BIOS found in most computers.

|

|

coreboot

coreboot is an Open Source project aimed at replacing the proprietary BIOS found in most computers.

|

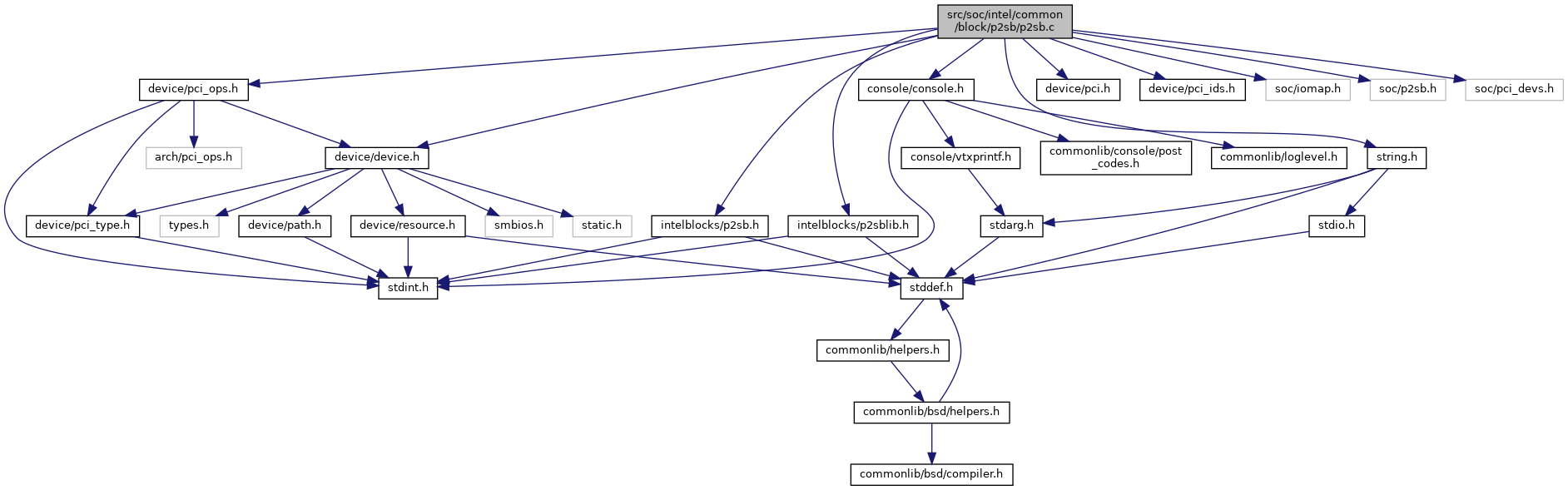

#include <device/pci_ops.h>#include <console/console.h>#include <device/device.h>#include <device/pci.h>#include <device/pci_ids.h>#include <intelblocks/p2sb.h>#include <intelblocks/p2sblib.h>#include <soc/iomap.h>#include <soc/p2sb.h>#include <soc/pci_devs.h>#include <string.h>

Go to the source code of this file.

Macros | |

| #define | __SIMPLE_DEVICE__ |

| #define | PCH_P2SB_EPMASK(mask_number) (PCH_P2SB_EPMASK0 + ((mask_number) * 4)) |

Functions | |

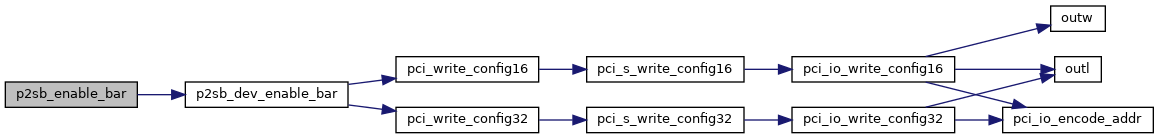

| void | p2sb_enable_bar (void) |

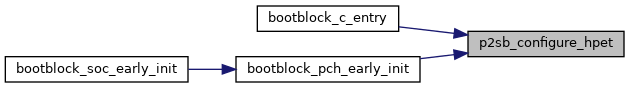

| void | p2sb_configure_hpet (void) |

| union p2sb_bdf | p2sb_get_hpet_bdf (void) |

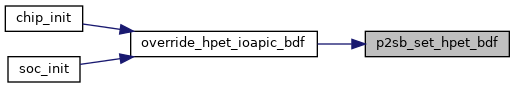

| void | p2sb_set_hpet_bdf (union p2sb_bdf bdf) |

| union p2sb_bdf | p2sb_get_ioapic_bdf (void) |

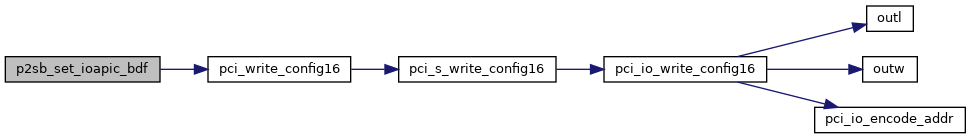

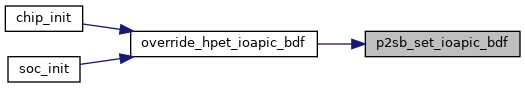

| void | p2sb_set_ioapic_bdf (union p2sb_bdf bdf) |

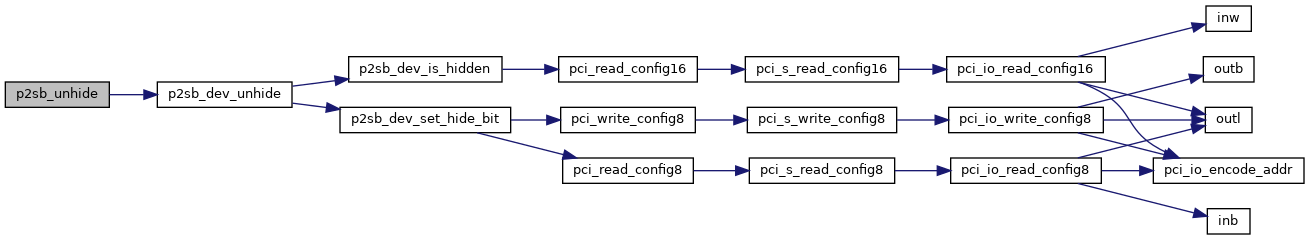

| void | p2sb_unhide (void) |

| void | p2sb_hide (void) |

| static void | p2sb_configure_endpoints (int epmask_id, uint32_t mask) |

| static void | p2sb_lock_endpoints (void) |

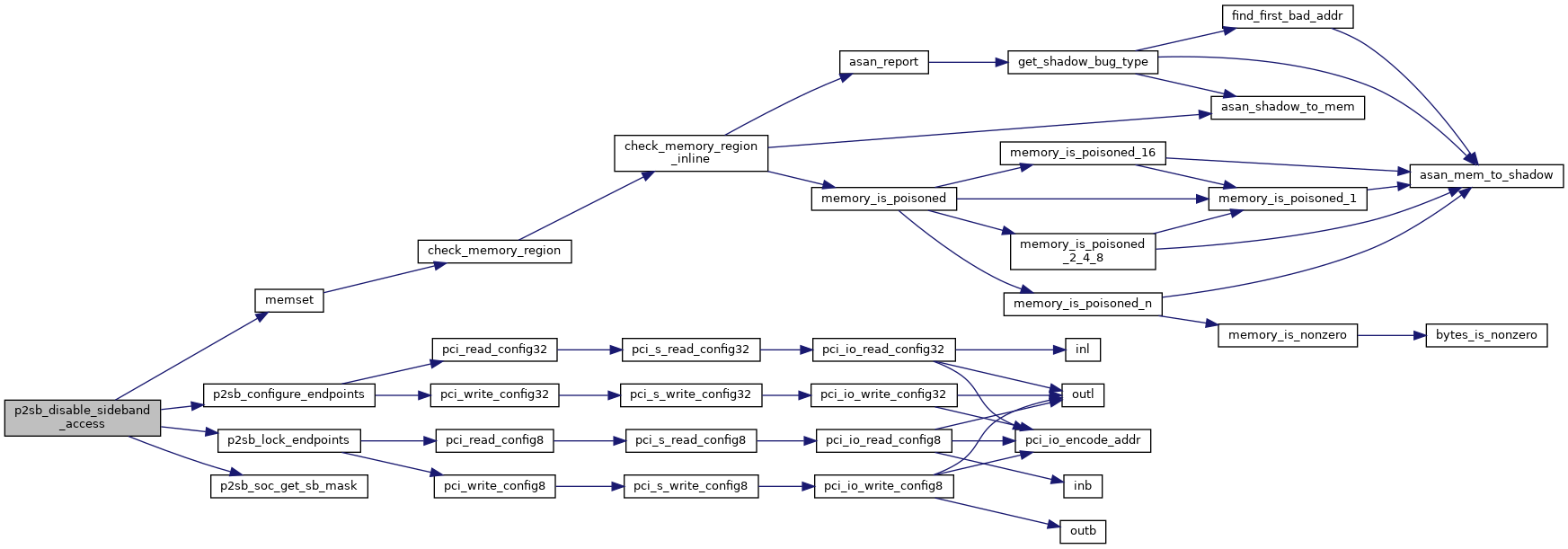

| void | p2sb_disable_sideband_access (void) |

| static void | read_resources (struct device *dev) |

Variables | |

| static const struct device_operations | device_ops |

| static const unsigned short | pci_device_ids [] |

| static const struct pci_driver pmc | __pci_driver |

| #define PCH_P2SB_EPMASK | ( | mask_number | ) | (PCH_P2SB_EPMASK0 + ((mask_number) * 4)) |

Definition at line 88 of file p2sb.c.

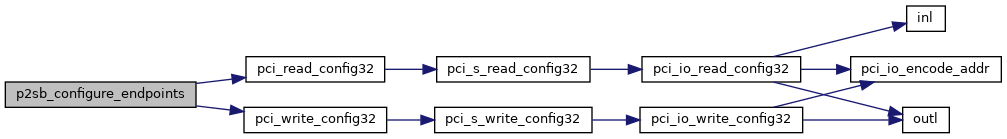

References mask, PCH_DEV_P2SB, PCH_P2SB_EPMASK, pci_read_config32(), and pci_write_config32().

Referenced by p2sb_disable_sideband_access().

Definition at line 29 of file p2sb.c.

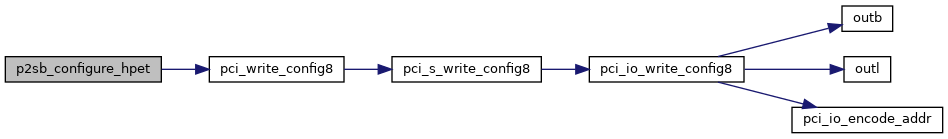

References HPTC_ADDR_ENABLE_BIT, HPTC_OFFSET, PCH_DEV_P2SB, and pci_write_config8().

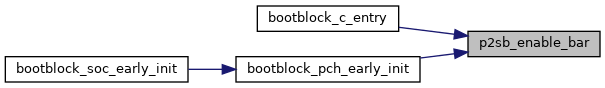

Referenced by bootblock_c_entry(), and bootblock_pch_early_init().

Definition at line 107 of file p2sb.c.

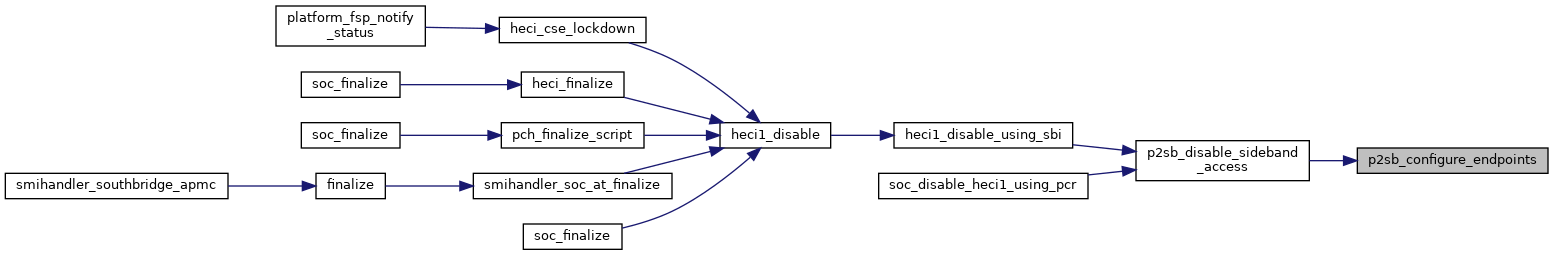

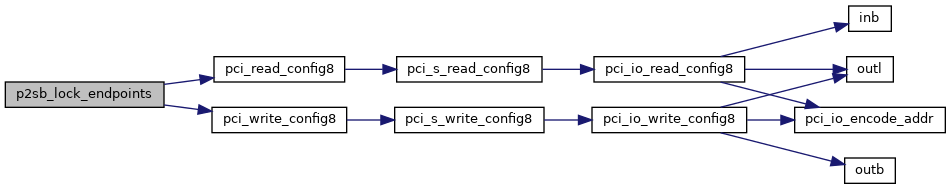

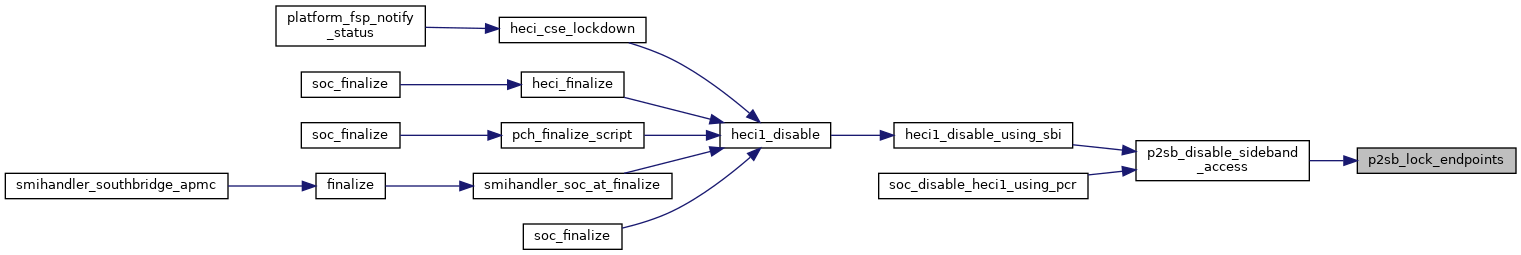

References ARRAY_SIZE, memset(), p2sb_configure_endpoints(), P2SB_EP_MASK_MAX_REG, p2sb_lock_endpoints(), and p2sb_soc_get_sb_mask().

Referenced by heci1_disable_using_sbi(), and soc_disable_heci1_using_pcr().

Definition at line 19 of file p2sb.c.

References P2SB_BAR, p2sb_dev_enable_bar(), and PCH_DEV_P2SB.

Referenced by bootblock_c_entry(), and bootblock_pch_early_init().

Definition at line 29 of file p2sb.c.

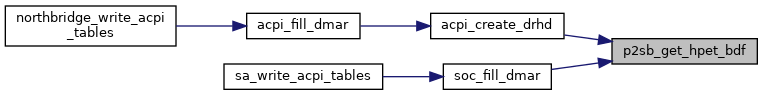

Referenced by acpi_create_drhd(), and soc_fill_dmar().

Definition at line 54 of file p2sb.c.

References PCH_DEV_P2SB, PCH_P2SB_HBDF, pci_write_config16(), and p2sb_bdf::raw.

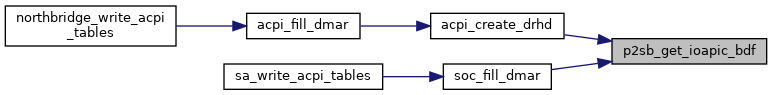

Referenced by acpi_create_drhd(), and soc_fill_dmar().

Definition at line 83 of file p2sb.c.

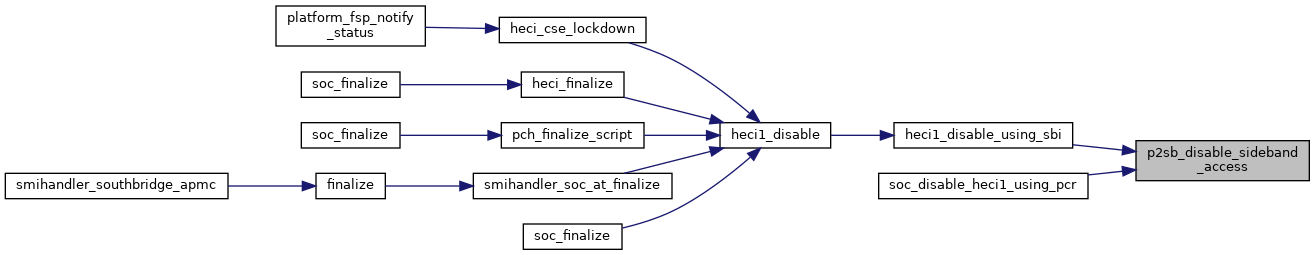

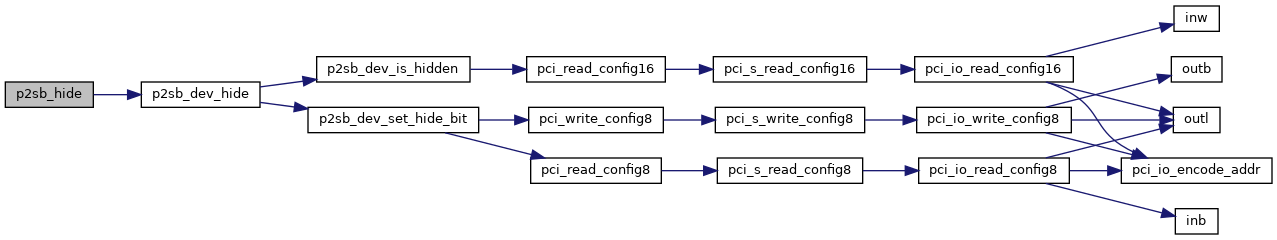

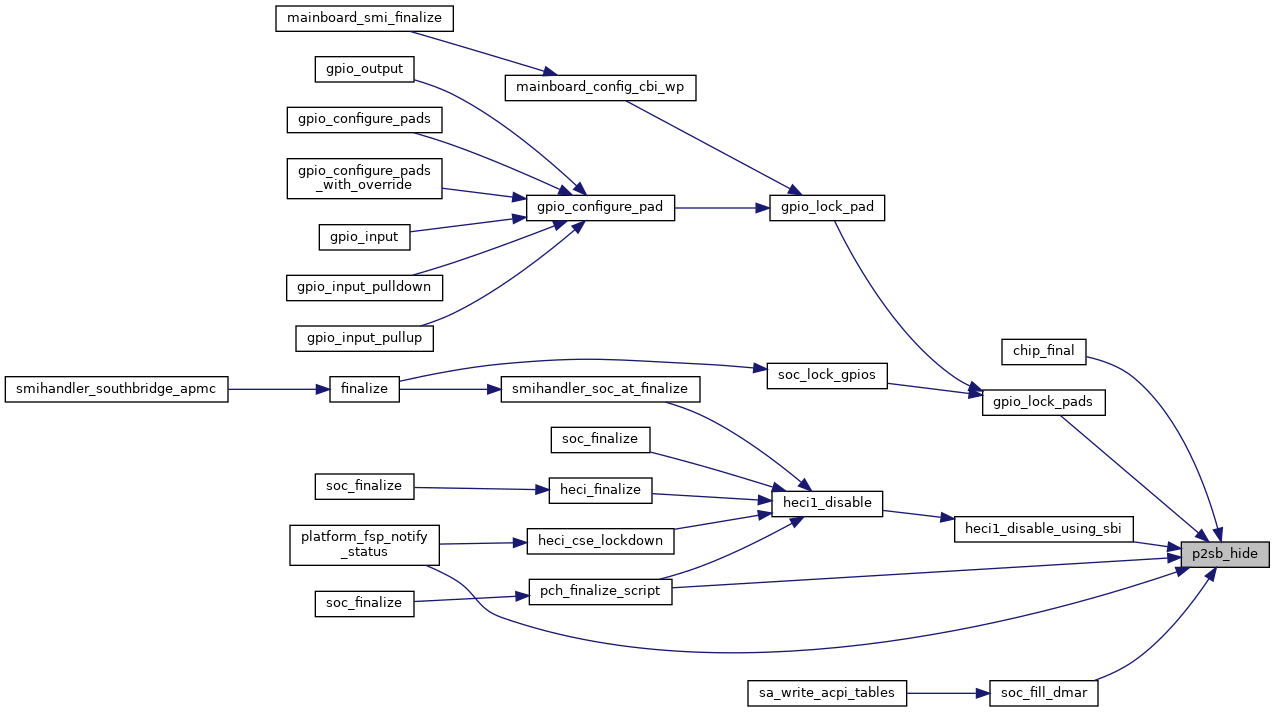

References p2sb_dev_hide(), and PCH_DEV_P2SB.

Referenced by chip_final(), gpio_lock_pads(), heci1_disable_using_sbi(), pch_finalize_script(), platform_fsp_notify_status(), and soc_fill_dmar().

Definition at line 97 of file p2sb.c.

References P2SB_E0_MASKLOCK, PCH_DEV_P2SB, PCH_P2SB_E0, pci_read_config8(), and pci_write_config8().

Referenced by p2sb_disable_sideband_access().

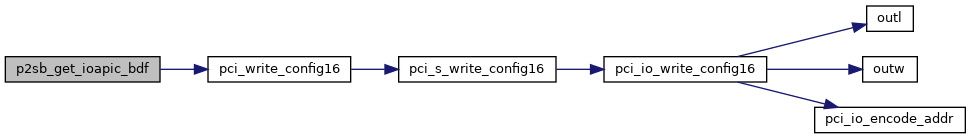

Definition at line 54 of file p2sb.c.

Referenced by override_hpet_ioapic_bdf().

Definition at line 73 of file p2sb.c.

References PCH_DEV_P2SB, PCH_P2SB_IBDF, pci_write_config16(), and p2sb_bdf::raw.

Referenced by override_hpet_ioapic_bdf().

Definition at line 78 of file p2sb.c.

References p2sb_dev_unhide(), and PCH_DEV_P2SB.

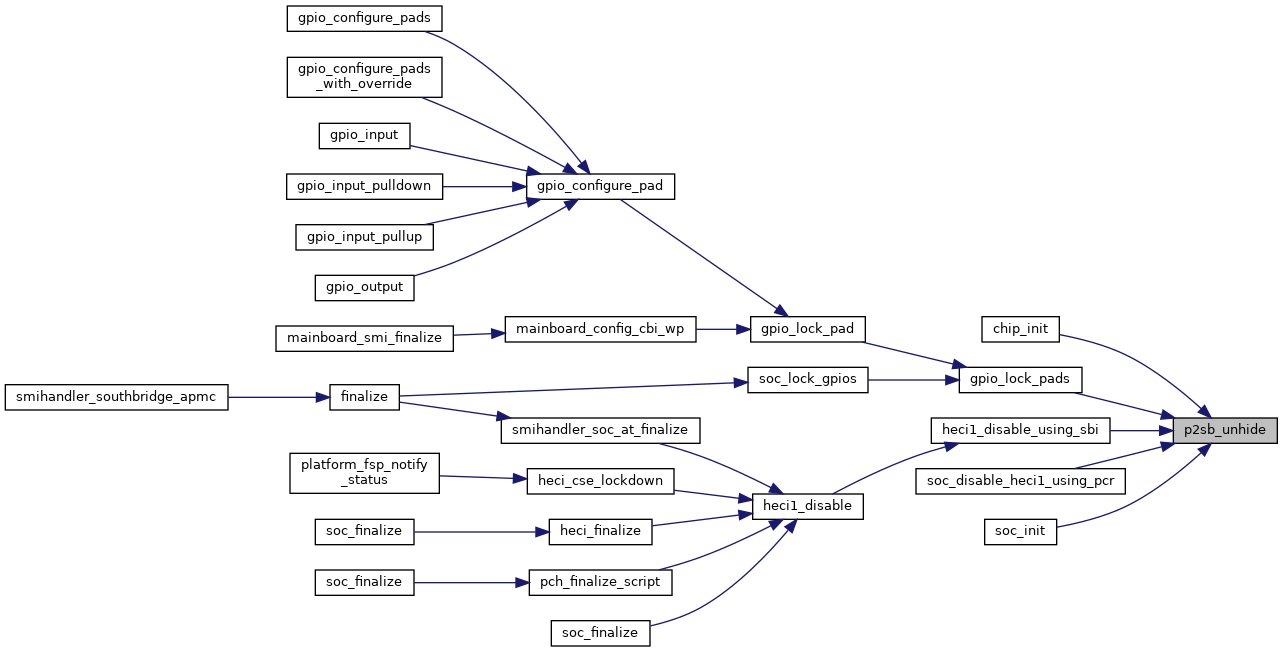

Referenced by chip_init(), gpio_lock_pads(), heci1_disable_using_sbi(), soc_disable_heci1_using_pcr(), and soc_init().

|

static |

|

static |

|

static |