|

coreboot

coreboot is an Open Source project aimed at replacing the proprietary BIOS found in most computers.

|

|

coreboot

coreboot is an Open Source project aimed at replacing the proprietary BIOS found in most computers.

|

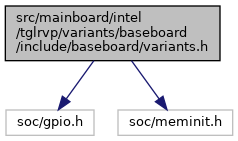

#include <soc/gpio.h>#include <soc/meminit.h>

Go to the source code of this file.

Functions | |

| const struct pad_config * | variant_gpio_table (size_t *num) |

| const struct pad_config * | variant_early_gpio_table (size_t *num) |

| size_t | variant_memory_sku (void) |

| const struct mb_cfg * | variant_memory_params (void) |

| const struct pad_config* variant_early_gpio_table | ( | size_t * | num | ) |

| const struct pad_config* variant_gpio_table | ( | size_t * | num | ) |

Definition at line 67 of file memory.c.

References ADL_M_LP4, ADL_M_LP5, ADL_N_LP5, ADL_P_DDR4_1, ADL_P_DDR4_2, ADL_P_DDR5_1, ADL_P_DDR5_2, ADL_P_LP4_1, ADL_P_LP4_2, ADL_P_LP5_1, ADL_P_LP5_2, adlm_lp4_mem_config, adlm_lp5_mem_config, adln_lp5_mem_config, baseboard_memcfg, board_id(), board_memcfg, ddr4_mem_config, ddr5_mem_config, die(), get_board_id(), lp5_mem_config, lpddr4_mem_config, and mem_config.

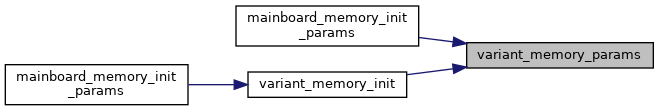

Referenced by mainboard_memory_init_params(), and variant_memory_init().

Definition at line 74 of file memory.c.

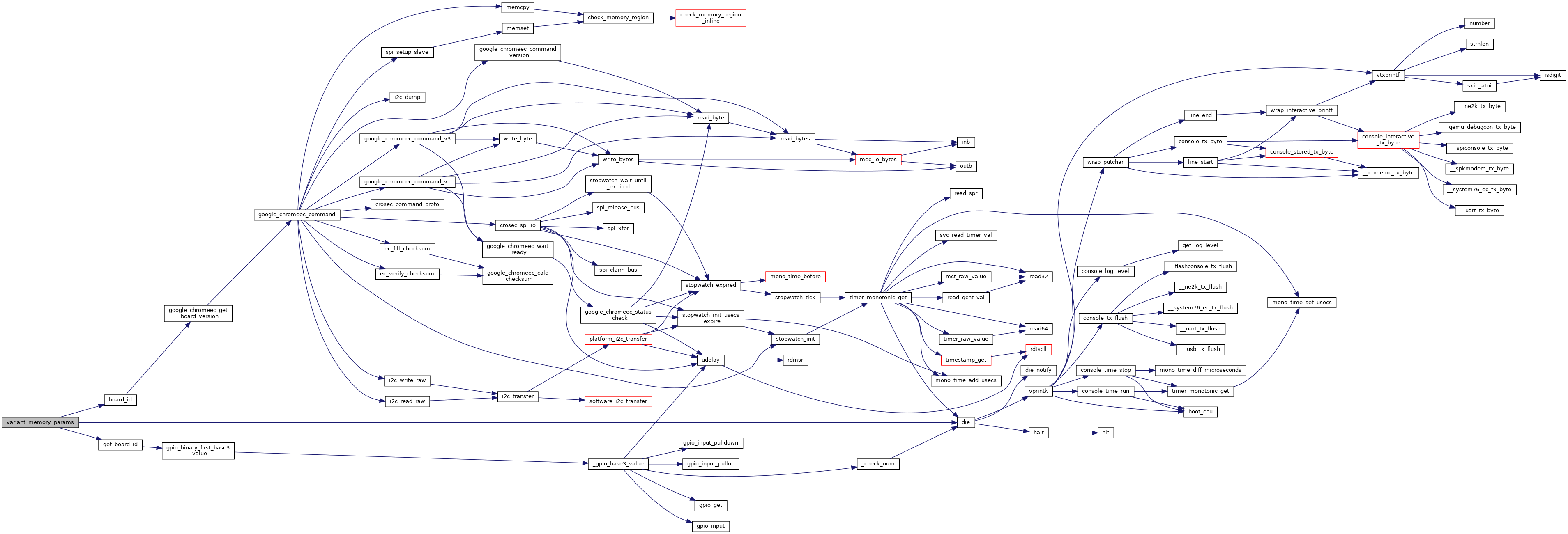

References ARRAY_SIZE, board_id(), BOARD_ID_UNKNOWN, gpio_base2_value(), GPIO_MEM_CONFIG_0, GPIO_MEM_CONFIG_1, GPIO_MEM_CONFIG_2, GPIO_MEM_CONFIG_3, GPIO_MEM_CONFIG_4, gpio_pullup_base2_value(), GPP_A19, GPP_A20, GPP_A7, GPP_E1, GPP_E11, GPP_E12, GPP_E2, GPP_E3, GPP_E7, MEM_CONFIG0, MEM_CONFIG1, MEM_CONFIG2, MEM_CONFIG3, spd_index, and val.

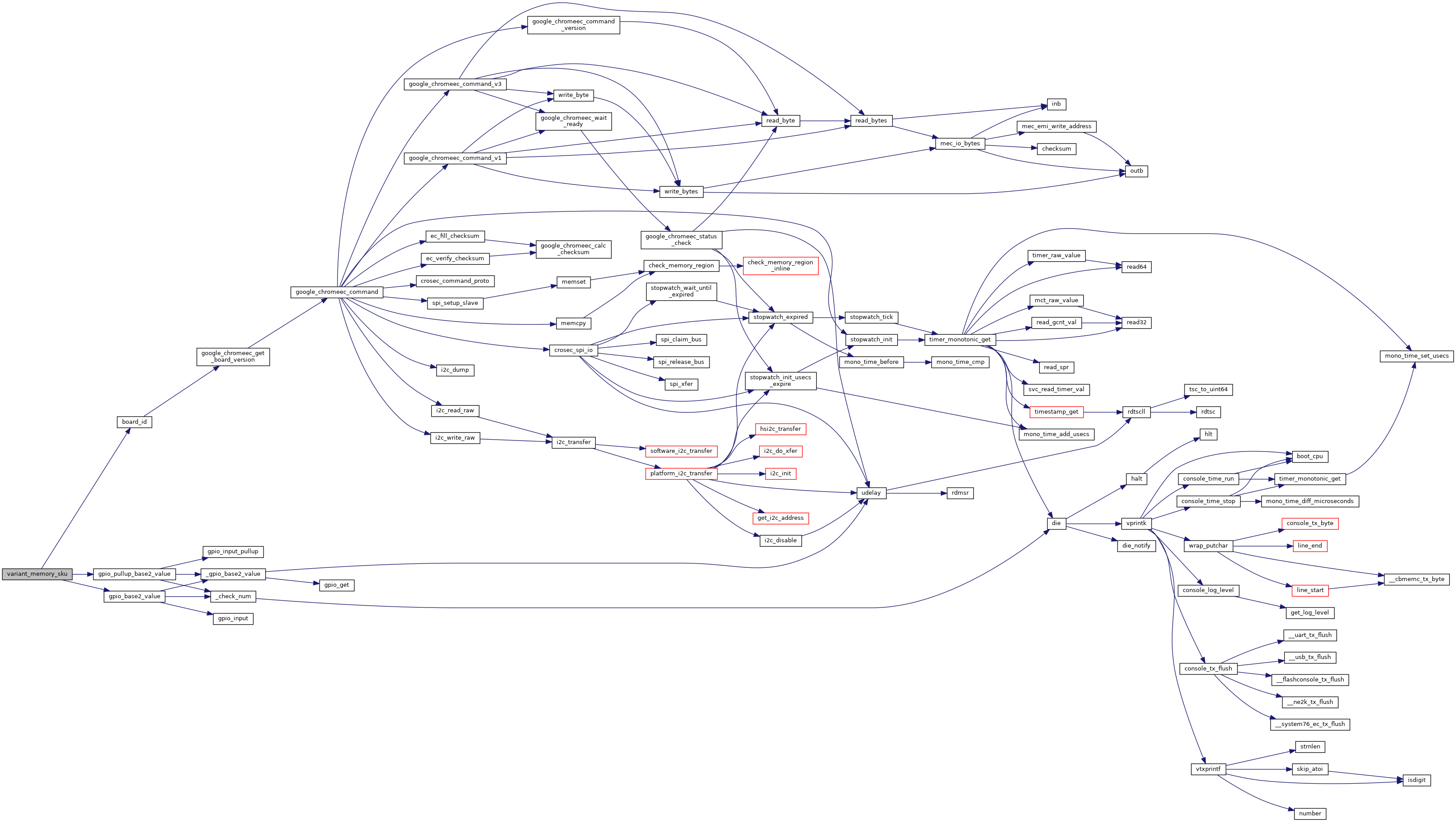

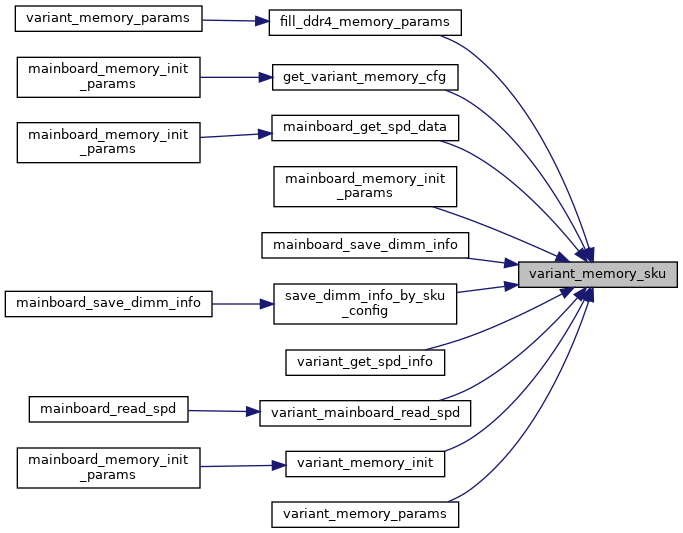

Referenced by fill_ddr4_memory_params(), get_variant_memory_cfg(), mainboard_get_spd_data(), mainboard_memory_init_params(), mainboard_save_dimm_info(), save_dimm_info_by_sku_config(), variant_get_spd_info(), variant_mainboard_read_spd(), variant_memory_init(), and variant_memory_params().