|

coreboot

coreboot is an Open Source project aimed at replacing the proprietary BIOS found in most computers.

|

|

coreboot

coreboot is an Open Source project aimed at replacing the proprietary BIOS found in most computers.

|

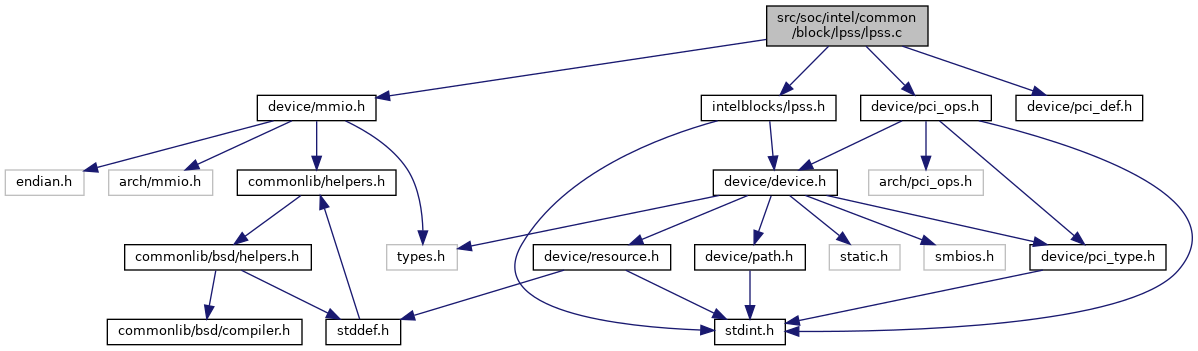

#include <device/mmio.h>#include <device/pci_def.h>#include <device/pci_ops.h>#include <intelblocks/lpss.h>

Go to the source code of this file.

Macros | |

| #define | LPSS_CLOCK_CTL_REG 0x200 |

| #define | LPSS_CNT_CLOCK_EN 1 |

| #define | LPSS_CNT_CLK_UPDATE (1 << 31) |

| #define | LPSS_CLOCK_DIV_N(n) (((n) & 0x7fff) << 16) |

| #define | LPSS_CLOCK_DIV_M(m) (((m) & 0x7fff) << 1) |

| #define | LPSS_RESET_CTL_REG 0x204 |

| #define | LPSS_CNT_RST_RELEASE 3 |

| #define | LPSS_DMA_RST_RELEASE (1 << 2) |

| #define | PME_CTRL_STATUS 0x84 |

| #define | POWER_STATE_MASK 3 |

Functions | |

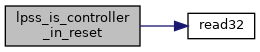

| bool | lpss_is_controller_in_reset (uintptr_t base) |

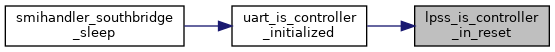

| void | lpss_reset_release (uintptr_t base) |

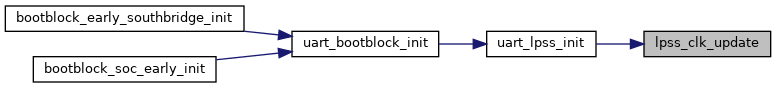

| void | lpss_clk_update (uintptr_t base, uint32_t clk_m_val, uint32_t clk_n_val) |

| void | lpss_set_power_state (pci_devfn_t devfn, enum lpss_pwr_state state) |

Definition at line 55 of file lpss.c.

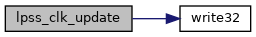

References addr, base, LPSS_CLOCK_CTL_REG, LPSS_CLOCK_DIV_M, LPSS_CLOCK_DIV_N, LPSS_CNT_CLK_UPDATE, LPSS_CNT_CLOCK_EN, and write32().

Referenced by uart_lpss_init().

Definition at line 36 of file lpss.c.

References addr, base, LPSS_CNT_RST_RELEASE, LPSS_RESET_CTL_REG, read32(), and val.

Referenced by uart_is_controller_initialized().

Definition at line 47 of file lpss.c.

References addr, base, LPSS_CNT_RST_RELEASE, LPSS_RESET_CTL_REG, and write32().

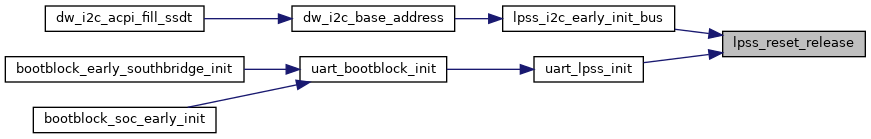

Referenced by lpss_i2c_early_init_bus(), and uart_lpss_init().

| void lpss_set_power_state | ( | pci_devfn_t | devfn, |

| enum lpss_pwr_state | state | ||

| ) |

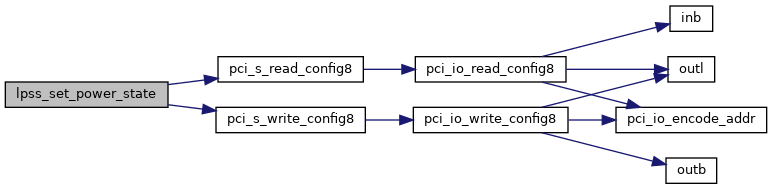

Definition at line 68 of file lpss.c.

References pci_s_read_config8(), pci_s_write_config8(), PME_CTRL_STATUS, and POWER_STATE_MASK.

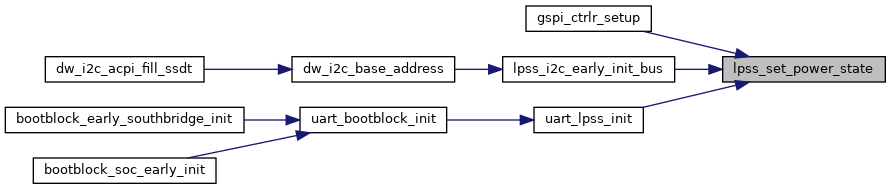

Referenced by gspi_ctrlr_setup(), lpss_i2c_early_init_bus(), and uart_lpss_init().