#include <types.h>

Go to the source code of this file.

|

| enum | me_bios_path {

ME_NORMAL_BIOS_PATH

, ME_S3WAKE_BIOS_PATH

, ME_ERROR_BIOS_PATH

, ME_RECOVERY_BIOS_PATH

,

ME_DISABLE_BIOS_PATH

, ME_FIRMWARE_UPDATE_BIOS_PATH

, ME_NORMAL_BIOS_PATH

, ME_S3WAKE_BIOS_PATH

,

ME_ERROR_BIOS_PATH

, ME_RECOVERY_BIOS_PATH

, ME_DISABLE_BIOS_PATH

, ME_FIRMWARE_UPDATE_BIOS_PATH

,

ME_NORMAL_BIOS_PATH

, ME_S3WAKE_BIOS_PATH

, ME_ERROR_BIOS_PATH

, ME_RECOVERY_BIOS_PATH

,

ME_DISABLE_BIOS_PATH

, ME_FIRMWARE_UPDATE_BIOS_PATH

, ME_NORMAL_BIOS_PATH

, ME_S3WAKE_BIOS_PATH

,

ME_ERROR_BIOS_PATH

, ME_RECOVERY_BIOS_PATH

, ME_DISABLE_BIOS_PATH

, ME_FIRMWARE_UPDATE_BIOS_PATH

} |

| |

◆ CBM_RR_GLOBAL_RESET

| #define CBM_RR_GLOBAL_RESET 0x01 |

Definition at line 206 of file me.h.

◆ GLOBAL_RESET_BIOS_MRC

| #define GLOBAL_RESET_BIOS_MRC 0x01 |

Definition at line 208 of file me.h.

◆ GLOBAL_RESET_BIOS_POST

| #define GLOBAL_RESET_BIOS_POST 0x02 |

Definition at line 209 of file me.h.

◆ GLOBAL_RESET_MEBX

| #define GLOBAL_RESET_MEBX 0x03 |

Definition at line 210 of file me.h.

◆ HECI_EOP_PERFORM_GLOBAL_RESET

| #define HECI_EOP_PERFORM_GLOBAL_RESET 0x1 |

Definition at line 204 of file me.h.

◆ HECI_EOP_STATUS_SUCCESS

| #define HECI_EOP_STATUS_SUCCESS 0x0 |

Definition at line 203 of file me.h.

◆ ME_DELAY

| #define ME_DELAY 10 /* 10 us */ |

Definition at line 9 of file me.h.

◆ ME_GMES_PHASE_BUP

| #define ME_GMES_PHASE_BUP 1 |

Definition at line 93 of file me.h.

◆ ME_GMES_PHASE_HOST

| #define ME_GMES_PHASE_HOST 6 |

Definition at line 98 of file me.h.

◆ ME_GMES_PHASE_MODULE

| #define ME_GMES_PHASE_MODULE 4 |

Definition at line 96 of file me.h.

◆ ME_GMES_PHASE_POLICY

| #define ME_GMES_PHASE_POLICY 3 |

Definition at line 95 of file me.h.

◆ ME_GMES_PHASE_ROM

| #define ME_GMES_PHASE_ROM 0 |

Definition at line 92 of file me.h.

◆ ME_GMES_PHASE_UKERNEL

| #define ME_GMES_PHASE_UKERNEL 2 |

Definition at line 94 of file me.h.

◆ ME_GMES_PHASE_UNKNOWN

| #define ME_GMES_PHASE_UNKNOWN 5 |

Definition at line 97 of file me.h.

◆ ME_HFS_ACK_CONTINUE

| #define ME_HFS_ACK_CONTINUE 7 |

Definition at line 50 of file me.h.

◆ ME_HFS_ACK_GBL_RESET

| #define ME_HFS_ACK_GBL_RESET 6 |

Definition at line 49 of file me.h.

◆ ME_HFS_ACK_NO_DID

| #define ME_HFS_ACK_NO_DID 0 |

Definition at line 43 of file me.h.

◆ ME_HFS_ACK_PWR_CYCLE

| #define ME_HFS_ACK_PWR_CYCLE 2 |

Definition at line 45 of file me.h.

◆ ME_HFS_ACK_RESET

| #define ME_HFS_ACK_RESET 1 |

Definition at line 44 of file me.h.

◆ ME_HFS_ACK_S3

Definition at line 46 of file me.h.

◆ ME_HFS_ACK_S4

Definition at line 47 of file me.h.

◆ ME_HFS_ACK_S5

Definition at line 48 of file me.h.

◆ ME_HFS_BIOS_DRAM_ACK

| #define ME_HFS_BIOS_DRAM_ACK 1 |

Definition at line 42 of file me.h.

◆ ME_HFS_CWS_INIT

| #define ME_HFS_CWS_INIT 1 |

Definition at line 21 of file me.h.

◆ ME_HFS_CWS_INVALID

| #define ME_HFS_CWS_INVALID 8 |

Definition at line 26 of file me.h.

◆ ME_HFS_CWS_NORMAL

| #define ME_HFS_CWS_NORMAL 5 |

Definition at line 23 of file me.h.

◆ ME_HFS_CWS_REC

Definition at line 22 of file me.h.

◆ ME_HFS_CWS_RESET

| #define ME_HFS_CWS_RESET 0 |

Definition at line 20 of file me.h.

◆ ME_HFS_CWS_TRANS

| #define ME_HFS_CWS_TRANS 7 |

Definition at line 25 of file me.h.

◆ ME_HFS_CWS_WAIT

| #define ME_HFS_CWS_WAIT 6 |

Definition at line 24 of file me.h.

◆ ME_HFS_ERROR_DEBUG

| #define ME_HFS_ERROR_DEBUG 4 |

Definition at line 36 of file me.h.

◆ ME_HFS_ERROR_IMAGE

| #define ME_HFS_ERROR_IMAGE 3 |

Definition at line 35 of file me.h.

◆ ME_HFS_ERROR_NONE

| #define ME_HFS_ERROR_NONE 0 |

Definition at line 33 of file me.h.

◆ ME_HFS_ERROR_UNCAT

| #define ME_HFS_ERROR_UNCAT 1 |

Definition at line 34 of file me.h.

◆ ME_HFS_MODE_DEBUG

| #define ME_HFS_MODE_DEBUG 2 |

Definition at line 38 of file me.h.

◆ ME_HFS_MODE_DIS

| #define ME_HFS_MODE_DIS 3 |

Definition at line 39 of file me.h.

◆ ME_HFS_MODE_NORMAL

| #define ME_HFS_MODE_NORMAL 0 |

Definition at line 37 of file me.h.

◆ ME_HFS_MODE_OVER_JMPR

| #define ME_HFS_MODE_OVER_JMPR 4 |

Definition at line 40 of file me.h.

◆ ME_HFS_MODE_OVER_MEI

| #define ME_HFS_MODE_OVER_MEI 5 |

Definition at line 41 of file me.h.

◆ ME_HFS_STATE_BRINGUP

| #define ME_HFS_STATE_BRINGUP 6 |

Definition at line 31 of file me.h.

◆ ME_HFS_STATE_ERROR

| #define ME_HFS_STATE_ERROR 7 |

Definition at line 32 of file me.h.

◆ ME_HFS_STATE_M0

| #define ME_HFS_STATE_M0 5 |

Definition at line 30 of file me.h.

◆ ME_HFS_STATE_M0_UMA

| #define ME_HFS_STATE_M0_UMA 1 |

Definition at line 28 of file me.h.

◆ ME_HFS_STATE_M3

| #define ME_HFS_STATE_M3 4 |

Definition at line 29 of file me.h.

◆ ME_HFS_STATE_PREBOOT

| #define ME_HFS_STATE_PREBOOT 0 |

Definition at line 27 of file me.h.

◆ ME_INIT_DONE

Definition at line 79 of file me.h.

◆ ME_INIT_STATUS_ERROR

| #define ME_INIT_STATUS_ERROR 2 |

Definition at line 82 of file me.h.

◆ ME_INIT_STATUS_NOMEM

| #define ME_INIT_STATUS_NOMEM 1 |

Definition at line 81 of file me.h.

◆ ME_INIT_STATUS_SUCCESS

| #define ME_INIT_STATUS_SUCCESS 0 |

Definition at line 80 of file me.h.

◆ ME_RETRY

| #define ME_RETRY 100000 /* 1 second */ |

Definition at line 8 of file me.h.

◆ MEI_ADDRESS_AMT

| #define MEI_ADDRESS_AMT 0x02 |

Definition at line 151 of file me.h.

◆ MEI_ADDRESS_CORE

| #define MEI_ADDRESS_CORE 0x01 |

Definition at line 150 of file me.h.

◆ MEI_ADDRESS_ICC

| #define MEI_ADDRESS_ICC 0x08 |

Definition at line 155 of file me.h.

◆ MEI_ADDRESS_MKHI

| #define MEI_ADDRESS_MKHI 0x07 |

Definition at line 154 of file me.h.

◆ MEI_ADDRESS_RESERVED

| #define MEI_ADDRESS_RESERVED 0x03 |

Definition at line 152 of file me.h.

◆ MEI_ADDRESS_THERMAL

| #define MEI_ADDRESS_THERMAL 0x09 |

Definition at line 156 of file me.h.

◆ MEI_ADDRESS_WDT

| #define MEI_ADDRESS_WDT 0x04 |

Definition at line 153 of file me.h.

◆ MEI_H_CB_WW

Definition at line 133 of file me.h.

◆ MEI_H_CSR

Definition at line 134 of file me.h.

◆ MEI_HOST_ADDRESS

| #define MEI_HOST_ADDRESS 0 |

Definition at line 158 of file me.h.

◆ MEI_ME_CB_RW

| #define MEI_ME_CB_RW 0x08 |

Definition at line 135 of file me.h.

◆ MEI_ME_CSR_HA

| #define MEI_ME_CSR_HA 0x0c |

Definition at line 136 of file me.h.

◆ MKHI_END_OF_POST

| #define MKHI_END_OF_POST 0x0c |

Definition at line 181 of file me.h.

◆ MKHI_FEATURE_OVERRIDE

| #define MKHI_FEATURE_OVERRIDE 0x14 |

Definition at line 182 of file me.h.

◆ MKHI_FWCAPS_GET_RULE

| #define MKHI_FWCAPS_GET_RULE 0x02 |

Definition at line 175 of file me.h.

◆ MKHI_GET_FW_VERSION

| #define MKHI_GET_FW_VERSION 0x02 |

Definition at line 179 of file me.h.

◆ MKHI_GLOBAL_RESET

| #define MKHI_GLOBAL_RESET 0x0b |

Definition at line 173 of file me.h.

◆ MKHI_GROUP_ID_CBM

| #define MKHI_GROUP_ID_CBM 0x00 |

Definition at line 168 of file me.h.

◆ MKHI_GROUP_ID_FWCAPS

| #define MKHI_GROUP_ID_FWCAPS 0x03 |

Definition at line 169 of file me.h.

◆ MKHI_GROUP_ID_GEN

| #define MKHI_GROUP_ID_GEN 0xff |

Definition at line 171 of file me.h.

◆ MKHI_GROUP_ID_MDES

| #define MKHI_GROUP_ID_MDES 0x08 |

Definition at line 170 of file me.h.

◆ MKHI_MDES_ENABLE

| #define MKHI_MDES_ENABLE 0x09 |

Definition at line 177 of file me.h.

◆ MKHI_SET_UMA

| #define MKHI_SET_UMA 0x08 |

Definition at line 180 of file me.h.

◆ PCI_CPU_DEVICE

| #define PCI_CPU_DEVICE PCI_DEV(0,0,0) |

Definition at line 15 of file me.h.

◆ PCI_CPU_MEBASE_H

| #define PCI_CPU_MEBASE_H 0x74 /* Set by MRC */ |

Definition at line 17 of file me.h.

◆ PCI_CPU_MEBASE_L

| #define PCI_CPU_MEBASE_L 0x70 /* Set by MRC */ |

Definition at line 16 of file me.h.

◆ PCI_ME_EXT_SHA1

| #define PCI_ME_EXT_SHA1 0x00 |

Definition at line 118 of file me.h.

◆ PCI_ME_EXT_SHA256

| #define PCI_ME_EXT_SHA256 0x02 |

Definition at line 119 of file me.h.

◆ PCI_ME_GMES

Definition at line 91 of file me.h.

◆ PCI_ME_H_GS

Definition at line 78 of file me.h.

◆ PCI_ME_HER

| #define PCI_ME_HER |

( |

|

x | ) |

(0xc0+(4*(x))) |

Definition at line 120 of file me.h.

◆ PCI_ME_HERES

| #define PCI_ME_HERES 0xbc |

Definition at line 117 of file me.h.

◆ PCI_ME_HFS

Definition at line 19 of file me.h.

◆ PCI_ME_UMA

Definition at line 68 of file me.h.

◆ me_bios_path

| Enumerator |

|---|

| ME_NORMAL_BIOS_PATH | |

| ME_S3WAKE_BIOS_PATH | |

| ME_ERROR_BIOS_PATH | |

| ME_RECOVERY_BIOS_PATH | |

| ME_DISABLE_BIOS_PATH | |

| ME_FIRMWARE_UPDATE_BIOS_PATH | |

| ME_NORMAL_BIOS_PATH | |

| ME_S3WAKE_BIOS_PATH | |

| ME_ERROR_BIOS_PATH | |

| ME_RECOVERY_BIOS_PATH | |

| ME_DISABLE_BIOS_PATH | |

| ME_FIRMWARE_UPDATE_BIOS_PATH | |

| ME_NORMAL_BIOS_PATH | |

| ME_S3WAKE_BIOS_PATH | |

| ME_ERROR_BIOS_PATH | |

| ME_RECOVERY_BIOS_PATH | |

| ME_DISABLE_BIOS_PATH | |

| ME_FIRMWARE_UPDATE_BIOS_PATH | |

| ME_NORMAL_BIOS_PATH | |

| ME_S3WAKE_BIOS_PATH | |

| ME_ERROR_BIOS_PATH | |

| ME_RECOVERY_BIOS_PATH | |

| ME_DISABLE_BIOS_PATH | |

| ME_FIRMWARE_UPDATE_BIOS_PATH | |

Definition at line 217 of file me.h.

◆ intel_early_me_init()

| int intel_early_me_init |

( |

void |

| ) |

|

◆ intel_early_me_init_done()

| int intel_early_me_init_done |

( |

u8 |

status | ) |

|

◆ intel_early_me_status()

◆ intel_early_me_uma_size()

| int intel_early_me_uma_size |

( |

void |

| ) |

|

◆ intel_me_status()

◆ setup_heci_uma()

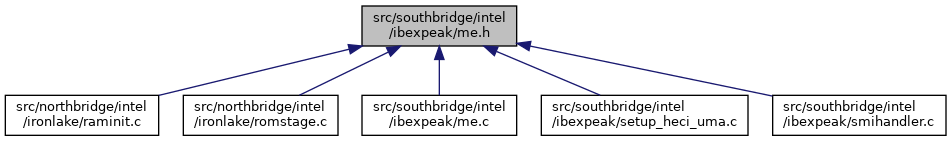

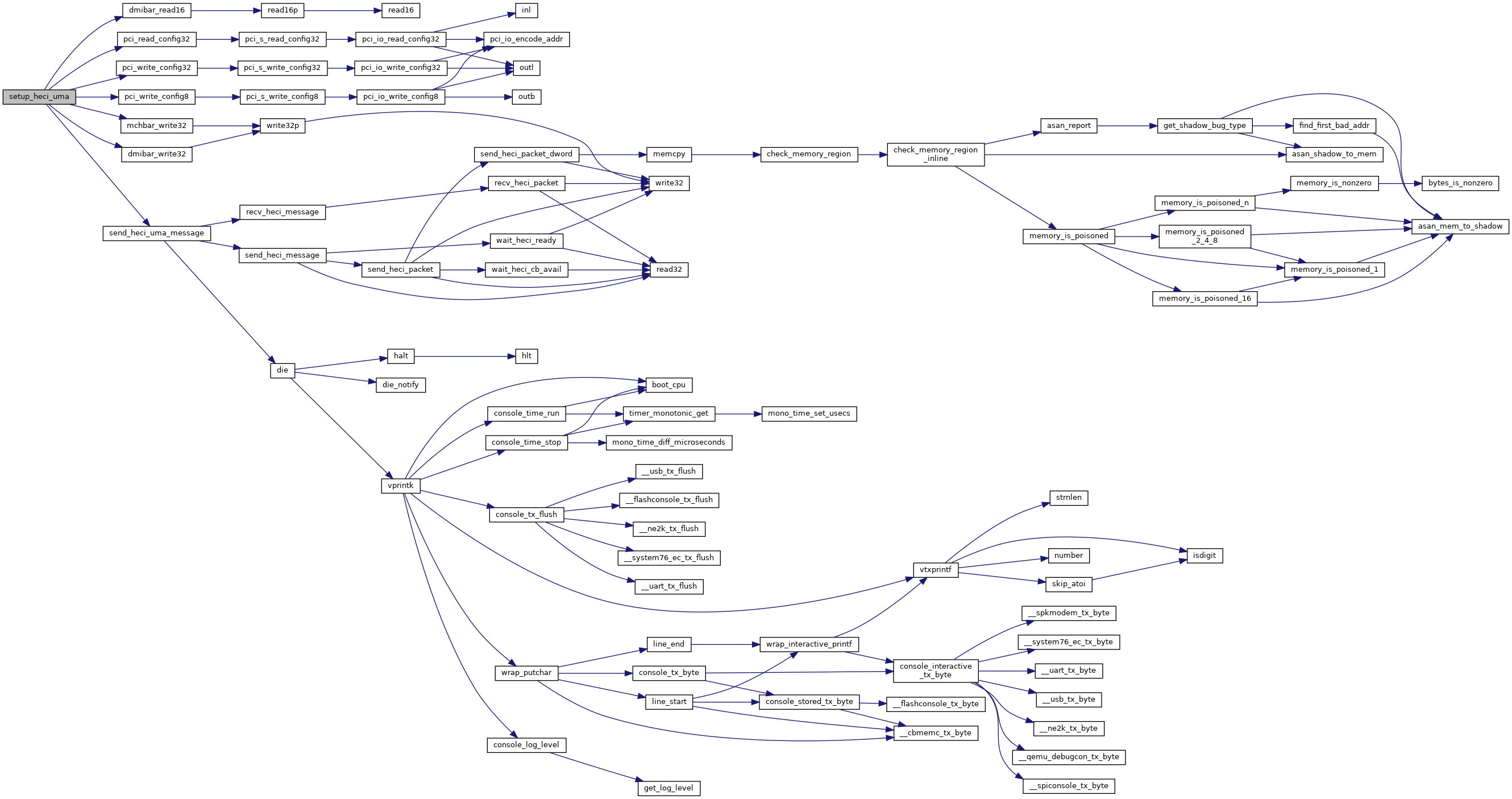

Definition at line 201 of file setup_heci_uma.c.

References dmibar_clrbits32, dmibar_read16(), dmibar_write32(), DMIVC0RCTL, DMIVC1RCTL, DMIVCMRCTL, DMIVCMRSTS, DMIVCPRCTL, HECIDEV, mchbar_write32(), pci_read_config32(), pci_write_config32(), pci_write_config8(), RCBA16, RCBA32, send_heci_uma_message(), and VCMNP.

Referenced by raminit().

◆ __packed