|

coreboot

coreboot is an Open Source project aimed at replacing the proprietary BIOS found in most computers.

|

|

coreboot

coreboot is an Open Source project aimed at replacing the proprietary BIOS found in most computers.

|

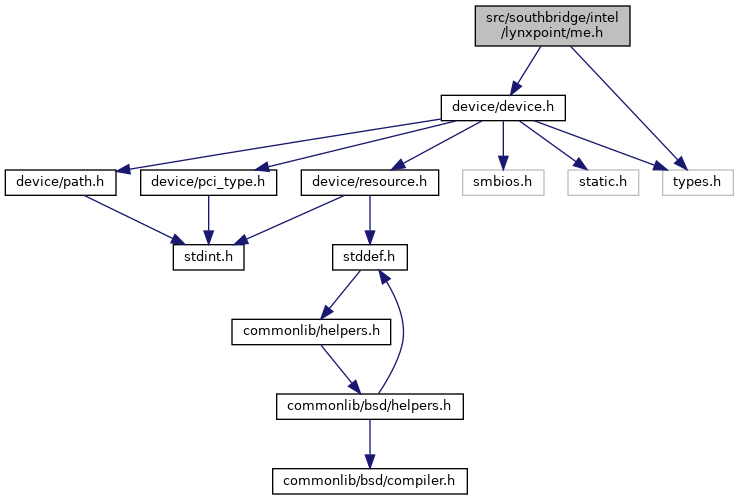

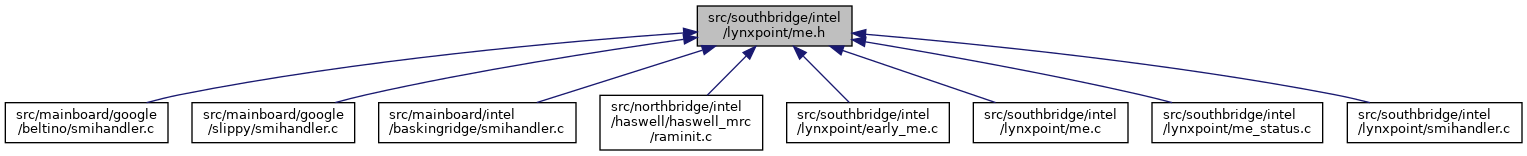

Go to the source code of this file.

Data Structures | |

| union | me_hfs |

| struct | me_hfs::__packed |

| union | me_uma |

| struct | me_uma::__packed |

| union | me_did |

| struct | me_did::__packed |

| union | me_hfs2 |

| struct | me_hfs2::__packed |

| union | me_heres |

| struct | me_heres::__packed |

| union | mei_csr |

| struct | mei_csr::__packed |

| union | mei_header |

| struct | mei_header::__packed |

| struct | mkhi_header |

| struct | me_fw_version |

| struct | icc_header |

| struct | icc_clock_enables_msg |

| struct | me_global_reset |

| union | mbp_header |

| struct | mbp_header::__packed |

| struct | mbp_item_header |

| struct | mbp_fw_version_name |

| struct | mbp_mefwcaps |

| struct | mbp_rom_bist_data |

| struct | mbp_platform_key |

| struct | mbp_me_firmware_type |

| struct | mbp_plat_type |

| struct | icc_address_mask |

| struct | mbp_icc_profile |

| struct | tdt_state_flag |

| struct | mbp_at_state |

| struct | mbp_plat_time |

| struct | mbp_nfc_data |

| struct | me_bios_payload |

| struct | me_fwcaps |

Functions | |

| void | intel_me_status (union me_hfs hfs, union me_hfs2 hfs2) |

| void | intel_early_me_status (void) |

| int | intel_early_me_init (void) |

| int | intel_early_me_uma_size (void) |

| int | intel_early_me_init_done (u8 status) |

| void | intel_me_finalize (struct device *dev) |

Variables | |

| struct mkhi_header | __packed |

| #define MBP_IDENT | ( | appid, | |

| item | |||

| ) | MBP_MAKE_IDENT(MBP_APPID_##appid, MBP_##appid##_##item##_ITEM) |

| #define ME_HFS2_STATE_BUP_CPU_RESET_DID_TIMEOUT_MEM_MISSING 0x17 |

| enum me_bios_path |

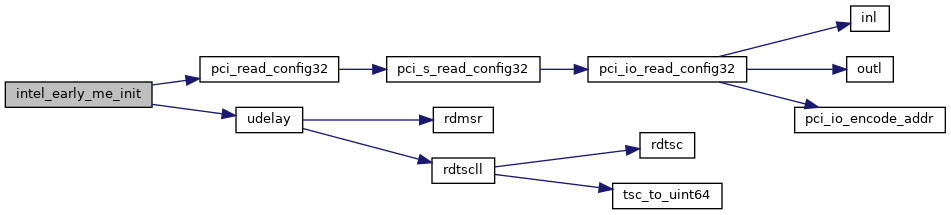

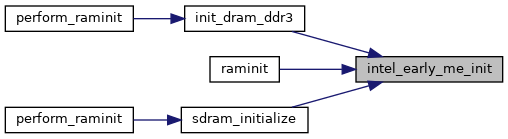

| int intel_early_me_init | ( | void | ) |

Definition at line 43 of file early_me.c.

References BIOS_ERR, BIOS_INFO, BIOS_WARNING, count, me_hfs::fpt_bad, ME_DELAY, ME_RETRY, PCH_ME_DEV, PCI_ME_HFS, PCI_ME_UMA, pci_read_config32(), printk, me_hfs::raw, me_uma::raw, udelay(), and me_uma::valid.

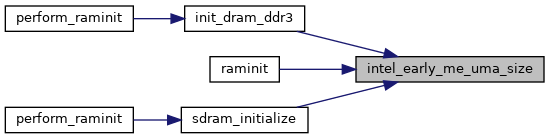

Referenced by init_dram_ddr3(), raminit(), and sdram_initialize().

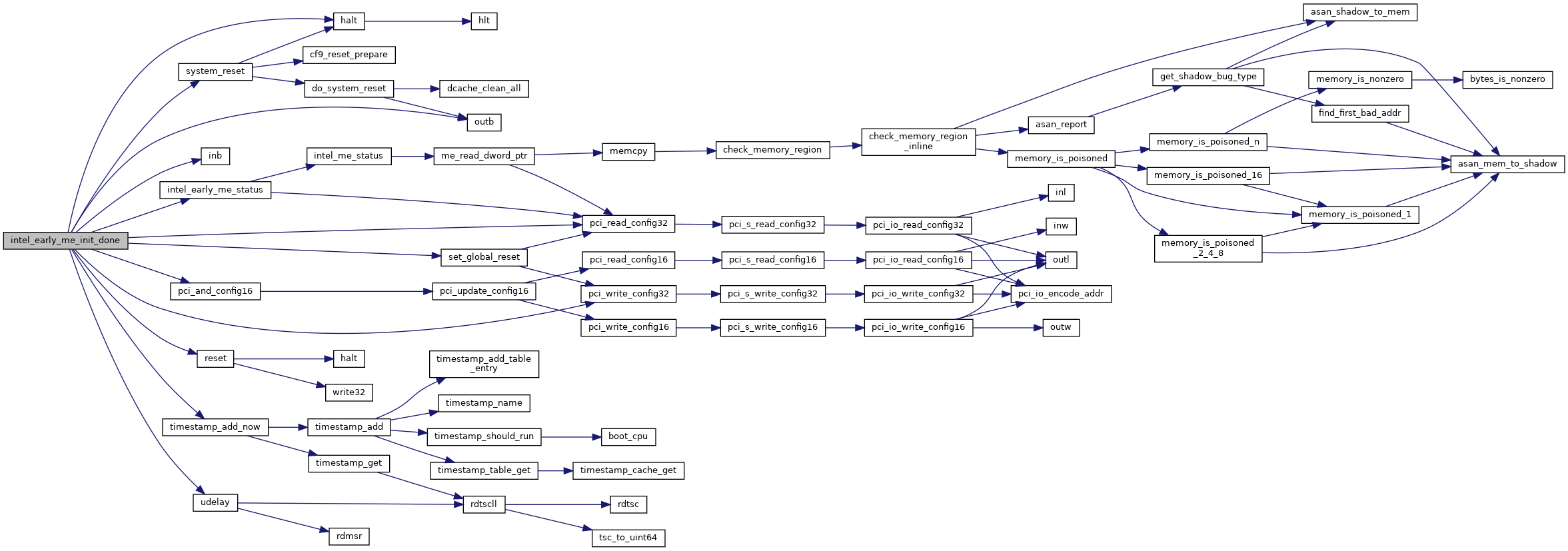

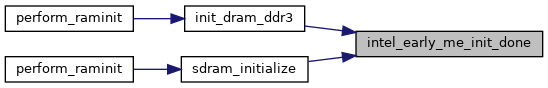

| int intel_early_me_init_done | ( | u8 | status | ) |

Definition at line 88 of file early_me.c.

References me_hfs::ack_data, BIOS_DEBUG, BIOS_ERR, me_hfs::bios_msg_ack, BIOS_NOTICE, count, did, GEN_PMCON_2, halt(), inb(), intel_early_me_status(), me_ack_values, ME_DELAY, ME_HFS_ACK_CONTINUE, ME_HFS_ACK_GBL_RESET, ME_HFS_ACK_NO_DID, ME_HFS_ACK_PWR_CYCLE, ME_HFS_ACK_RESET, ME_HFS_ACK_S3, ME_HFS_ACK_S4, ME_HFS_ACK_S5, ME_HFS_BIOS_DRAM_ACK, ME_HFS_MODE_DEBUG, ME_HFS_MODE_NORMAL, ME_INIT_DONE, ME_INIT_STATUS_ERROR, ME_INIT_STATUS_NOMEM, ME_RETRY, outb(), PCH_LPC_DEV, PCH_ME_DEV, pci_and_config16(), PCI_CPU_DEVICE, PCI_CPU_MEBASE_H, PCI_CPU_MEBASE_L, PCI_ME_GMES, PCI_ME_H_GS, PCI_ME_HFS, pci_read_config32(), pci_write_config32(), printk, me_hfs::raw, reset(), set_global_reset(), me_did::status, system_reset(), timestamp_add_now(), TS_ME_INFORM_DRAM_END, TS_ME_INFORM_DRAM_START, and udelay().

Referenced by init_dram_ddr3(), and sdram_initialize().

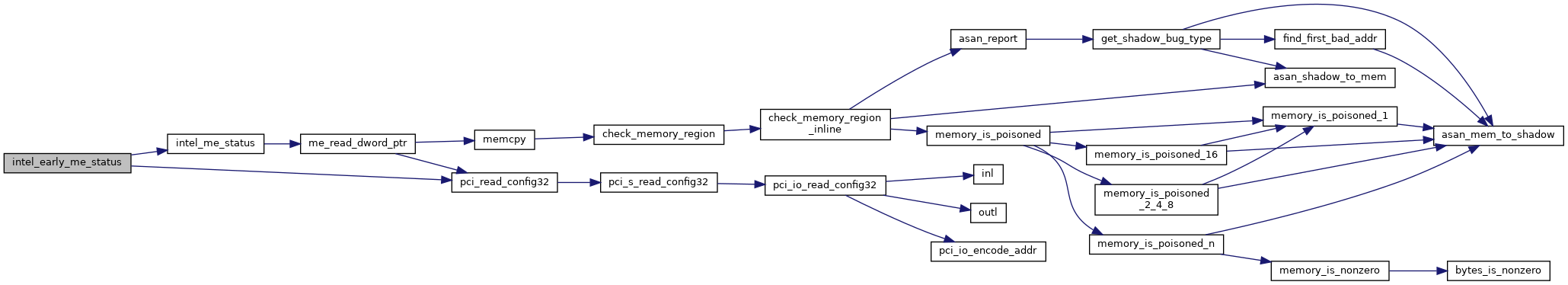

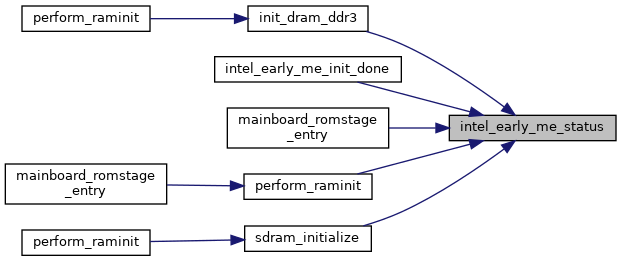

Definition at line 26 of file early_me.c.

References BIOS_DEBUG, intel_me_status(), PCH_ME_DEV, PCI_ME_GMES, PCI_ME_HFS, PCI_ME_HFS2, pci_read_config32(), PCI_VENDOR_ID, printk, me_hfs::raw, me_gmes::raw, and me_hfs2::raw.

Referenced by init_dram_ddr3(), intel_early_me_init_done(), mainboard_romstage_entry(), perform_raminit(), and sdram_initialize().

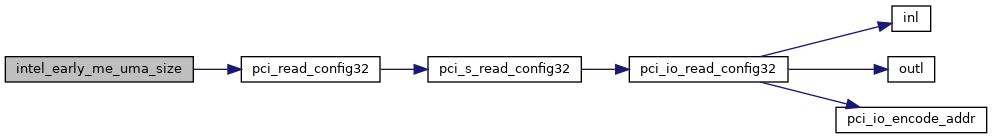

| int intel_early_me_uma_size | ( | void | ) |

Definition at line 74 of file early_me.c.

References BIOS_DEBUG, PCH_ME_DEV, PCI_ME_UMA, pci_read_config32(), printk, me_uma::raw, me_uma::size, and me_uma::valid.

Referenced by init_dram_ddr3(), raminit(), and sdram_initialize().

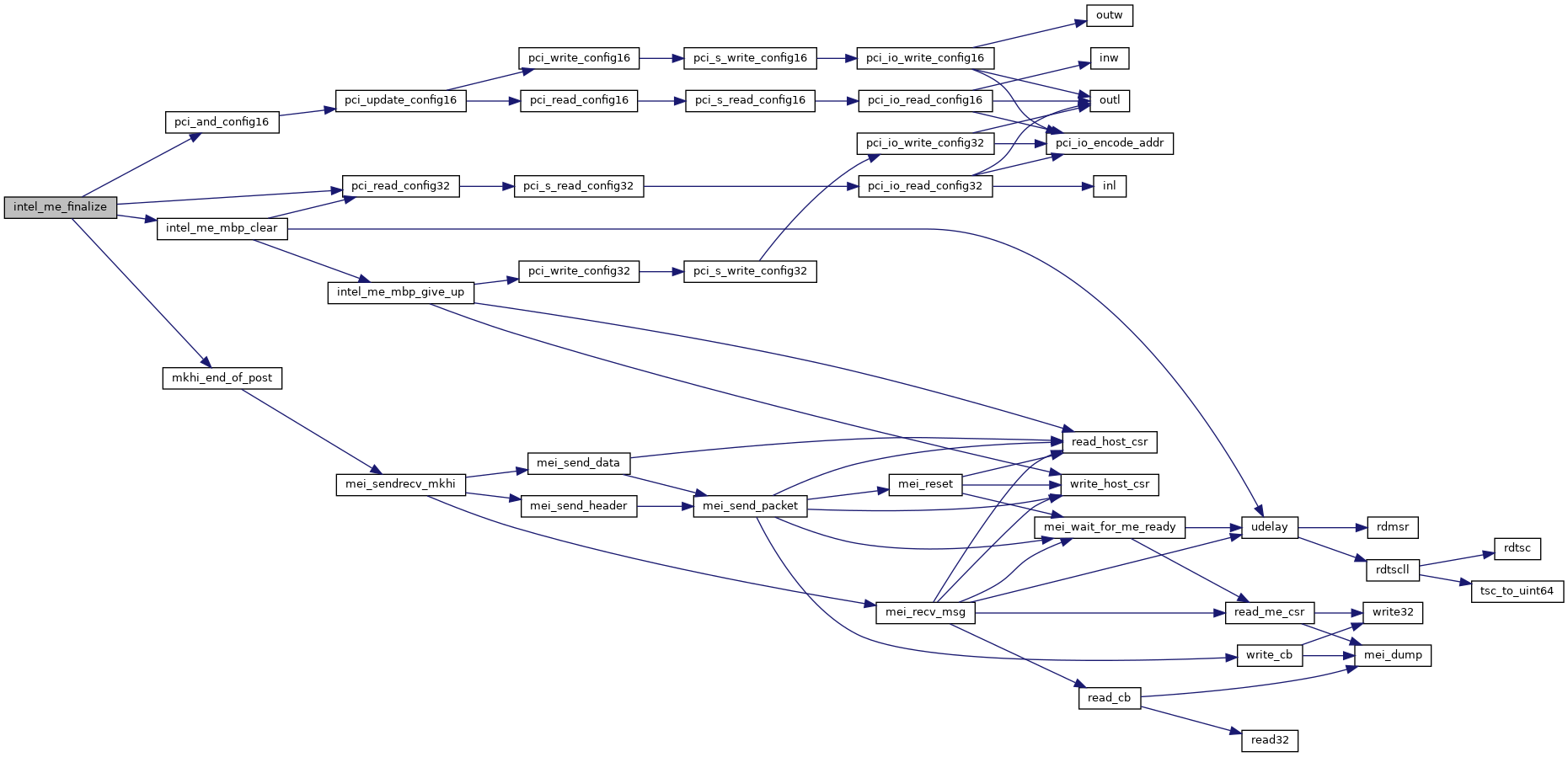

Definition at line 519 of file me.c.

References FD2, me_hfs::fpt_bad, intel_me_mbp_clear(), ME_HFS_CWS_NORMAL, ME_HFS_MODE_NORMAL, mei_base_address, mkhi_end_of_post(), me_hfs::operation_mode, PCH_DISABLE_MEI1, pci_and_config16(), PCI_BASE_ADDRESS_0, PCI_BASE_ADDRESS_MEM_ATTR_MASK, PCI_COMMAND, PCI_COMMAND_IO, PCI_COMMAND_MASTER, PCI_COMMAND_MEMORY, PCI_ME_HFS, pci_read_config32(), me_hfs::raw, RCBA32_OR, and me_hfs::working_state.

Definition at line 126 of file me_status.c.

References ARRAY_SIZE, BIOS_DEBUG, me_hfs::boot_options_present, me_hfs2::current_pmevent, me_hfs2::current_state, me_hfs::error_code, me_hfs::fpt_bad, me_hfs::ft_bup_ld_flr, me_hfs::fw_init_complete, me_cws_values, me_error_values, ME_HFS2_PHASE_BUP, ME_HFS2_PHASE_HOST_COMM, ME_HFS2_PHASE_POLICY, ME_HFS2_PHASE_ROM, me_opmode_values, me_opstate_values, me_pmevent_values, me_progress_bup_values, me_progress_policy_values, me_progress_rom_values, me_progress_values, me_hfs::mfg_mode, me_hfs::operation_mode, me_hfs::operation_state, printk, me_hfs2::progress_code, me_hfs::update_in_progress, and me_hfs::working_state.