|

coreboot

coreboot is an Open Source project aimed at replacing the proprietary BIOS found in most computers.

|

|

coreboot

coreboot is an Open Source project aimed at replacing the proprietary BIOS found in most computers.

|

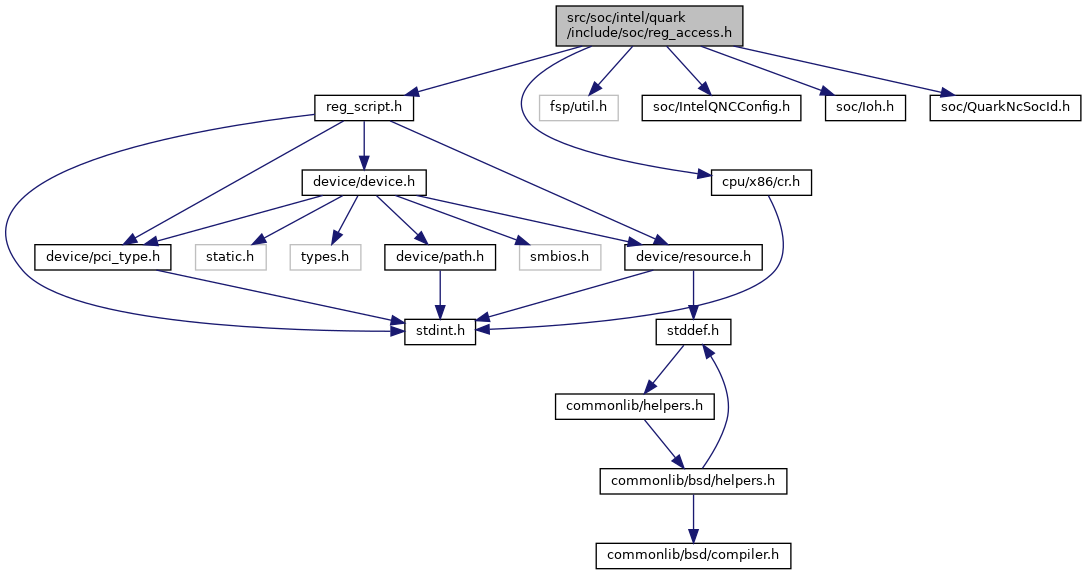

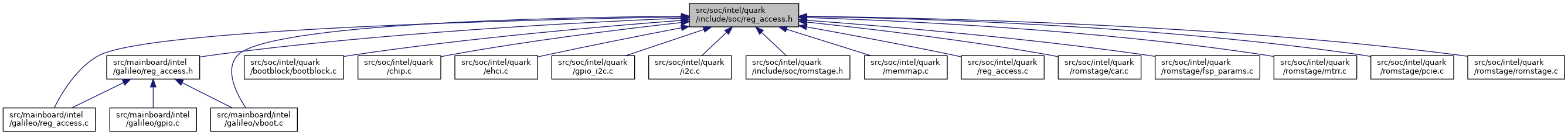

#include <cpu/x86/cr.h>#include <fsp/util.h>#include <reg_script.h>#include <soc/IntelQNCConfig.h>#include <soc/Ioh.h>#include <soc/QuarkNcSocId.h>

Go to the source code of this file.

Macros | |

| #define | SOC_ACCESS(cmd_, reg_, size_, mask_, value_, timeout_, reg_set_) |

| #define | REG_CPU_CR_ACCESS(cmd_, reg_, mask_, value_, timeout_) |

| #define | REG_CPU_CR_READ(reg_) REG_CPU_CR_ACCESS(READ, reg_, 0, 0, 0) |

| #define | REG_CPU_CR_WRITE(reg_, value_) REG_CPU_CR_ACCESS(WRITE, reg_, 0, value_, 0) |

| #define | REG_CPU_CR_AND(reg_, value_) REG_CPU_CR_RMW(reg_, value_, 0) |

| #define | REG_CPU_CR_RMW(reg_, mask_, value_) REG_CPU_CR_ACCESS(RMW, reg_, mask_, value_, 0) |

| #define | REG_CPU_CR_RXW(reg_, mask_, value_) REG_CPU_CR_ACCESS(RXW, reg_, mask_, value_, 0) |

| #define | REG_CPU_CR_OR(reg_, value_) REG_CPU_CR_RMW(reg_, 0xffffffff, value_) |

| #define | REG_CPU_CR_POLL(reg_, mask_, value_, timeout_) REG_CPU_CR_ACCESS(POLL, reg_, mask_, value_, timeout_) |

| #define | REG_CPU_CR_XOR(reg_, value_) REG_CPU_CR_RXW(reg_, 0xffffffff, value_) |

| #define | REG_GPE0_ACCESS(cmd_, reg_, mask_, value_, timeout_) |

| #define | REG_GPE0_READ(reg_) REG_GPE0_ACCESS(READ, reg_, 0, 0, 0) |

| #define | REG_GPE0_WRITE(reg_, value_) REG_GPE0_ACCESS(WRITE, reg_, 0, value_, 0) |

| #define | REG_GPE0_AND(reg_, value_) REG_GPE0_RMW(reg_, value_, 0) |

| #define | REG_GPE0_RMW(reg_, mask_, value_) REG_GPE0_ACCESS(RMW, reg_, mask_, value_, 0) |

| #define | REG_GPE0_RXW(reg_, mask_, value_) REG_GPE0_ACCESS(RXW, reg_, mask_, value_, 0) |

| #define | REG_GPE0_OR(reg_, value_) REG_GPE0_RMW(reg_, 0xffffffff, value_) |

| #define | REG_GPE0_POLL(reg_, mask_, value_, timeout_) REG_GPE0_ACCESS(POLL, reg_, mask_, value_, timeout_) |

| #define | REG_GPE0_XOR(reg_, value_) REG_GPE0_RXW(reg_, 0xffffffff, value_) |

| #define | REG_GPIO_ACCESS(cmd_, reg_, mask_, value_, timeout_) |

| #define | REG_GPIO_READ(reg_) REG_GPIO_ACCESS(READ, reg_, 0, 0, 0) |

| #define | REG_GPIO_WRITE(reg_, value_) REG_GPIO_ACCESS(WRITE, reg_, 0, value_, 0) |

| #define | REG_GPIO_AND(reg_, value_) REG_GPIO_RMW(reg_, value_, 0) |

| #define | REG_GPIO_RMW(reg_, mask_, value_) REG_GPIO_ACCESS(RMW, reg_, mask_, value_, 0) |

| #define | REG_GPIO_RXW(reg_, mask_, value_) REG_GPIO_ACCESS(RXW, reg_, mask_, value_, 0) |

| #define | REG_GPIO_OR(reg_, value_) REG_GPIO_RMW(reg_, 0xffffffff, value_) |

| #define | REG_GPIO_POLL(reg_, mask_, value_, timeout_) REG_GPIO_ACCESS(POLL, reg_, mask_, value_, timeout_) |

| #define | REG_GPIO_XOR(reg_, value_) REG_GPIO_RXW(reg_, 0xffffffff, value_) |

| #define | REG_HOST_BRIDGE_ACCESS(cmd_, reg_, mask_, value_, timeout_) |

| #define | REG_HOST_BRIDGE_READ(reg_) REG_HOST_BRIDGE_ACCESS(READ, reg_, 0, 0, 0) |

| #define | REG_HOST_BRIDGE_WRITE(reg_, value_) REG_HOST_BRIDGE_ACCESS(WRITE, reg_, 0, value_, 0) |

| #define | REG_HOST_BRIDGE_AND(reg_, value_) REG_HOST_BRIDGE_RMW(reg_, value_, 0) |

| #define | REG_HOST_BRIDGE_RMW(reg_, mask_, value_) REG_HOST_BRIDGE_ACCESS(RMW, reg_, mask_, value_, 0) |

| #define | REG_HOST_BRIDGE_RXW(reg_, mask_, value_) REG_HOST_BRIDGE_ACCESS(RXW, reg_, mask_, value_, 0) |

| #define | REG_HOST_BRIDGE_OR(reg_, value_) REG_HOST_BRIDGE_RMW(reg_, 0xffffffff, value_) |

| #define | REG_HOST_BRIDGE_POLL(reg_, mask_, value_, timeout_) REG_HOST_BRIDGE_ACCESS(POLL, reg_, mask_, value_, timeout_) |

| #define | REG_HOST_BRIDGE_XOR(reg_, value_) REG_HOST_BRIDGE_RXW(reg_, 0xffffffff, value_) |

| #define | REG_LEG_GPIO_ACCESS(cmd_, reg_, mask_, value_, timeout_) |

| #define | REG_LEG_GPIO_READ(reg_) REG_LEG_GPIO_ACCESS(READ, reg_, 0, 0, 0) |

| #define | REG_LEG_GPIO_WRITE(reg_, value_) REG_LEG_GPIO_ACCESS(WRITE, reg_, 0, value_, 0) |

| #define | REG_LEG_GPIO_AND(reg_, value_) REG_LEG_GPIO_RMW(reg_, value_, 0) |

| #define | REG_LEG_GPIO_RMW(reg_, mask_, value_) REG_LEG_GPIO_ACCESS(RMW, reg_, mask_, value_, 0) |

| #define | REG_LEG_GPIO_RXW(reg_, mask_, value_) REG_LEG_GPIO_ACCESS(RXW, reg_, mask_, value_, 0) |

| #define | REG_LEG_GPIO_OR(reg_, value_) REG_LEG_GPIO_RMW(reg_, 0xffffffff, value_) |

| #define | REG_LEG_GPIO_POLL(reg_, mask_, value_, timeout_) REG_LEG_GPIO_ACCESS(POLL, reg_, mask_, value_, timeout_) |

| #define | REG_LEG_GPIO_XOR(reg_, value_) REG_LEG_GPIO_RXW(reg_, 0xffffffff, value_) |

| #define | REG_PCIE_AFE_ACCESS(cmd_, reg_, mask_, value_, timeout_) |

| #define | REG_PCIE_AFE_READ(reg_) REG_PCIE_AFE_ACCESS(READ, reg_, 0, 0, 0) |

| #define | REG_PCIE_AFE_WRITE(reg_, value_) REG_PCIE_AFE_ACCESS(WRITE, reg_, 0, value_, 0) |

| #define | REG_PCIE_AFE_AND(reg_, value_) REG_PCIE_AFE_RMW(reg_, value_, 0) |

| #define | REG_PCIE_AFE_RMW(reg_, mask_, value_) REG_PCIE_AFE_ACCESS(RMW, reg_, mask_, value_, 0) |

| #define | REG_PCIE_AFE_RXW(reg_, mask_, value_) REG_PCIE_AFE_ACCESS(RXW, reg_, mask_, value_, 0) |

| #define | REG_PCIE_AFE_OR(reg_, value_) REG_PCIE_AFE_RMW(reg_, 0xffffffff, value_) |

| #define | REG_PCIE_AFE_POLL(reg_, mask_, value_, timeout_) REG_PCIE_AFE_ACCESS(POLL, reg_, mask_, value_, timeout_) |

| #define | REG_PCIE_AFE_XOR(reg_, value_) REG_PCIE_AFE_RXW(reg_, 0xffffffff, value_) |

| #define | MAINBOARD_PCIE_RESET(pin_value_) SOC_ACCESS(WRITE, 0, REG_SCRIPT_SIZE_32, 1, pin_value_, 0, PCIE_RESET) |

| #define | REG_RMU_TEMP_ACCESS(cmd_, reg_, mask_, value_, timeout_) |

| #define | REG_RMU_TEMP_READ(reg_) REG_RMU_TEMP_ACCESS(READ, reg_, 0, 0, 0) |

| #define | REG_RMU_TEMP_WRITE(reg_, value_) REG_RMU_TEMP_ACCESS(WRITE, reg_, 0, value_, 0) |

| #define | REG_RMU_TEMP_AND(reg_, value_) REG_RMU_TEMP_RMW(reg_, value_, 0) |

| #define | REG_RMU_TEMP_RMW(reg_, mask_, value_) REG_RMU_TEMP_ACCESS(RMW, reg_, mask_, value_, 0) |

| #define | REG_RMU_TEMP_RXW(reg_, mask_, value_) REG_RMU_TEMP_ACCESS(RXW, reg_, mask_, value_, 0) |

| #define | REG_RMU_TEMP_OR(reg_, value_) REG_RMU_TEMP_RMW(reg_, 0xffffffff, value_) |

| #define | REG_RMU_TEMP_POLL(reg_, mask_, value_, timeout_) REG_RMU_TEMP_ACCESS(POLL, reg_, mask_, value_, timeout_) |

| #define | REG_RMU_TEMP_XOR(reg_, value_) REG_RMU_TEMP_RXW(reg_, 0xffffffff, value_) |

| #define | REG_SOC_UNIT_ACCESS(cmd_, reg_, mask_, value_, timeout_) |

| #define | REG_SOC_UNIT_READ(reg_) REG_SOC_UNIT_ACCESS(READ, reg_, 0, 0, 0) |

| #define | REG_SOC_UNIT_WRITE(reg_, value_) REG_SOC_UNIT_ACCESS(WRITE, reg_, 0, value_, 0) |

| #define | REG_SOC_UNIT_AND(reg_, value_) REG_SOC_UNIT_RMW(reg_, value_, 0) |

| #define | REG_SOC_UNIT_RMW(reg_, mask_, value_) REG_SOC_UNIT_ACCESS(RMW, reg_, mask_, value_, 0) |

| #define | REG_SOC_UNIT_RXW(reg_, mask_, value_) REG_SOC_UNIT_ACCESS(RXW, reg_, mask_, value_, 0) |

| #define | REG_SOC_UNIT_OR(reg_, value_) REG_SOC_UNIT_RMW(reg_, 0xffffffff, value_) |

| #define | REG_SOC_UNIT_POLL(reg_, mask_, value_, timeout_) REG_SOC_UNIT_ACCESS(POLL, reg_, mask_, value_, timeout_) |

| #define | REG_SOC_UNIT_XOR(reg_, value_) REG_SOC_UNIT_RXW(reg_, 0xffffffff, value_) |

| #define | TIME_DELAY_USEC(value_) |

| #define | REG_USB_ACCESS(cmd_, reg_, mask_, value_, timeout_) |

| #define | REG_USB_READ(reg_) REG_USB_ACCESS(READ, reg_, 0, 0, 0) |

| #define | REG_USB_WRITE(reg_, value_) REG_USB_ACCESS(WRITE, reg_, 0, value_, 0) |

| #define | REG_USB_AND(reg_, value_) REG_USB_RMW(reg_, value_, 0) |

| #define | REG_USB_RMW(reg_, mask_, value_) REG_USB_ACCESS(RMW, reg_, mask_, value_, 0) |

| #define | REG_USB_RXW(reg_, mask_, value_) REG_USB_ACCESS(RXW, reg_, mask_, value_, 0) |

| #define | REG_USB_OR(reg_, value_) REG_USB_RMW(reg_, 0xffffffff, value_) |

| #define | REG_USB_POLL(reg_, mask_, value_, timeout_) REG_USB_ACCESS(POLL, reg_, mask_, value_, timeout_) |

| #define | REG_USB_XOR(reg_, value_) REG_USB_RXW(reg_, 0xffffffff, value_) |

Enumerations | |

| enum | { USB_PHY_REGS = 1 , SOC_UNIT_REGS , RMU_TEMP_REGS , MICROSECOND_DELAY , LEG_GPIO_REGS , GPIO_REGS , PCIE_AFE_REGS , PCIE_RESET , GPE0_REGS , HOST_BRIDGE , CPU_CR } |

| enum | { SOC_TYPE = REG_SCRIPT_TYPE_SOC_BASE } |

Functions | |

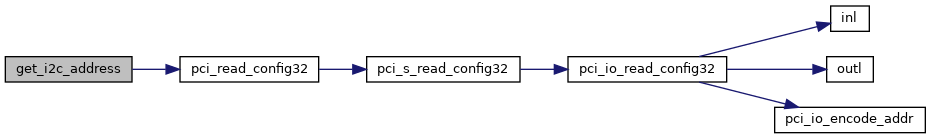

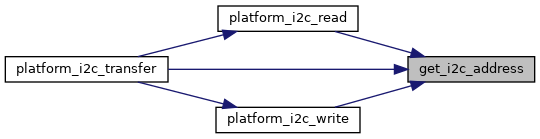

| void * | get_i2c_address (void) |

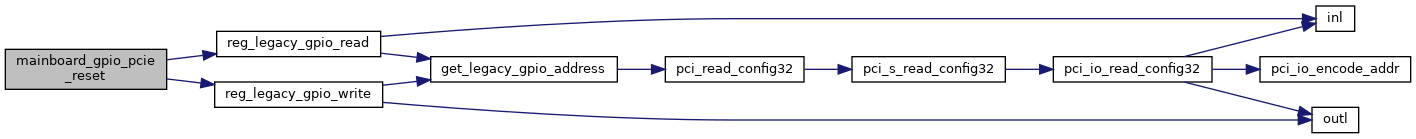

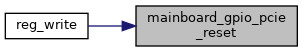

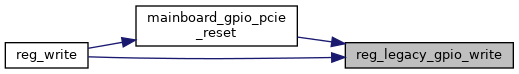

| void | mainboard_gpio_pcie_reset (uint32_t pin_value) |

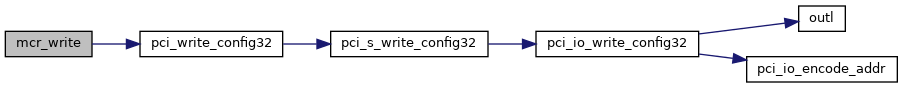

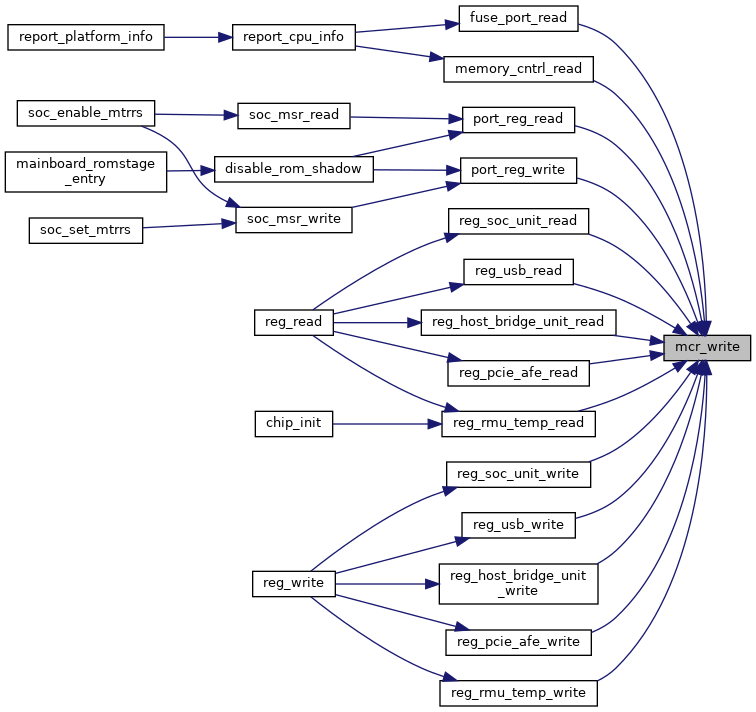

| void | mcr_write (uint8_t opcode, uint8_t port, uint32_t reg_address) |

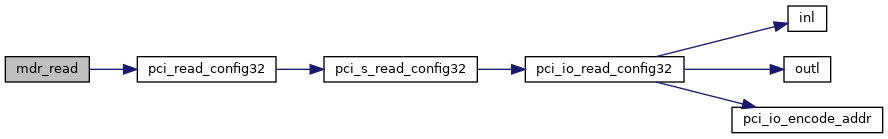

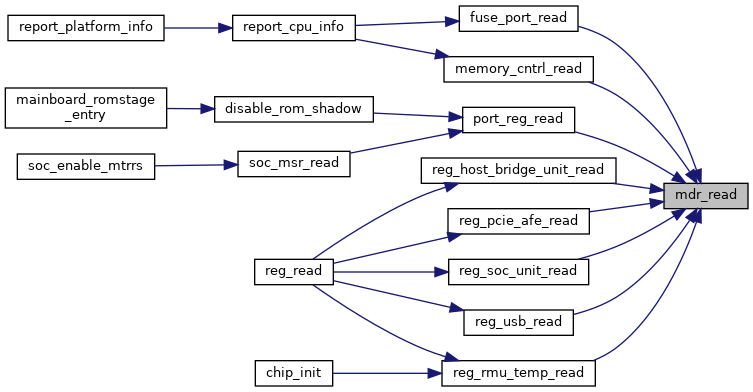

| uint32_t | mdr_read (void) |

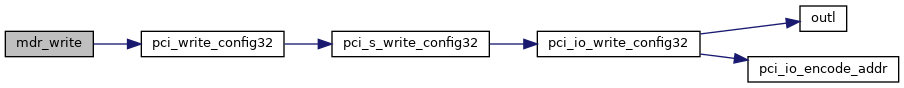

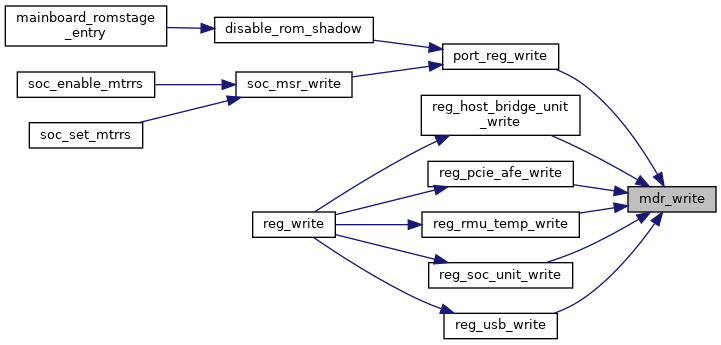

| void | mdr_write (uint32_t value) |

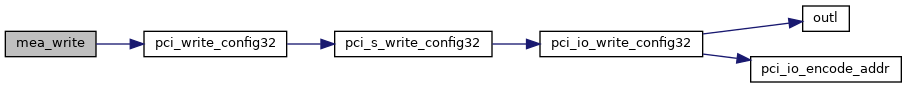

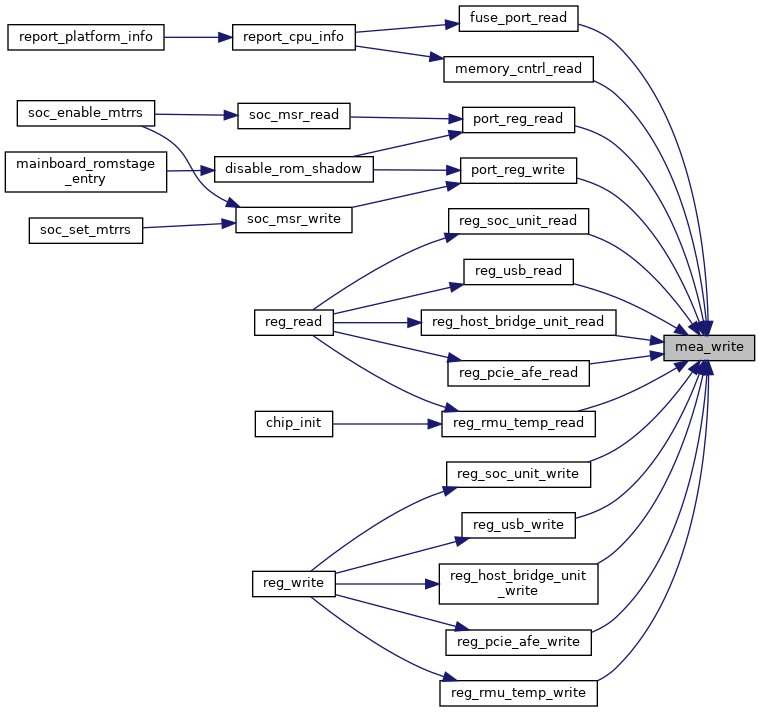

| void | mea_write (uint32_t reg_address) |

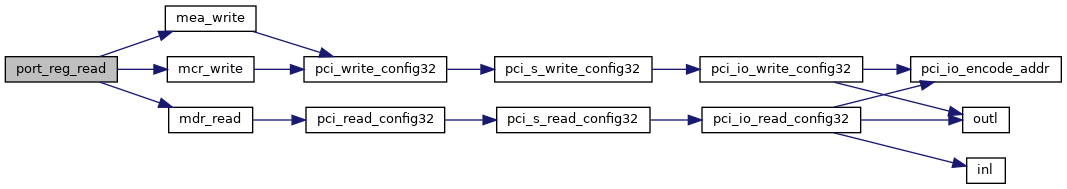

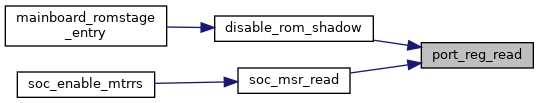

| uint32_t | port_reg_read (uint8_t port, uint32_t offset) |

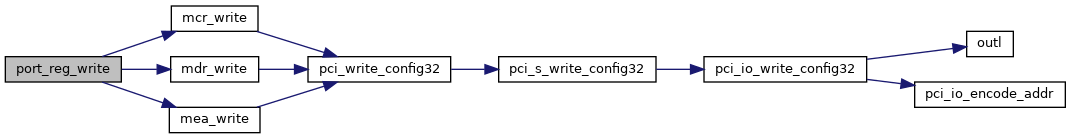

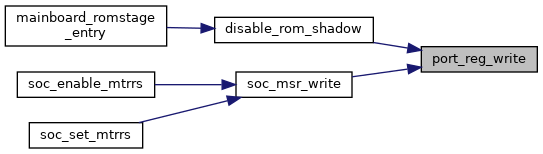

| void | port_reg_write (uint8_t port, uint32_t offset, uint32_t value) |

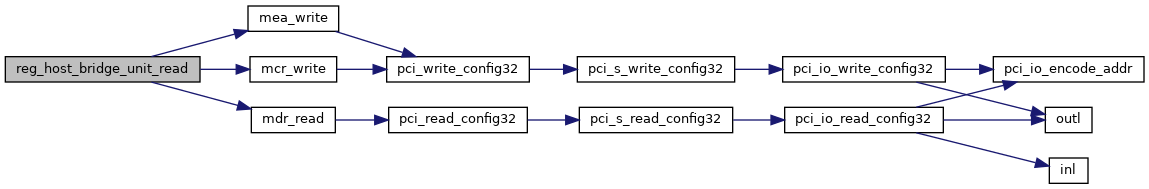

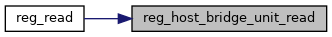

| uint32_t | reg_host_bridge_unit_read (uint32_t reg_address) |

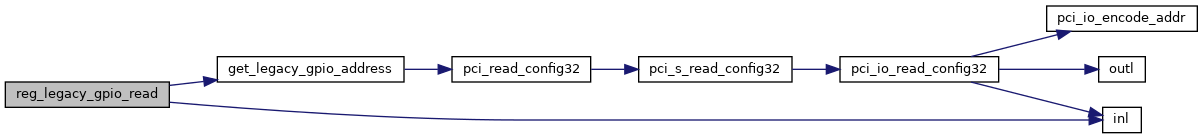

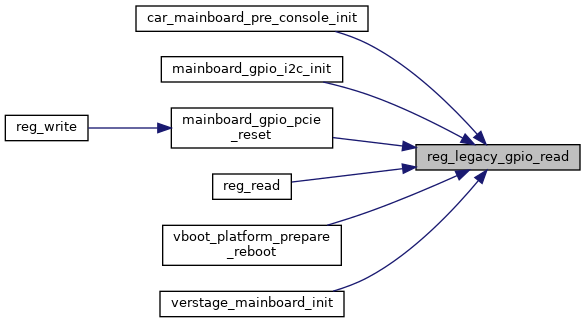

| uint32_t | reg_legacy_gpio_read (uint32_t reg_address) |

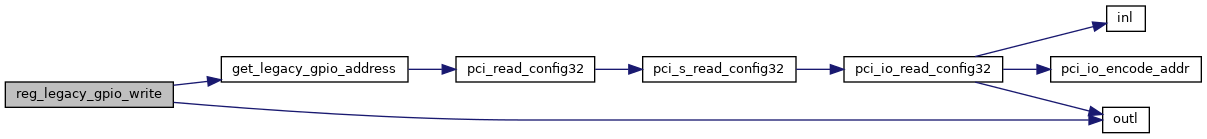

| void | reg_legacy_gpio_write (uint32_t reg_address, uint32_t value) |

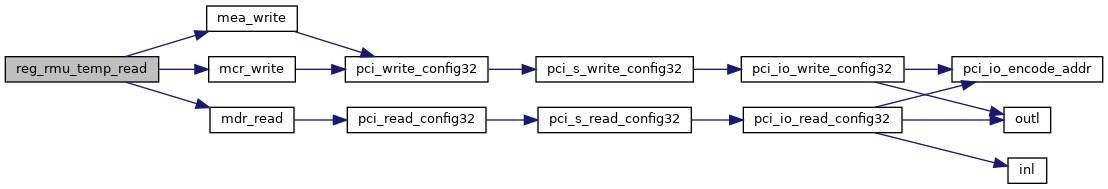

| uint32_t | reg_rmu_temp_read (uint32_t reg_address) |

| #define MAINBOARD_PCIE_RESET | ( | pin_value_ | ) | SOC_ACCESS(WRITE, 0, REG_SCRIPT_SIZE_32, 1, pin_value_, 0, PCIE_RESET) |

Definition at line 163 of file reg_access.h.

| #define REG_CPU_CR_ACCESS | ( | cmd_, | |

| reg_, | |||

| mask_, | |||

| value_, | |||

| timeout_ | |||

| ) |

Definition at line 37 of file reg_access.h.

| #define REG_CPU_CR_AND | ( | reg_, | |

| value_ | |||

| ) | REG_CPU_CR_RMW(reg_, value_, 0) |

Definition at line 44 of file reg_access.h.

| #define REG_CPU_CR_OR | ( | reg_, | |

| value_ | |||

| ) | REG_CPU_CR_RMW(reg_, 0xffffffff, value_) |

Definition at line 50 of file reg_access.h.

| #define REG_CPU_CR_POLL | ( | reg_, | |

| mask_, | |||

| value_, | |||

| timeout_ | |||

| ) | REG_CPU_CR_ACCESS(POLL, reg_, mask_, value_, timeout_) |

Definition at line 52 of file reg_access.h.

| #define REG_CPU_CR_READ | ( | reg_ | ) | REG_CPU_CR_ACCESS(READ, reg_, 0, 0, 0) |

Definition at line 40 of file reg_access.h.

| #define REG_CPU_CR_RMW | ( | reg_, | |

| mask_, | |||

| value_ | |||

| ) | REG_CPU_CR_ACCESS(RMW, reg_, mask_, value_, 0) |

Definition at line 46 of file reg_access.h.

| #define REG_CPU_CR_RXW | ( | reg_, | |

| mask_, | |||

| value_ | |||

| ) | REG_CPU_CR_ACCESS(RXW, reg_, mask_, value_, 0) |

Definition at line 48 of file reg_access.h.

| #define REG_CPU_CR_WRITE | ( | reg_, | |

| value_ | |||

| ) | REG_CPU_CR_ACCESS(WRITE, reg_, 0, value_, 0) |

Definition at line 42 of file reg_access.h.

| #define REG_CPU_CR_XOR | ( | reg_, | |

| value_ | |||

| ) | REG_CPU_CR_RXW(reg_, 0xffffffff, value_) |

Definition at line 54 of file reg_access.h.

| #define REG_GPE0_ACCESS | ( | cmd_, | |

| reg_, | |||

| mask_, | |||

| value_, | |||

| timeout_ | |||

| ) |

Definition at line 58 of file reg_access.h.

| #define REG_GPE0_AND | ( | reg_, | |

| value_ | |||

| ) | REG_GPE0_RMW(reg_, value_, 0) |

Definition at line 65 of file reg_access.h.

| #define REG_GPE0_OR | ( | reg_, | |

| value_ | |||

| ) | REG_GPE0_RMW(reg_, 0xffffffff, value_) |

Definition at line 71 of file reg_access.h.

| #define REG_GPE0_POLL | ( | reg_, | |

| mask_, | |||

| value_, | |||

| timeout_ | |||

| ) | REG_GPE0_ACCESS(POLL, reg_, mask_, value_, timeout_) |

Definition at line 73 of file reg_access.h.

| #define REG_GPE0_READ | ( | reg_ | ) | REG_GPE0_ACCESS(READ, reg_, 0, 0, 0) |

Definition at line 61 of file reg_access.h.

| #define REG_GPE0_RMW | ( | reg_, | |

| mask_, | |||

| value_ | |||

| ) | REG_GPE0_ACCESS(RMW, reg_, mask_, value_, 0) |

Definition at line 67 of file reg_access.h.

| #define REG_GPE0_RXW | ( | reg_, | |

| mask_, | |||

| value_ | |||

| ) | REG_GPE0_ACCESS(RXW, reg_, mask_, value_, 0) |

Definition at line 69 of file reg_access.h.

| #define REG_GPE0_WRITE | ( | reg_, | |

| value_ | |||

| ) | REG_GPE0_ACCESS(WRITE, reg_, 0, value_, 0) |

Definition at line 63 of file reg_access.h.

| #define REG_GPE0_XOR | ( | reg_, | |

| value_ | |||

| ) | REG_GPE0_RXW(reg_, 0xffffffff, value_) |

Definition at line 75 of file reg_access.h.

| #define REG_GPIO_ACCESS | ( | cmd_, | |

| reg_, | |||

| mask_, | |||

| value_, | |||

| timeout_ | |||

| ) |

Definition at line 79 of file reg_access.h.

| #define REG_GPIO_AND | ( | reg_, | |

| value_ | |||

| ) | REG_GPIO_RMW(reg_, value_, 0) |

Definition at line 86 of file reg_access.h.

| #define REG_GPIO_OR | ( | reg_, | |

| value_ | |||

| ) | REG_GPIO_RMW(reg_, 0xffffffff, value_) |

Definition at line 92 of file reg_access.h.

| #define REG_GPIO_POLL | ( | reg_, | |

| mask_, | |||

| value_, | |||

| timeout_ | |||

| ) | REG_GPIO_ACCESS(POLL, reg_, mask_, value_, timeout_) |

Definition at line 94 of file reg_access.h.

| #define REG_GPIO_READ | ( | reg_ | ) | REG_GPIO_ACCESS(READ, reg_, 0, 0, 0) |

Definition at line 82 of file reg_access.h.

| #define REG_GPIO_RMW | ( | reg_, | |

| mask_, | |||

| value_ | |||

| ) | REG_GPIO_ACCESS(RMW, reg_, mask_, value_, 0) |

Definition at line 88 of file reg_access.h.

| #define REG_GPIO_RXW | ( | reg_, | |

| mask_, | |||

| value_ | |||

| ) | REG_GPIO_ACCESS(RXW, reg_, mask_, value_, 0) |

Definition at line 90 of file reg_access.h.

| #define REG_GPIO_WRITE | ( | reg_, | |

| value_ | |||

| ) | REG_GPIO_ACCESS(WRITE, reg_, 0, value_, 0) |

Definition at line 84 of file reg_access.h.

| #define REG_GPIO_XOR | ( | reg_, | |

| value_ | |||

| ) | REG_GPIO_RXW(reg_, 0xffffffff, value_) |

Definition at line 96 of file reg_access.h.

| #define REG_HOST_BRIDGE_ACCESS | ( | cmd_, | |

| reg_, | |||

| mask_, | |||

| value_, | |||

| timeout_ | |||

| ) |

Definition at line 100 of file reg_access.h.

| #define REG_HOST_BRIDGE_AND | ( | reg_, | |

| value_ | |||

| ) | REG_HOST_BRIDGE_RMW(reg_, value_, 0) |

Definition at line 107 of file reg_access.h.

| #define REG_HOST_BRIDGE_OR | ( | reg_, | |

| value_ | |||

| ) | REG_HOST_BRIDGE_RMW(reg_, 0xffffffff, value_) |

Definition at line 113 of file reg_access.h.

| #define REG_HOST_BRIDGE_POLL | ( | reg_, | |

| mask_, | |||

| value_, | |||

| timeout_ | |||

| ) | REG_HOST_BRIDGE_ACCESS(POLL, reg_, mask_, value_, timeout_) |

Definition at line 115 of file reg_access.h.

| #define REG_HOST_BRIDGE_READ | ( | reg_ | ) | REG_HOST_BRIDGE_ACCESS(READ, reg_, 0, 0, 0) |

Definition at line 103 of file reg_access.h.

| #define REG_HOST_BRIDGE_RMW | ( | reg_, | |

| mask_, | |||

| value_ | |||

| ) | REG_HOST_BRIDGE_ACCESS(RMW, reg_, mask_, value_, 0) |

Definition at line 109 of file reg_access.h.

| #define REG_HOST_BRIDGE_RXW | ( | reg_, | |

| mask_, | |||

| value_ | |||

| ) | REG_HOST_BRIDGE_ACCESS(RXW, reg_, mask_, value_, 0) |

Definition at line 111 of file reg_access.h.

| #define REG_HOST_BRIDGE_WRITE | ( | reg_, | |

| value_ | |||

| ) | REG_HOST_BRIDGE_ACCESS(WRITE, reg_, 0, value_, 0) |

Definition at line 105 of file reg_access.h.

| #define REG_HOST_BRIDGE_XOR | ( | reg_, | |

| value_ | |||

| ) | REG_HOST_BRIDGE_RXW(reg_, 0xffffffff, value_) |

Definition at line 117 of file reg_access.h.

| #define REG_LEG_GPIO_ACCESS | ( | cmd_, | |

| reg_, | |||

| mask_, | |||

| value_, | |||

| timeout_ | |||

| ) |

Definition at line 121 of file reg_access.h.

| #define REG_LEG_GPIO_AND | ( | reg_, | |

| value_ | |||

| ) | REG_LEG_GPIO_RMW(reg_, value_, 0) |

Definition at line 128 of file reg_access.h.

| #define REG_LEG_GPIO_OR | ( | reg_, | |

| value_ | |||

| ) | REG_LEG_GPIO_RMW(reg_, 0xffffffff, value_) |

Definition at line 134 of file reg_access.h.

| #define REG_LEG_GPIO_POLL | ( | reg_, | |

| mask_, | |||

| value_, | |||

| timeout_ | |||

| ) | REG_LEG_GPIO_ACCESS(POLL, reg_, mask_, value_, timeout_) |

Definition at line 136 of file reg_access.h.

| #define REG_LEG_GPIO_READ | ( | reg_ | ) | REG_LEG_GPIO_ACCESS(READ, reg_, 0, 0, 0) |

Definition at line 124 of file reg_access.h.

| #define REG_LEG_GPIO_RMW | ( | reg_, | |

| mask_, | |||

| value_ | |||

| ) | REG_LEG_GPIO_ACCESS(RMW, reg_, mask_, value_, 0) |

Definition at line 130 of file reg_access.h.

| #define REG_LEG_GPIO_RXW | ( | reg_, | |

| mask_, | |||

| value_ | |||

| ) | REG_LEG_GPIO_ACCESS(RXW, reg_, mask_, value_, 0) |

Definition at line 132 of file reg_access.h.

| #define REG_LEG_GPIO_WRITE | ( | reg_, | |

| value_ | |||

| ) | REG_LEG_GPIO_ACCESS(WRITE, reg_, 0, value_, 0) |

Definition at line 126 of file reg_access.h.

| #define REG_LEG_GPIO_XOR | ( | reg_, | |

| value_ | |||

| ) | REG_LEG_GPIO_RXW(reg_, 0xffffffff, value_) |

Definition at line 138 of file reg_access.h.

| #define REG_PCIE_AFE_ACCESS | ( | cmd_, | |

| reg_, | |||

| mask_, | |||

| value_, | |||

| timeout_ | |||

| ) |

Definition at line 142 of file reg_access.h.

| #define REG_PCIE_AFE_AND | ( | reg_, | |

| value_ | |||

| ) | REG_PCIE_AFE_RMW(reg_, value_, 0) |

Definition at line 149 of file reg_access.h.

| #define REG_PCIE_AFE_OR | ( | reg_, | |

| value_ | |||

| ) | REG_PCIE_AFE_RMW(reg_, 0xffffffff, value_) |

Definition at line 155 of file reg_access.h.

| #define REG_PCIE_AFE_POLL | ( | reg_, | |

| mask_, | |||

| value_, | |||

| timeout_ | |||

| ) | REG_PCIE_AFE_ACCESS(POLL, reg_, mask_, value_, timeout_) |

Definition at line 157 of file reg_access.h.

| #define REG_PCIE_AFE_READ | ( | reg_ | ) | REG_PCIE_AFE_ACCESS(READ, reg_, 0, 0, 0) |

Definition at line 145 of file reg_access.h.

| #define REG_PCIE_AFE_RMW | ( | reg_, | |

| mask_, | |||

| value_ | |||

| ) | REG_PCIE_AFE_ACCESS(RMW, reg_, mask_, value_, 0) |

Definition at line 151 of file reg_access.h.

| #define REG_PCIE_AFE_RXW | ( | reg_, | |

| mask_, | |||

| value_ | |||

| ) | REG_PCIE_AFE_ACCESS(RXW, reg_, mask_, value_, 0) |

Definition at line 153 of file reg_access.h.

| #define REG_PCIE_AFE_WRITE | ( | reg_, | |

| value_ | |||

| ) | REG_PCIE_AFE_ACCESS(WRITE, reg_, 0, value_, 0) |

Definition at line 147 of file reg_access.h.

| #define REG_PCIE_AFE_XOR | ( | reg_, | |

| value_ | |||

| ) | REG_PCIE_AFE_RXW(reg_, 0xffffffff, value_) |

Definition at line 159 of file reg_access.h.

| #define REG_RMU_TEMP_ACCESS | ( | cmd_, | |

| reg_, | |||

| mask_, | |||

| value_, | |||

| timeout_ | |||

| ) |

Definition at line 167 of file reg_access.h.

| #define REG_RMU_TEMP_AND | ( | reg_, | |

| value_ | |||

| ) | REG_RMU_TEMP_RMW(reg_, value_, 0) |

Definition at line 174 of file reg_access.h.

| #define REG_RMU_TEMP_OR | ( | reg_, | |

| value_ | |||

| ) | REG_RMU_TEMP_RMW(reg_, 0xffffffff, value_) |

Definition at line 180 of file reg_access.h.

| #define REG_RMU_TEMP_POLL | ( | reg_, | |

| mask_, | |||

| value_, | |||

| timeout_ | |||

| ) | REG_RMU_TEMP_ACCESS(POLL, reg_, mask_, value_, timeout_) |

Definition at line 182 of file reg_access.h.

| #define REG_RMU_TEMP_READ | ( | reg_ | ) | REG_RMU_TEMP_ACCESS(READ, reg_, 0, 0, 0) |

Definition at line 170 of file reg_access.h.

| #define REG_RMU_TEMP_RMW | ( | reg_, | |

| mask_, | |||

| value_ | |||

| ) | REG_RMU_TEMP_ACCESS(RMW, reg_, mask_, value_, 0) |

Definition at line 176 of file reg_access.h.

| #define REG_RMU_TEMP_RXW | ( | reg_, | |

| mask_, | |||

| value_ | |||

| ) | REG_RMU_TEMP_ACCESS(RXW, reg_, mask_, value_, 0) |

Definition at line 178 of file reg_access.h.

| #define REG_RMU_TEMP_WRITE | ( | reg_, | |

| value_ | |||

| ) | REG_RMU_TEMP_ACCESS(WRITE, reg_, 0, value_, 0) |

Definition at line 172 of file reg_access.h.

| #define REG_RMU_TEMP_XOR | ( | reg_, | |

| value_ | |||

| ) | REG_RMU_TEMP_RXW(reg_, 0xffffffff, value_) |

Definition at line 184 of file reg_access.h.

| #define REG_SOC_UNIT_ACCESS | ( | cmd_, | |

| reg_, | |||

| mask_, | |||

| value_, | |||

| timeout_ | |||

| ) |

Definition at line 188 of file reg_access.h.

| #define REG_SOC_UNIT_AND | ( | reg_, | |

| value_ | |||

| ) | REG_SOC_UNIT_RMW(reg_, value_, 0) |

Definition at line 195 of file reg_access.h.

| #define REG_SOC_UNIT_OR | ( | reg_, | |

| value_ | |||

| ) | REG_SOC_UNIT_RMW(reg_, 0xffffffff, value_) |

Definition at line 201 of file reg_access.h.

| #define REG_SOC_UNIT_POLL | ( | reg_, | |

| mask_, | |||

| value_, | |||

| timeout_ | |||

| ) | REG_SOC_UNIT_ACCESS(POLL, reg_, mask_, value_, timeout_) |

Definition at line 203 of file reg_access.h.

| #define REG_SOC_UNIT_READ | ( | reg_ | ) | REG_SOC_UNIT_ACCESS(READ, reg_, 0, 0, 0) |

Definition at line 191 of file reg_access.h.

| #define REG_SOC_UNIT_RMW | ( | reg_, | |

| mask_, | |||

| value_ | |||

| ) | REG_SOC_UNIT_ACCESS(RMW, reg_, mask_, value_, 0) |

Definition at line 197 of file reg_access.h.

| #define REG_SOC_UNIT_RXW | ( | reg_, | |

| mask_, | |||

| value_ | |||

| ) | REG_SOC_UNIT_ACCESS(RXW, reg_, mask_, value_, 0) |

Definition at line 199 of file reg_access.h.

| #define REG_SOC_UNIT_WRITE | ( | reg_, | |

| value_ | |||

| ) | REG_SOC_UNIT_ACCESS(WRITE, reg_, 0, value_, 0) |

Definition at line 193 of file reg_access.h.

| #define REG_SOC_UNIT_XOR | ( | reg_, | |

| value_ | |||

| ) | REG_SOC_UNIT_RXW(reg_, 0xffffffff, value_) |

Definition at line 205 of file reg_access.h.

| #define REG_USB_ACCESS | ( | cmd_, | |

| reg_, | |||

| mask_, | |||

| value_, | |||

| timeout_ | |||

| ) |

Definition at line 214 of file reg_access.h.

| #define REG_USB_AND | ( | reg_, | |

| value_ | |||

| ) | REG_USB_RMW(reg_, value_, 0) |

Definition at line 221 of file reg_access.h.

| #define REG_USB_OR | ( | reg_, | |

| value_ | |||

| ) | REG_USB_RMW(reg_, 0xffffffff, value_) |

Definition at line 227 of file reg_access.h.

| #define REG_USB_POLL | ( | reg_, | |

| mask_, | |||

| value_, | |||

| timeout_ | |||

| ) | REG_USB_ACCESS(POLL, reg_, mask_, value_, timeout_) |

Definition at line 229 of file reg_access.h.

| #define REG_USB_READ | ( | reg_ | ) | REG_USB_ACCESS(READ, reg_, 0, 0, 0) |

Definition at line 217 of file reg_access.h.

| #define REG_USB_RMW | ( | reg_, | |

| mask_, | |||

| value_ | |||

| ) | REG_USB_ACCESS(RMW, reg_, mask_, value_, 0) |

Definition at line 223 of file reg_access.h.

| #define REG_USB_RXW | ( | reg_, | |

| mask_, | |||

| value_ | |||

| ) | REG_USB_ACCESS(RXW, reg_, mask_, value_, 0) |

Definition at line 225 of file reg_access.h.

| #define REG_USB_WRITE | ( | reg_, | |

| value_ | |||

| ) | REG_USB_ACCESS(WRITE, reg_, 0, value_, 0) |

Definition at line 219 of file reg_access.h.

| #define REG_USB_XOR | ( | reg_, | |

| value_ | |||

| ) | REG_USB_RXW(reg_, 0xffffffff, value_) |

Definition at line 231 of file reg_access.h.

| #define SOC_ACCESS | ( | cmd_, | |

| reg_, | |||

| size_, | |||

| mask_, | |||

| value_, | |||

| timeout_, | |||

| reg_set_ | |||

| ) |

Definition at line 32 of file reg_access.h.

| #define TIME_DELAY_USEC | ( | value_ | ) |

Definition at line 209 of file reg_access.h.

| anonymous enum |

| Enumerator | |

|---|---|

| USB_PHY_REGS | |

| SOC_UNIT_REGS | |

| RMU_TEMP_REGS | |

| MICROSECOND_DELAY | |

| LEG_GPIO_REGS | |

| GPIO_REGS | |

| PCIE_AFE_REGS | |

| PCIE_RESET | |

| GPE0_REGS | |

| HOST_BRIDGE | |

| CPU_CR | |

Definition at line 13 of file reg_access.h.

| anonymous enum |

| Enumerator | |

|---|---|

| SOC_TYPE | |

Definition at line 27 of file reg_access.h.

Definition at line 42 of file reg_access.c.

References ASSERT, I2CGPIO_BDF, PCI_BASE_ADDRESS_0, PCI_BASE_ADDRESS_MEM_ATTR_MASK, and pci_read_config32().

Referenced by platform_i2c_read(), platform_i2c_transfer(), and platform_i2c_write().

Definition at line 53 of file gpio.c.

References CONFIG, GEN1_PCI_RESET_RESUMEWELL_GPIO, GEN2_PCI_RESET_RESUMEWELL_GPIO, R_QNC_GPIO_RGLVL_RESUME_WELL, reg_legacy_gpio_read(), reg_legacy_gpio_write(), and value.

Referenced by reg_write().

Definition at line 95 of file reg_access.c.

References MC_BDF, pci_write_config32(), QNC_ACCESS_PORT_MCR, QNC_MCR_BYTE_ENABLES, QNC_MCR_MASK, QNC_MCR_OP_OFFSET, QNC_MCR_PORT_OFFSET, and QNC_MCR_REG_OFFSET.

Referenced by fuse_port_read(), memory_cntrl_read(), port_reg_read(), port_reg_write(), reg_host_bridge_unit_read(), reg_host_bridge_unit_write(), reg_pcie_afe_read(), reg_pcie_afe_write(), reg_rmu_temp_read(), reg_rmu_temp_write(), reg_soc_unit_read(), reg_soc_unit_write(), reg_usb_read(), and reg_usb_write().

Definition at line 104 of file reg_access.c.

References MC_BDF, pci_read_config32(), and QNC_ACCESS_PORT_MDR.

Referenced by fuse_port_read(), memory_cntrl_read(), port_reg_read(), reg_host_bridge_unit_read(), reg_pcie_afe_read(), reg_rmu_temp_read(), reg_soc_unit_read(), and reg_usb_read().

Definition at line 109 of file reg_access.c.

References MC_BDF, pci_write_config32(), QNC_ACCESS_PORT_MDR, and value.

Referenced by port_reg_write(), reg_host_bridge_unit_write(), reg_pcie_afe_write(), reg_rmu_temp_write(), reg_soc_unit_write(), and reg_usb_write().

Definition at line 114 of file reg_access.c.

References MC_BDF, pci_write_config32(), QNC_ACCESS_PORT_MEA, and QNC_MEA_MASK.

Referenced by fuse_port_read(), memory_cntrl_read(), port_reg_read(), port_reg_write(), reg_host_bridge_unit_read(), reg_host_bridge_unit_write(), reg_pcie_afe_read(), reg_pcie_afe_write(), reg_rmu_temp_read(), reg_rmu_temp_write(), reg_soc_unit_read(), reg_soc_unit_write(), reg_usb_read(), and reg_usb_write().

Definition at line 120 of file reg_access.c.

References mcr_write(), mdr_read(), mea_write(), offset, and QUARK_OPCODE_READ.

Referenced by disable_rom_shadow(), and soc_msr_read().

Definition at line 128 of file reg_access.c.

References mcr_write(), mdr_write(), mea_write(), offset, QUARK_OPCODE_WRITE, and value.

Referenced by disable_rom_shadow(), and soc_msr_write().

Definition at line 190 of file reg_access.c.

References mcr_write(), mdr_read(), mea_write(), QUARK_NC_HOST_BRIDGE_SB_PORT_ID, and QUARK_OPCODE_READ.

Referenced by reg_read().

Definition at line 208 of file reg_access.c.

References get_legacy_gpio_address(), and inl().

Referenced by car_mainboard_pre_console_init(), mainboard_gpio_i2c_init(), mainboard_gpio_pcie_reset(), reg_read(), vboot_platform_prepare_reboot(), and verstage_mainboard_init().

Definition at line 214 of file reg_access.c.

References get_legacy_gpio_address(), outl(), and value.

Referenced by mainboard_gpio_pcie_reset(), and reg_write().

Definition at line 238 of file reg_access.c.

References mcr_write(), mdr_read(), mea_write(), QUARK_NC_RMU_SB_PORT_ID, and QUARK_OPCODE_READ.

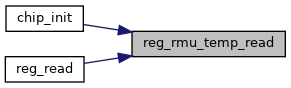

Referenced by chip_init(), and reg_read().