|

coreboot

coreboot is an Open Source project aimed at replacing the proprietary BIOS found in most computers.

|

|

coreboot

coreboot is an Open Source project aimed at replacing the proprietary BIOS found in most computers.

|

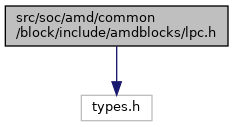

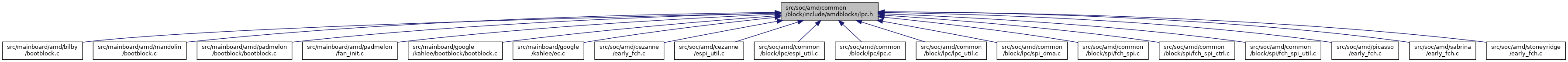

#include <types.h>

Go to the source code of this file.

Functions | |

| void | lpc_disable_decodes (void) |

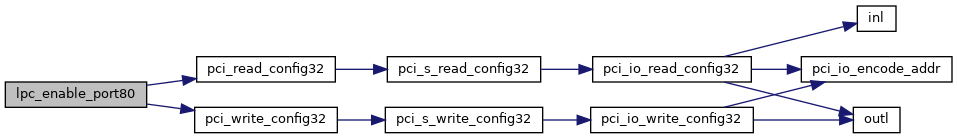

| void | lpc_enable_port80 (void) |

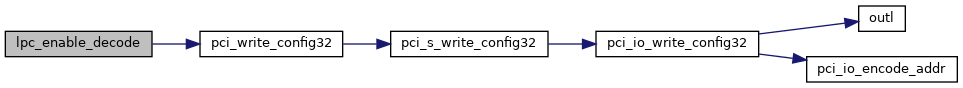

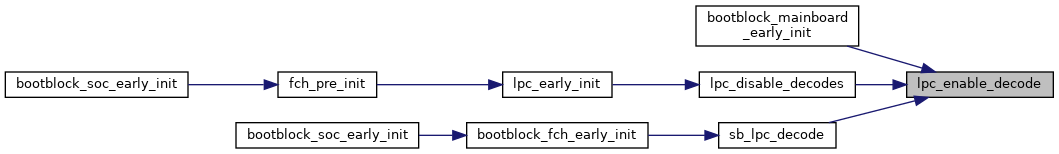

| void | lpc_enable_decode (uint32_t decodes) |

| void | lpc_enable_sio_decode (const bool addr) |

| uintptr_t | lpc_spibase (void) |

| void | lpc_tpm_decode (void) |

| void | lpc_tpm_decode_spi (void) |

| void | lpc_enable_rom (void) |

| void | lpc_enable_spi_prefetch (void) |

| void | lpc_disable_spi_rom_sharing (void) |

| uint16_t | lpc_wideio_size (int index) |

| Find the size of a particular wide IO. More... | |

| int | lpc_find_wideio_range (uint16_t start, uint16_t size) |

| Identify if any LPC wide IO is covering the IO range. More... | |

| int | lpc_set_wideio_range (uint16_t start, uint16_t size) |

| Program a LPC wide IO to support an IO range. More... | |

| uintptr_t | lpc_get_spibase (void) |

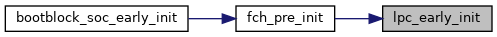

| void | lpc_early_init (void) |

| void | lpc_set_spibase (uint32_t base) |

| void | lpc_enable_spi_rom (uint32_t enable) |

| #define LPC_ROM_DMA_CTRL_DW_COUNT | ( | bytes | ) | (((bytes / LPC_ROM_DMA_MIN_ALIGNMENT) - 1) << LPC_ROM_DMA_CTRL_DW_COUNT_SHIFT) |

| #define LPC_ROM_DMA_CTRL_DW_COUNT_MASK (0x3ffUL << LPC_ROM_DMA_CTRL_DW_COUNT_SHIFT) |

| #define LPC_ROM_DMA_CTRL_MAX_BYTES |

| #define RANGE_ADDR_MASK 0x000000ff /* Range defined by bits 7-0 */ |

| #define ROM_PROTECT_RANGE_REG | ( | n | ) | (ROM_PROTECT_RANGE0 + (4 * n)) |

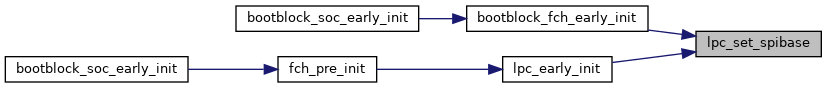

Definition at line 169 of file lpc_util.c.

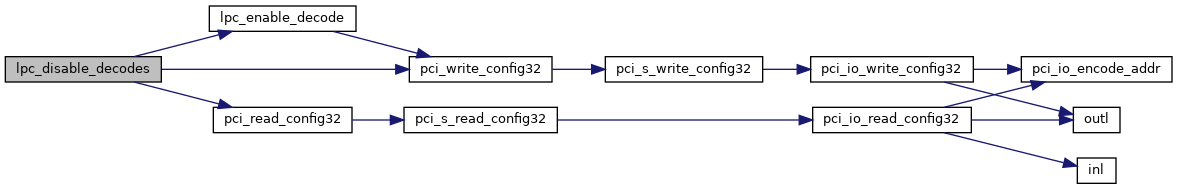

References _LPCB_DEV, lpc_enable_decode(), LPC_IO_OR_MEM_DECODE_ENABLE, LPC_IO_PORT_DECODE_ENABLE, LPC_MEM_PORT0, LPC_MEM_PORT1, LPC_SYNC_TIMEOUT_COUNT_ENABLE, LPC_SYNC_TIMEOUT_COUNT_MASK, LPC_WIDEIO2_GENERIC_PORT, pci_read_config32(), and pci_write_config32().

Referenced by lpc_early_init().

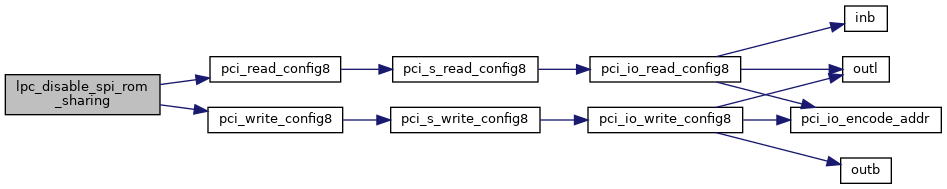

Definition at line 296 of file lpc_util.c.

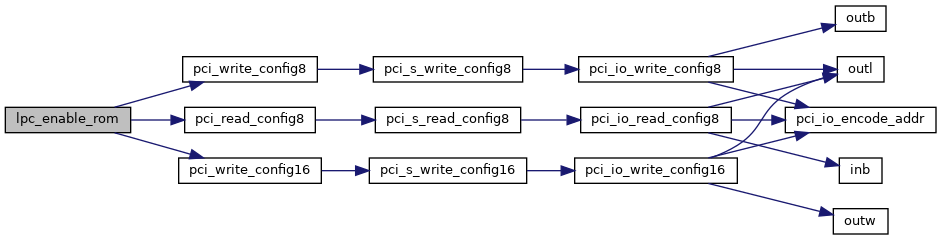

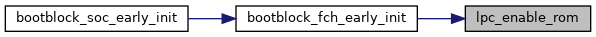

References _LPCB_DEV, CONFIG, dead_code, EXT_ROM_SHARING_EN, LPC_PCI_CONTROL, pci_read_config8(), pci_write_config8(), and VW_ROM_SHARING_EN.

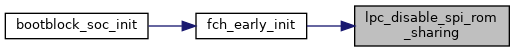

Referenced by fch_early_init().

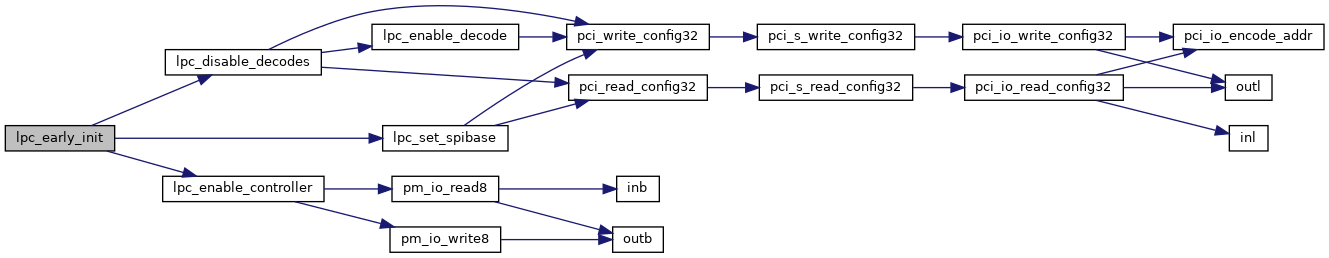

Definition at line 355 of file lpc_util.c.

References lpc_disable_decodes(), lpc_enable_controller(), lpc_set_spibase(), and SPI_BASE_ADDRESS.

Referenced by fch_pre_init().

Definition at line 160 of file lpc_util.c.

References _LPCB_DEV, LPC_IO_PORT_DECODE_ENABLE, and pci_write_config32().

Referenced by bootblock_mainboard_early_init(), lpc_disable_decodes(), and sb_lpc_decode().

Definition at line 139 of file lpc_util.c.

References _LPCB_DEV, DECODE_IO_PORT_ENABLE4, LPC_IO_OR_MEM_DECODE_ENABLE, pci_read_config32(), and pci_write_config32().

Referenced by bootblock_fch_early_init(), and lpc_configure_decodes().

Definition at line 250 of file lpc_util.c.

References _LPCB_DEV, LPC_IO_OR_MEM_DECODE_ENABLE, pci_read_config8(), pci_write_config16(), pci_write_config8(), ROM_ADDRESS_RANGE1_END, ROM_ADDRESS_RANGE1_START, ROM_ADDRESS_RANGE2_END, and ROM_ADDRESS_RANGE2_START.

Referenced by bootblock_fch_early_init().

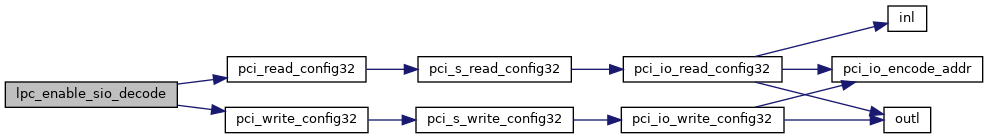

Definition at line 148 of file lpc_util.c.

References _LPCB_DEV, addr, DECODE_ALTERNATE_SIO_ENABLE, DECODE_SIO_ENABLE, LPC_IO_OR_MEM_DECODE_ENABLE, LPC_SELECT_SIO_2E2F, pci_read_config32(), and pci_write_config32().

Referenced by bootblock_mainboard_early_init().

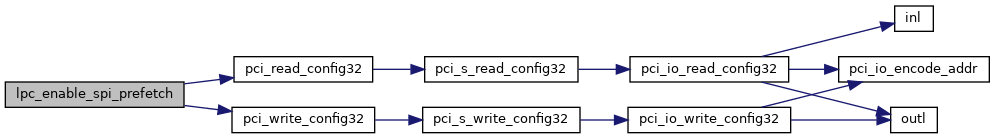

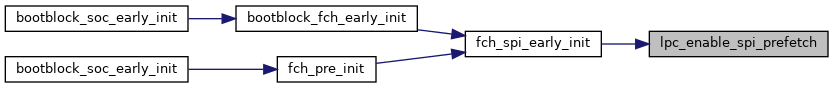

Definition at line 287 of file lpc_util.c.

References _LPCB_DEV, LPC_ROM_DMA_EC_HOST_CONTROL, pci_read_config32(), pci_write_config32(), SPI_FROM_HOST_PREFETCH_EN, and SPI_FROM_USB_PREFETCH_EN.

Referenced by fch_spi_early_init().

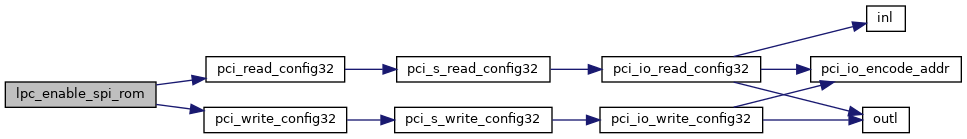

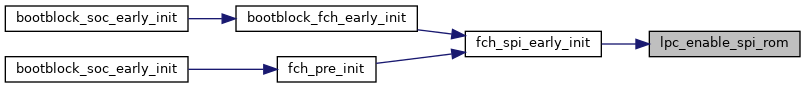

Definition at line 330 of file lpc_util.c.

References _LPCB_DEV, pci_read_config32(), pci_write_config32(), SPI_BASE_ADDRESS_REGISTER, SPI_ROM_ALT_ENABLE, and SPI_ROM_ENABLE.

Referenced by fch_spi_early_init().

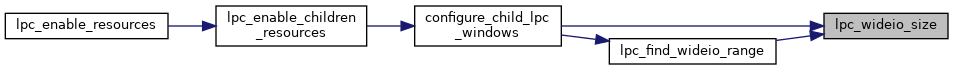

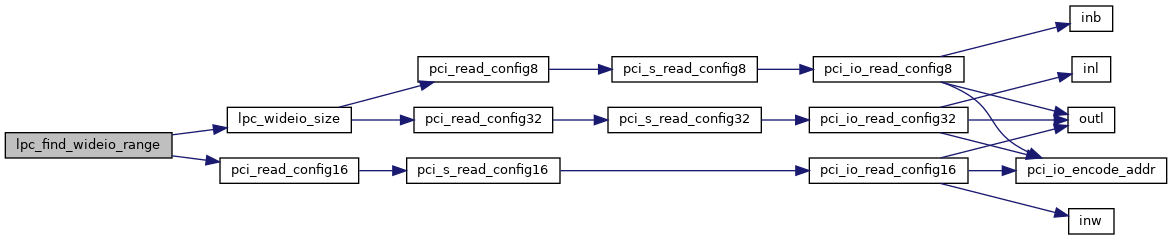

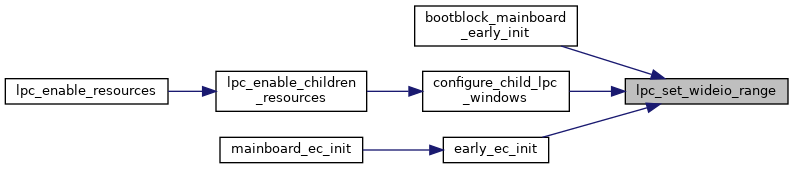

Identify if any LPC wide IO is covering the IO range.

| start | = start of IO range |

| size | = size of IO range |

Definition at line 80 of file lpc_util.c.

References _LPCB_DEV, ARRAY_SIZE, lpc_wideio_size(), pci_read_config16(), WIDEIO_RANGE_ERROR, and wio_io_en.

Referenced by configure_child_lpc_windows().

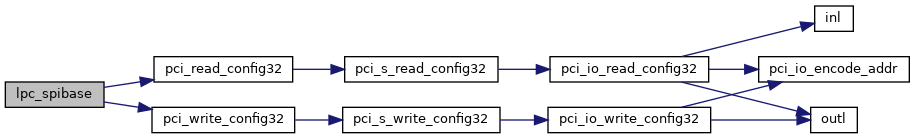

Definition at line 309 of file lpc_util.c.

References _LPCB_DEV, ALIGN_DOWN, base, pci_read_config32(), SPI_BASE_ADDRESS_REGISTER, and SPI_BASE_ALIGNMENT.

Referenced by espi_get_bar(), and spi_get_bar().

Definition at line 318 of file lpc_util.c.

References _LPCB_DEV, ALIGN_DOWN, base, pci_read_config32(), pci_write_config32(), SPI_BASE_ADDRESS_REGISTER, and SPI_BASE_ALIGNMENT.

Referenced by bootblock_fch_early_init(), and lpc_early_init().

Program a LPC wide IO to support an IO range.

| start | = start of range to be routed through wide IO |

| size | = size of range to be routed through wide IO |

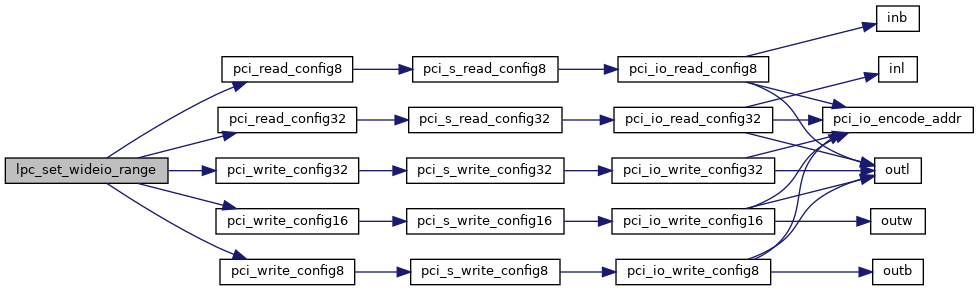

Definition at line 109 of file lpc_util.c.

References _LPCB_DEV, wide_io_ioport_and_bits::alt, ARRAY_SIZE, wide_io_ioport_and_bits::enable, LPC_ALT_WIDEIO_RANGE_ENABLE, LPC_IO_OR_MEM_DECODE_ENABLE, pci_read_config32(), pci_read_config8(), pci_write_config16(), pci_write_config32(), pci_write_config8(), WIDEIO_RANGE_ERROR, and wio_io_en.

Referenced by bootblock_mainboard_early_init(), configure_child_lpc_windows(), and early_ec_init().

Definition at line 185 of file lpc_util.c.

References _LPCB_DEV, base, pci_read_config32(), pci_write_config32(), SPI_BASE_ADDRESS, SPI_BASE_ADDRESS_REGISTER, SPI_BASE_RESERVED, SPI_PRESERVE_BITS, and SPI_ROM_ENABLE.

Definition at line 214 of file lpc_util.c.

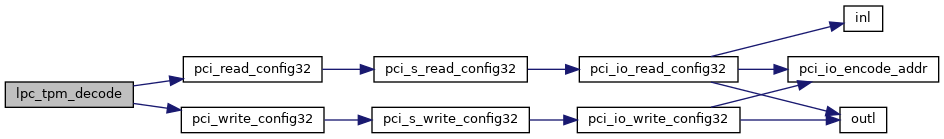

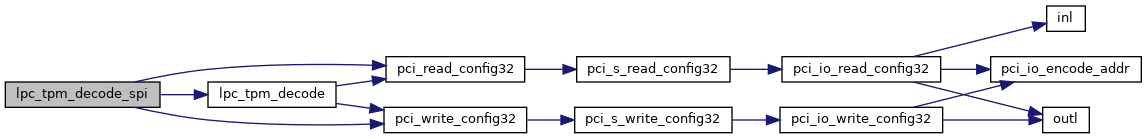

References _LPCB_DEV, LPC_TRUSTED_PLATFORM_MODULE, pci_read_config32(), pci_write_config32(), TPM_12_EN, TPM_LEGACY_EN, and value.

Referenced by lpc_tpm_decode_spi().

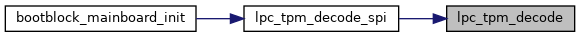

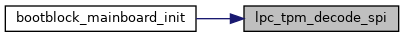

Definition at line 229 of file lpc_util.c.

References _LPCB_DEV, lpc_tpm_decode(), pci_read_config32(), pci_write_config32(), ROUTE_TPM_2_SPI, and SPI_BASE_ADDRESS_REGISTER.

Referenced by bootblock_mainboard_init().

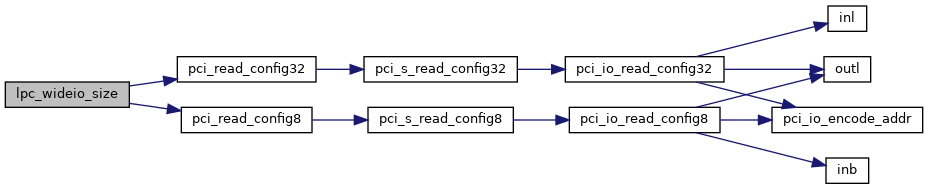

| uint16_t lpc_wideio_size | ( | int | index | ) |

Find the size of a particular wide IO.

| index | = index of desired wide IO |

Definition at line 54 of file lpc_util.c.

References _LPCB_DEV, wide_io_ioport_and_bits::alt, ARRAY_SIZE, LPC_ALT_WIDEIO_RANGE_ENABLE, LPC_IO_OR_MEM_DECODE_ENABLE, pci_read_config32(), pci_read_config8(), and wio_io_en.

Referenced by configure_child_lpc_windows(), and lpc_find_wideio_range().