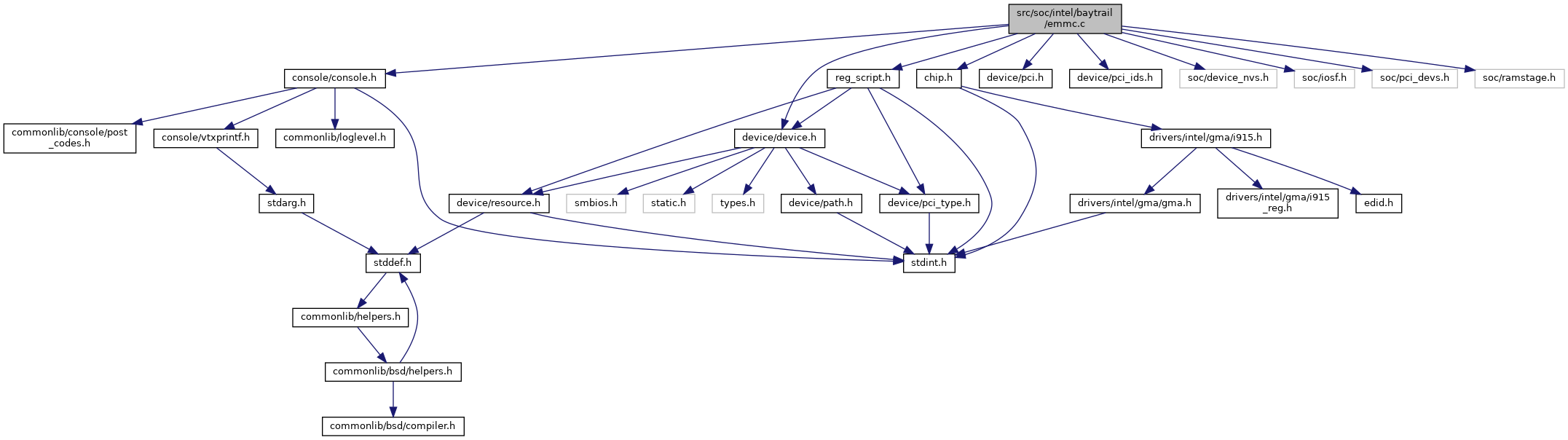

#include <console/console.h>

#include <device/device.h>

#include <device/pci.h>

#include <device/pci_ids.h>

#include <reg_script.h>

#include <soc/device_nvs.h>

#include <soc/iosf.h>

#include <soc/pci_devs.h>

#include <soc/ramstage.h>

#include "chip.h"

Go to the source code of this file.

◆ emmc_init()

◆ __pci_driver

| const struct pci_driver southcluster __pci_driver |

|

static |

Initial value:= {

}

static struct device_operations device_ops

Definition at line 33 of file emmc.c.

◆ device_ops

Initial value:= {

}

static void emmc_init(struct device *dev)

void pci_dev_enable_resources(struct device *dev)

void pci_dev_read_resources(struct device *dev)

void pci_dev_set_resources(struct device *dev)

struct pci_operations soc_pci_ops

Definition at line 33 of file emmc.c.

◆ emmc_ops

Initial value:= {

}

#define PCI_BASE_ADDRESS_0

#define REG_PCI_OR32(reg_, value_)

#define REG_RES_WRITE8(bar_, reg_, value_)

#define REG_PCI_WRITE32(reg_, value_)

Definition at line 1 of file emmc.c.