|

coreboot

coreboot is an Open Source project aimed at replacing the proprietary BIOS found in most computers.

|

|

coreboot

coreboot is an Open Source project aimed at replacing the proprietary BIOS found in most computers.

|

#include <stdint.h>

Go to the source code of this file.

Data Structures | |

| struct | dll_setting |

| struct | rt_dqs_setting |

| struct | timings |

| struct | dimminfo |

| struct | rcven_timings |

| struct | sysinfo |

Enumerations | |

| enum | fsb_clock { FSB_CLOCK_800MHz = 0 , FSB_CLOCK_1066MHz = 1 , FSB_CLOCK_1333MHz = 2 } |

| enum | mem_clock { MEM_CLOCK_400MHz = 0 , MEM_CLOCK_533MHz = 1 , MEM_CLOCK_667MHz = 2 , MEM_CLOCK_800MHz = 3 , MEM_CLOCK_1066MHz = 4 , MEM_CLOCK_1333MHz = 5 } |

| enum | ddr { DDR2 = 2 , DDR3 = 3 , DDR2 = 2 , DDR3 = 3 } |

| enum | ddrxspd { DDR2SPD = 0x8 , DDR3SPD = 0xb } |

| enum | chip_width { CHIP_WIDTH_x4 = 0 , CHIP_WIDTH_x8 = 1 , CHIP_WIDTH_x16 = 2 , CHIP_WIDTH_x32 = 3 , CHIP_WIDTH_x4 = 0 , CHIP_WIDTH_x8 = 1 , CHIP_WIDTH_x16 = 2 , CHIP_WIDTH_x32 = 3 } |

| enum | chip_cap { CHIP_CAP_256M = 0 , CHIP_CAP_512M = 1 , CHIP_CAP_1G = 2 , CHIP_CAP_2G = 3 , CHIP_CAP_4G = 4 , CHIP_CAP_8G = 5 , CHIP_CAP_16G = 6 , CHIP_CAP_256M = 0 , CHIP_CAP_512M = 1 , CHIP_CAP_1G = 2 , CHIP_CAP_2G = 3 , CHIP_CAP_4G = 4 , CHIP_CAP_8G = 5 , CHIP_CAP_16G = 6 } |

| enum | n_banks { N_BANKS_4 = 0 , N_BANKS_8 = 1 } |

| enum | ddr2_signals { CLKSET0 = 0 , CTRL0 , CLKSET1 , CMD , CTRL1 , CTRL2 , CTRL3 } |

Functions | |

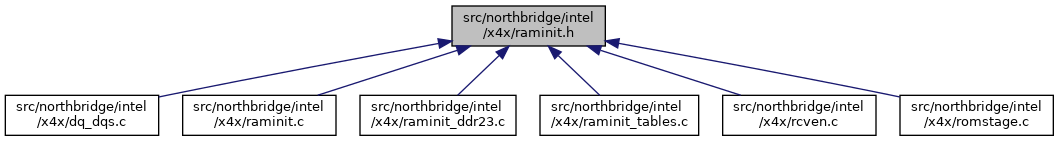

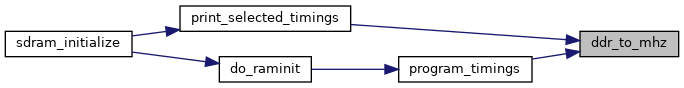

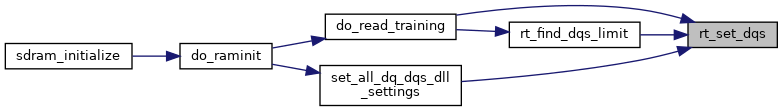

| void | sdram_initialize (int boot_path, const u8 *spd_map) |

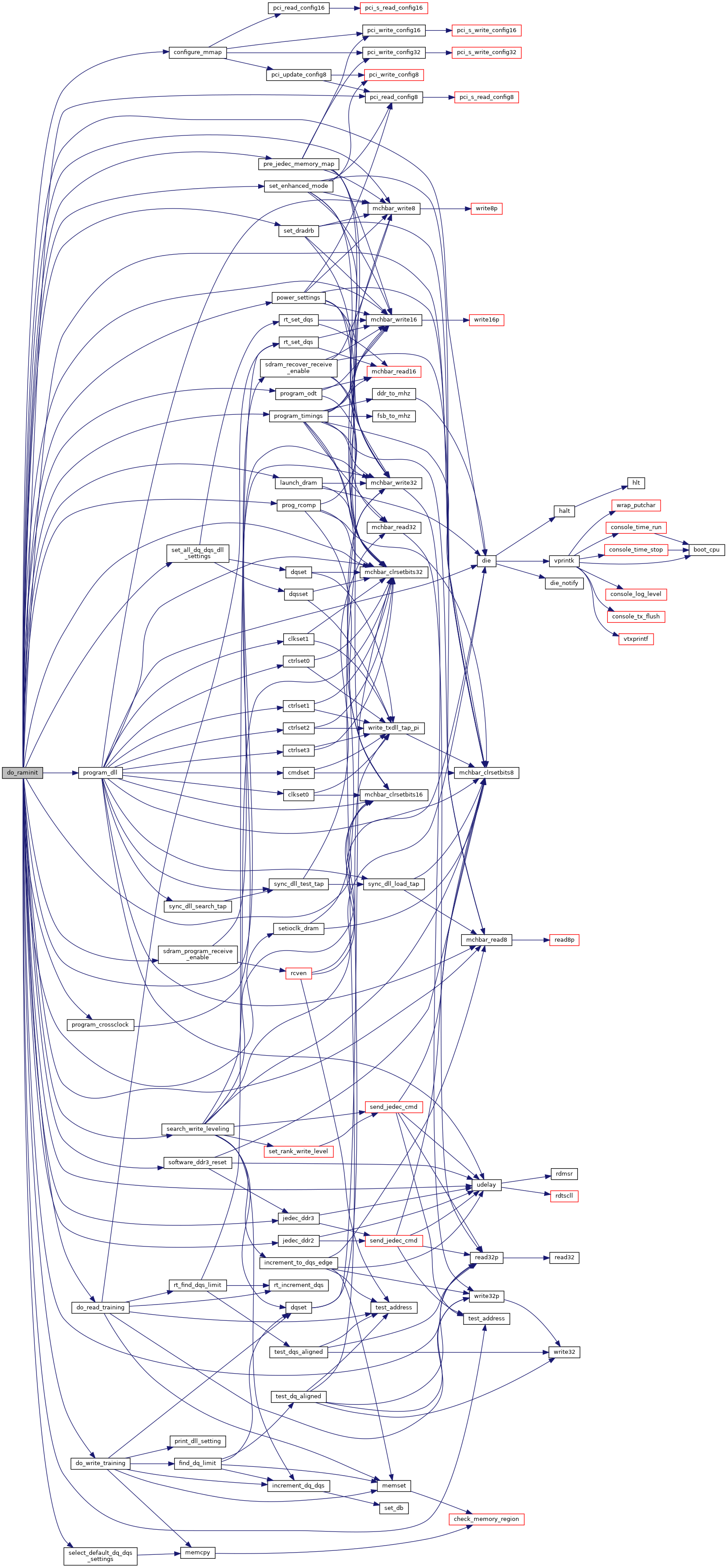

| void | do_raminit (struct sysinfo *, int fast_boot) |

| void | rcven (struct sysinfo *s) |

| u32 | fsb_to_mhz (u32 speed) |

| u32 | ddr_to_mhz (u32 speed) |

| u32 | test_address (int channel, int rank) |

| void | dqsset (u8 ch, u8 lane, const struct dll_setting *setting) |

| All finer DQ and DQS DLL settings are set to the same value for each rank in a channel, while coarse is common. More... | |

| void | dqset (u8 ch, u8 lane, const struct dll_setting *setting) |

| void | rt_set_dqs (u8 channel, u8 lane, u8 rank, struct rt_dqs_setting *dqs_setting) |

| int | do_write_training (struct sysinfo *s) |

| int | do_read_training (struct sysinfo *s) |

| void | search_write_leveling (struct sysinfo *s) |

| void | send_jedec_cmd (const struct sysinfo *s, u8 r, u8 ch, u8 cmd, u32 val) |

| #define BOTH_DIMMS_ARE_POPULATED | ( | dimms, | |

| ch | |||

| ) |

| #define CHANNEL_IS_CARDF | ( | dimms, | |

| idx | |||

| ) |

| #define CHANNEL_IS_POPULATED | ( | dimms, | |

| idx | |||

| ) |

| #define DIMM_IS_POPULATED | ( | dimms, | |

| idx | |||

| ) | (dimms[idx].card_type != RAW_CARD_UNPOPULATED) |

| #define DIMMS_PER_CHANNEL (TOTAL_DIMMS / TOTAL_CHANNELS) |

| #define FOR_EACH_BYTELANE | ( | l | ) | for (l = 0; l < TOTAL_BYTELANES; l++) |

| #define FOR_EACH_CHANNEL | ( | idx | ) | for (idx = 0; idx < TOTAL_CHANNELS; ++idx) |

| #define FOR_EACH_DIMM | ( | idx | ) | for (idx = 0; idx < TOTAL_DIMMS; ++idx) |

| #define FOR_EACH_DIMM_IN_CHANNEL | ( | ch, | |

| idx | |||

| ) | for (idx = (ch) << 1; idx < ((ch) << 1) + DIMMS_PER_CHANNEL; ++idx) |

| #define FOR_EACH_POPULATED_CHANNEL | ( | dimms, | |

| idx | |||

| ) | FOR_EACH_CHANNEL(idx) IF_CHANNEL_POPULATED(dimms, idx) |

| #define FOR_EACH_POPULATED_CHANNEL_AND_BYTELANE | ( | dimms, | |

| ch, | |||

| l | |||

| ) | FOR_EACH_POPULATED_CHANNEL (dimms, ch) FOR_EACH_BYTELANE(l) |

| #define FOR_EACH_POPULATED_DIMM | ( | dimms, | |

| idx | |||

| ) | FOR_EACH_DIMM(idx) IF_DIMM_POPULATED(dimms, idx) |

| #define FOR_EACH_POPULATED_DIMM_IN_CHANNEL | ( | dimms, | |

| ch, | |||

| idx | |||

| ) | FOR_EACH_DIMM_IN_CHANNEL(ch, idx) IF_DIMM_POPULATED(dimms, idx) |

| #define FOR_EACH_POPULATED_RANK | ( | dimms, | |

| ch, | |||

| r | |||

| ) | FOR_EACH_RANK(ch, r) IF_RANK_POPULATED(dimms, ch, r) |

| #define FOR_EACH_POPULATED_RANK_IN_CHANNEL | ( | dimms, | |

| ch, | |||

| r | |||

| ) | FOR_EACH_RANK_IN_CHANNEL(r) IF_RANK_POPULATED(dimms, ch, r) |

| #define FOR_EACH_RANK | ( | ch, | |

| r | |||

| ) | FOR_EACH_CHANNEL(ch) FOR_EACH_RANK_IN_CHANNEL(r) |

| #define FOR_EACH_RANK_IN_CHANNEL | ( | r | ) | for (r = 0; r < RANKS_PER_CHANNEL; ++r) |

| #define IF_CHANNEL_POPULATED | ( | dimms, | |

| idx | |||

| ) |

| #define IF_DIMM_POPULATED | ( | dimms, | |

| idx | |||

| ) | if (dimms[idx].card_type != RAW_CARD_UNPOPULATED) |

| #define IF_RANK_POPULATED | ( | dimms, | |

| ch, | |||

| r | |||

| ) |

| #define ONLY_DIMMA_IS_POPULATED | ( | dimms, | |

| ch | |||

| ) |

| #define ONLY_DIMMB_IS_POPULATED | ( | dimms, | |

| ch | |||

| ) |

| #define RANK_IS_POPULATED | ( | dimms, | |

| ch, | |||

| r | |||

| ) |

| enum chip_cap |

| enum chip_width |

| enum ddr2_signals |

| enum fsb_clock |

| enum mem_clock |

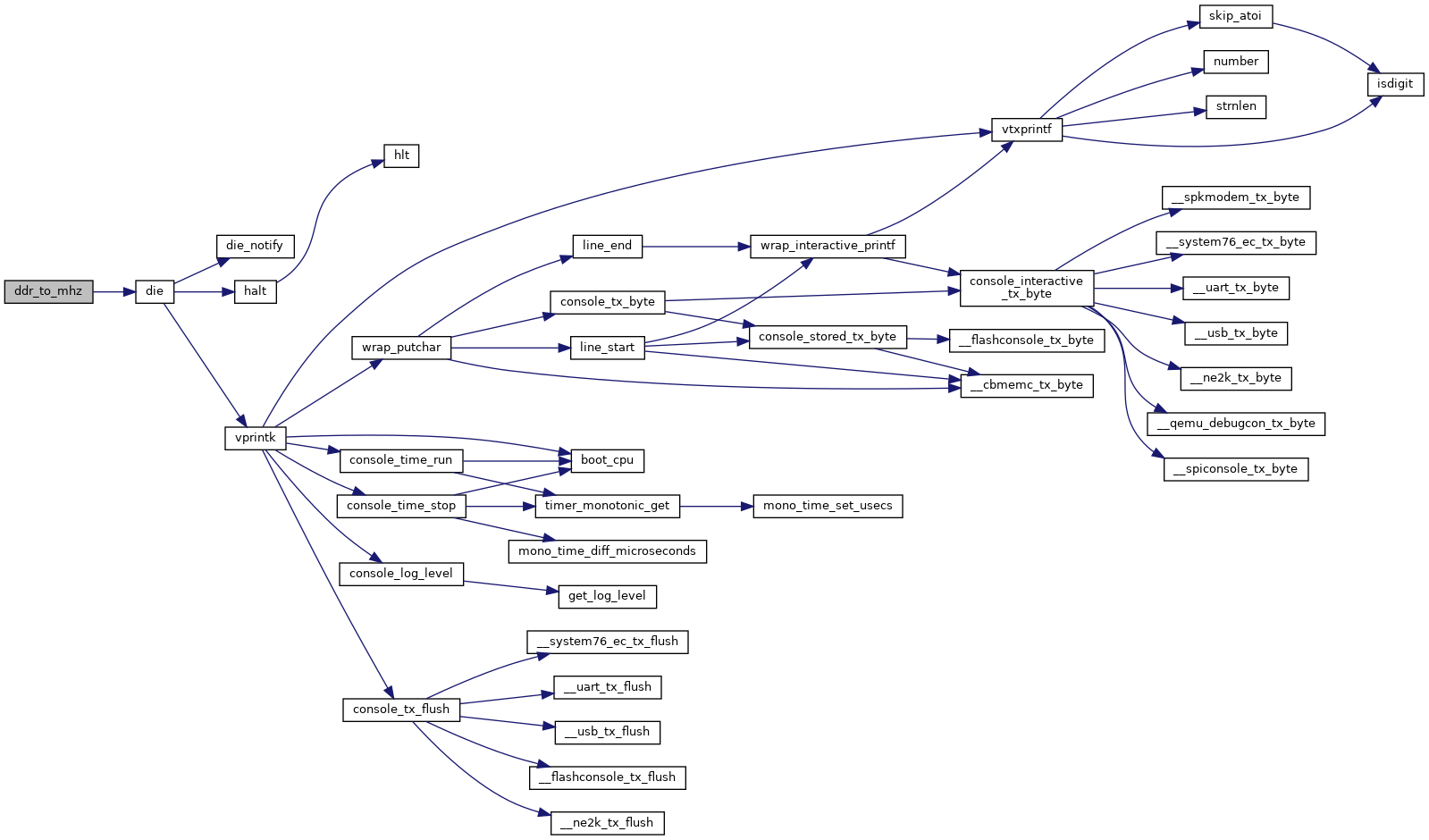

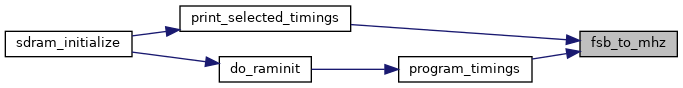

Definition at line 26 of file raminit_ddr23.c.

References ARRAY_SIZE, die(), and mhz.

Referenced by print_selected_timings(), and program_timings().

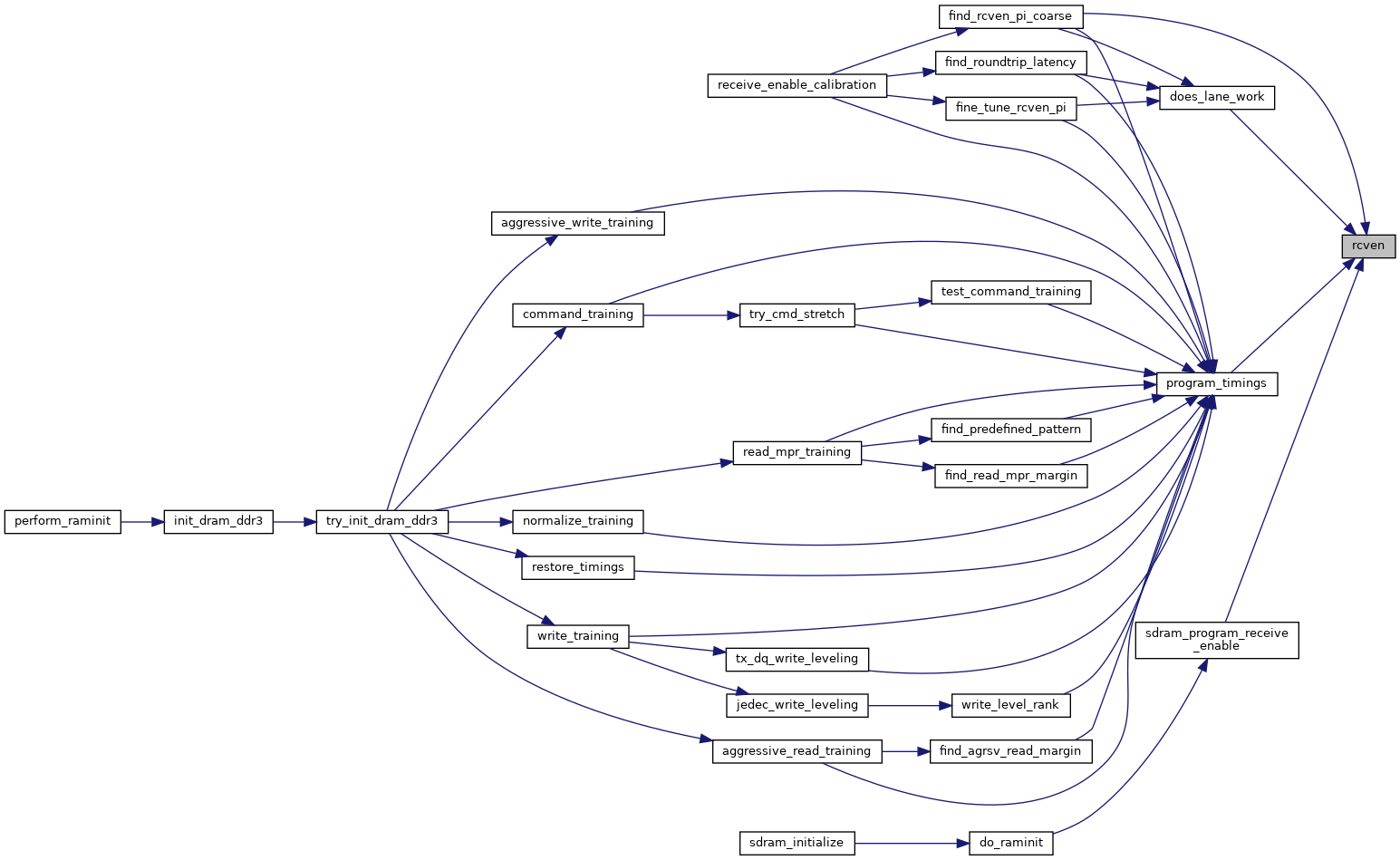

Definition at line 1932 of file raminit_ddr23.c.

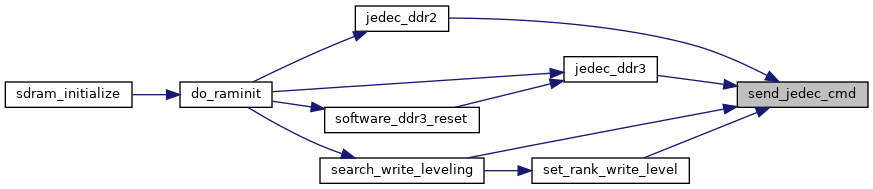

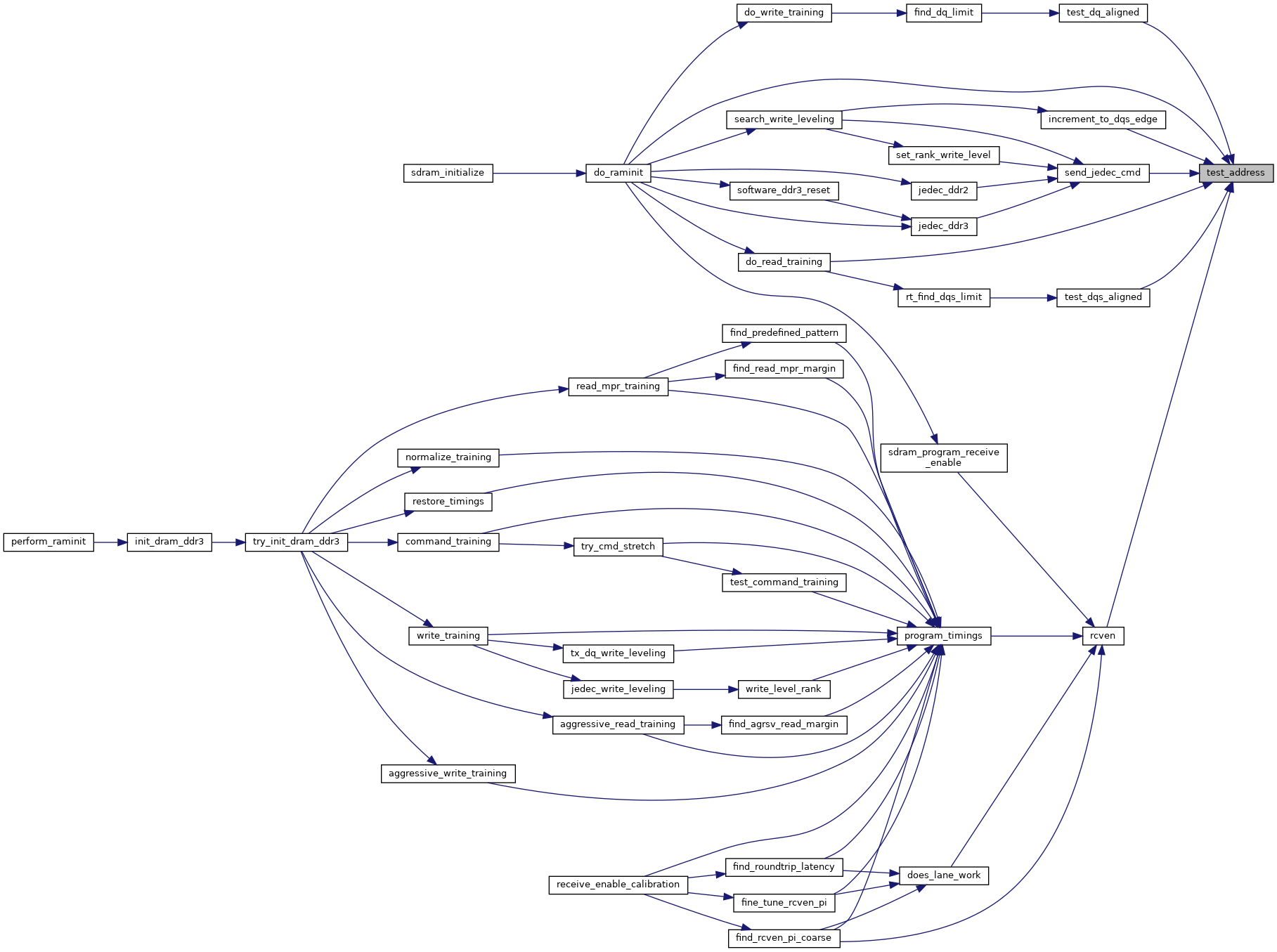

References BIOS_DEBUG, BOOT_PATH_NORMAL, BOOT_PATH_RESUME, BOOT_PATH_WARM_RESET, ch, CHANNEL_IS_POPULATED, CLKCFG_MCHBAR, CLKCFG_MEMCLK_MASK, CLKCFG_MEMCLK_SHIFT, CLKCFG_UPDATE, configure_mmap(), DDR2, DDR3, die(), do_read_training(), do_write_training(), FOR_EACH_CHANNEL, FOR_EACH_POPULATED_CHANNEL, FOR_EACH_POPULATED_RANK, FSB_CLOCK_1066MHz, HOST_BRIDGE, jedec_ddr2(), jedec_ddr3(), launch_dram(), mchbar_clrbits8, mchbar_clrsetbits16(), mchbar_clrsetbits32(), mchbar_clrsetbits8(), mchbar_read8(), mchbar_setbits16, mchbar_setbits32, mchbar_setbits8, mchbar_write16(), mchbar_write32(), mchbar_write8(), ME_UMA_SIZEMB, MEM_CLOCK_667MHz, pci_read_config8(), PMSTS_BOTH_SELFREFRESH, PMSTS_MCHBAR, post_jedec_tab, power_settings(), pre_jedec_memory_map(), printk, prog_rcomp(), program_crossclock(), program_dll(), program_odt(), program_timings(), RANK_IS_POPULATED, read32p(), s, sdram_program_receive_enable(), search_write_leveling(), select_default_dq_dqs_settings(), set_all_dq_dqs_dll_settings(), set_dradrb(), set_enhanced_mode(), setioclk_dram(), software_ddr3_reset(), test_address(), and udelay().

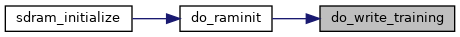

Referenced by sdram_initialize().

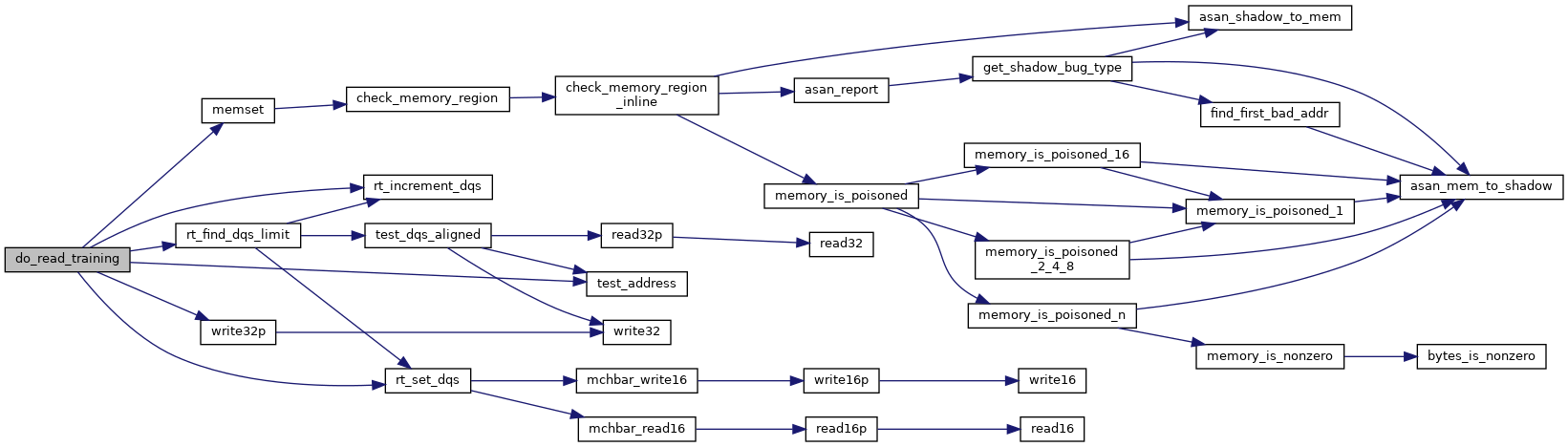

| int do_read_training | ( | struct sysinfo * | s | ) |

Definition at line 421 of file dq_dqs.c.

References address, BIOS_CRIT, BIOS_DEBUG, BIOS_ERR, CB_ERR, CB_SUCCESS, FAILING, FOR_EACH_BYTELANE, FOR_EACH_POPULATED_CHANNEL, FOR_EACH_POPULATED_RANK_IN_CHANNEL, FOR_EACH_RANK_IN_CHANNEL, memset(), printk, RAM_DEBUG, read_training_schedule, rt_find_dqs_limit(), rt_increment_dqs(), RT_LOOPS, RT_PATTERN_SIZE, rt_set_dqs(), s, SUCCEEDING, test_address(), TOTAL_BYTELANES, TOTAL_CHANNELS, and write32p().

Referenced by do_raminit().

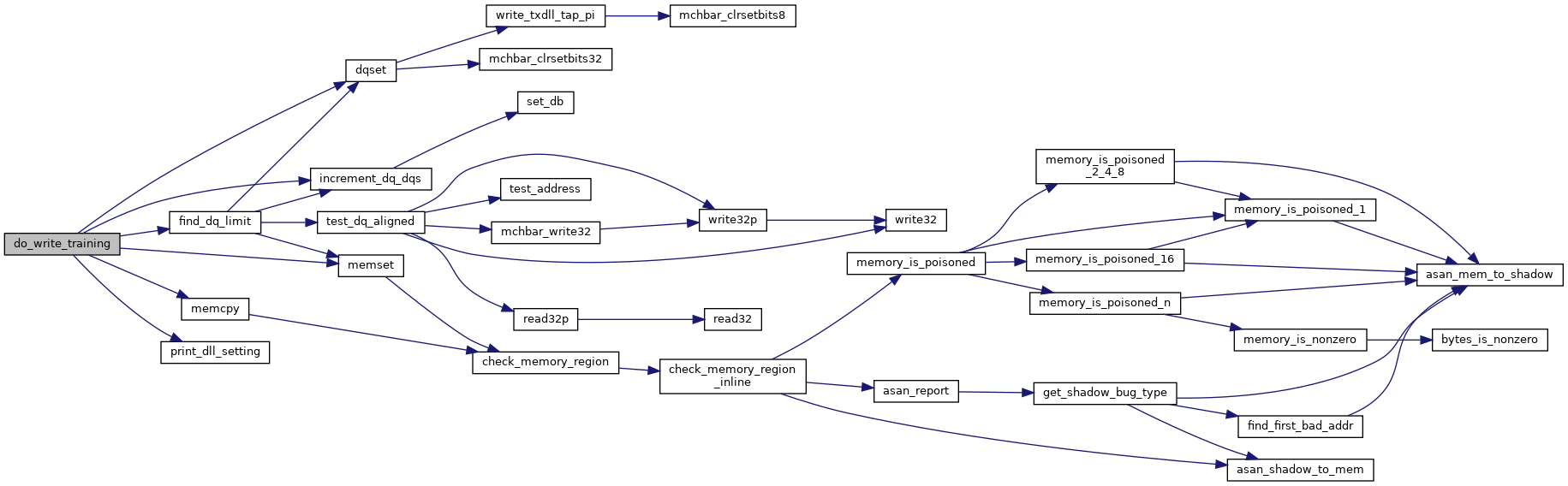

| int do_write_training | ( | struct sysinfo * | s | ) |

Definition at line 253 of file dq_dqs.c.

References BIOS_CRIT, BIOS_DEBUG, BIOS_ERR, BIOS_WARNING, CB_ERR, CB_SUCCESS, CONSISTENCY, dqset(), FAILING, find_dq_limit(), FOR_EACH_BYTELANE, FOR_EACH_POPULATED_CHANNEL, increment_dq_dqs(), memcpy(), memset(), print_dll_setting(), printk, RAM_DEBUG, s, SUCCEEDING, and TOTAL_BYTELANES.

Referenced by do_raminit().

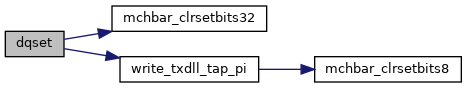

| void dqset | ( | u8 | ch, |

| u8 | lane, | ||

| const struct dll_setting * | setting | ||

| ) |

Definition at line 351 of file raminit_ddr23.c.

References ch, dll_setting::clk_delay, dll_setting::coarse, dll_setting::db_en, dll_setting::db_sel, mchbar_clrsetbits32(), dll_setting::pi, dll_setting::tap, and write_txdll_tap_pi().

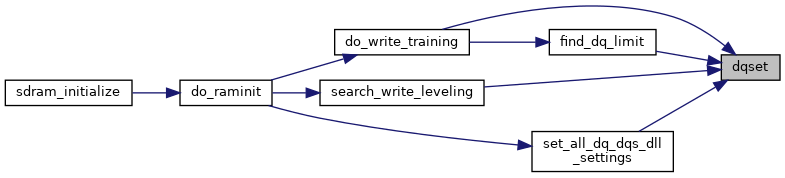

Referenced by do_write_training(), find_dq_limit(), search_write_leveling(), and set_all_dq_dqs_dll_settings().

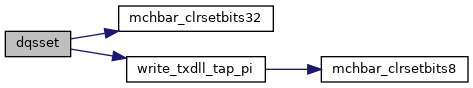

| void dqsset | ( | u8 | ch, |

| u8 | lane, | ||

| const struct dll_setting * | setting | ||

| ) |

All finer DQ and DQS DLL settings are set to the same value for each rank in a channel, while coarse is common.

Definition at line 332 of file raminit_ddr23.c.

References ch, dll_setting::clk_delay, dll_setting::coarse, dll_setting::db_en, dll_setting::db_sel, mchbar_clrsetbits32(), dll_setting::pi, dll_setting::tap, and write_txdll_tap_pi().

Referenced by set_all_dq_dqs_dll_settings().

Definition at line 21 of file raminit_ddr23.c.

Referenced by print_selected_timings(), and program_timings().

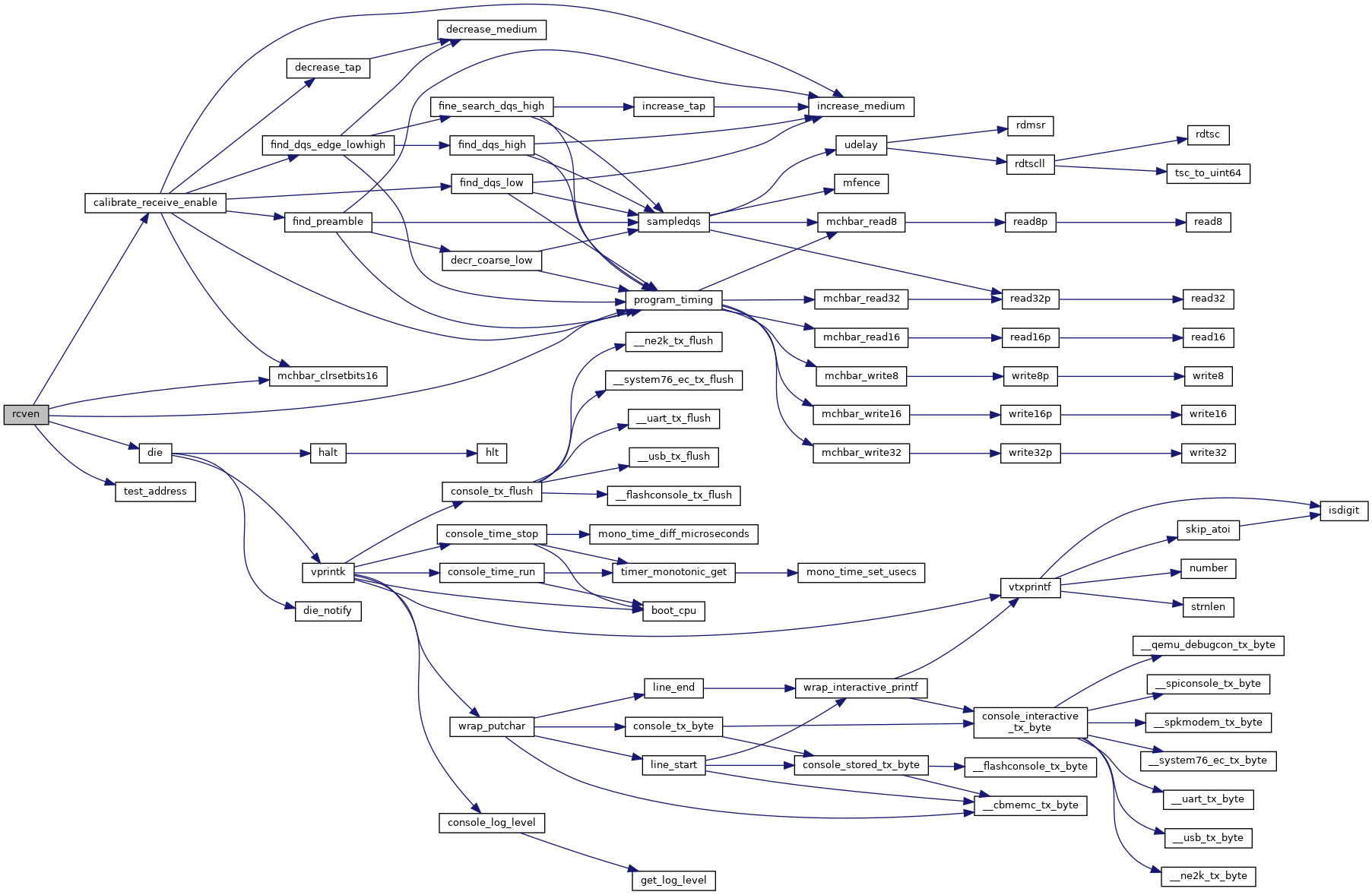

Definition at line 282 of file rcven.c.

References addr, BIOS_DEBUG, calibrate_receive_enable(), rec_timing::coarse, die(), FOR_EACH_BYTELANE, FOR_EACH_POPULATED_CHANNEL, FOR_EACH_POPULATED_RANK_IN_CHANNEL, mchbar_clrbits8, mchbar_clrsetbits16(), rec_timing::medium, rec_timing::pi, printk, program_timing(), s, rec_timing::tap, test_address(), and TOTAL_BYTELANES.

Referenced by does_lane_work(), find_rcven_pi_coarse(), program_timings(), and sdram_program_receive_enable().

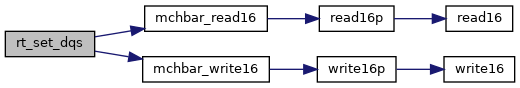

| void rt_set_dqs | ( | u8 | channel, |

| u8 | lane, | ||

| u8 | rank, | ||

| struct rt_dqs_setting * | dqs_setting | ||

| ) |

Definition at line 369 of file raminit_ddr23.c.

References mchbar_read16(), mchbar_write16(), rt_dqs_setting::pi, printk, RAM_SPEW, and rt_dqs_setting::tap.

Referenced by do_read_training(), rt_find_dqs_limit(), and set_all_dq_dqs_dll_settings().

| boot_path | 0 = normal, 1 = reset, 2 = resume from s3 |

| spd_addresses | pointer to a list of SPD addresses |

| boot_path | 0 = normal, 1 = reset, 2 = resume from s3 |

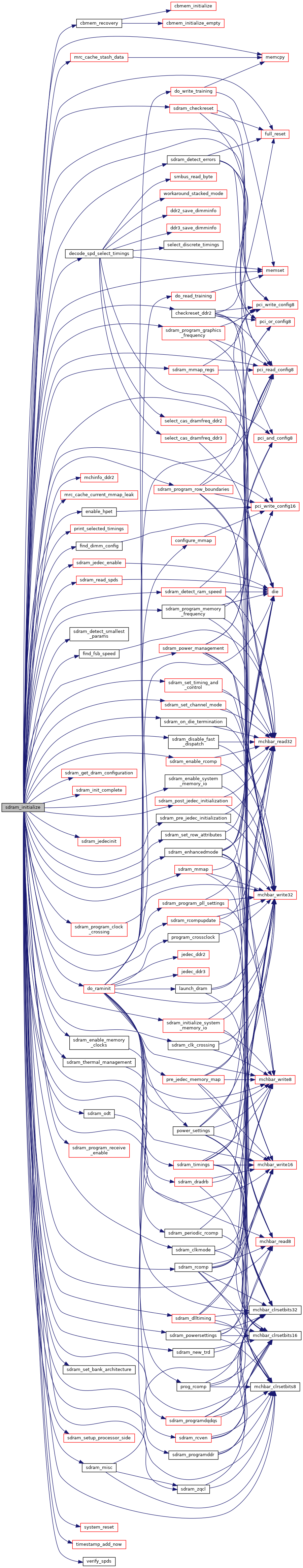

Definition at line 2682 of file raminit.c.

References BIOS_DEBUG, sys_info::boot_path, sysinfo::boot_path, BOOT_PATH_NORMAL, BOOT_PATH_RESET, BOOT_PATH_RESUME, BOOT_PATH_WARM_RESET, C0CKECTRL, C0DMC, C0IOBUFACTCTL, C0REFRCTRL2, C0RSTCTL, C1DMC, CB_SUCCESS, cbmem_recovery(), checkreset_ddr2(), COMPCTRL1, CONFIG, CPCTL, decode_spd_select_timings(), do_raminit(), enable_hpet(), find_dimm_config(), find_fsb_speed(), full_reset(), GCFC, GEN_PMCON_2, HIT4, HOST_BRIDGE, IGD_DEV, sysinfo::max_fsb, mchbar_clrsetbits8(), mchbar_read8(), mchbar_setbits16, mchbar_setbits32, mchbar_setbits8, mchinfo_ddr2(), memcpy(), memset(), mrc_cache_current_mmap_leak(), mrc_cache_stash_data(), MRC_CACHE_VERSION, MRC_TRAINING_DATA, pci_and_config8(), PCI_DEV, pci_or_config8(), pci_read_config8(), pci_write_config16(), pci_write_config8(), print_selected_timings(), printk, PRINTK_DEBUG, s, sysinfo::s3resume, sdram_checkreset(), sdram_clk_crossing(), sdram_clkmode(), sdram_detect_errors(), sdram_detect_ram_speed(), sdram_detect_smallest_params(), sdram_disable_fast_dispatch(), sdram_dlltiming(), sdram_dradrb(), sdram_enable_memory_clocks(), sdram_enable_rcomp(), sdram_enable_system_memory_io(), sdram_enhancedmode(), sdram_get_dram_configuration(), sdram_init_complete(), sdram_initialize_system_memory_io(), sdram_jedec_enable(), sdram_jedecinit(), sdram_misc(), sdram_mmap(), sdram_mmap_regs(), sdram_new_trd(), sdram_odt(), sdram_on_die_termination(), sdram_periodic_rcomp(), sdram_post_jedec_initialization(), sdram_power_management(), sdram_powersettings(), sdram_pre_jedec_initialization(), sdram_program_clock_crossing(), sdram_program_graphics_frequency(), sdram_program_memory_frequency(), sdram_program_pll_settings(), sdram_program_receive_enable(), sdram_program_row_boundaries(), sdram_programddr(), sdram_programdqdqs(), sdram_rcomp(), sdram_rcompupdate(), sdram_rcven(), sdram_read_spds(), sdram_set_bank_architecture(), sdram_set_channel_mode(), sdram_set_row_attributes(), sdram_set_timing_and_control(), sdram_setup_processor_side(), sdram_thermal_management(), sdram_timings(), sdram_zqcl(), sys_info::spd_addresses, sysinfo::spd_map, system_reset(), timestamp_add_now(), TS_INITRAM_END, TS_INITRAM_START, and verify_spds().

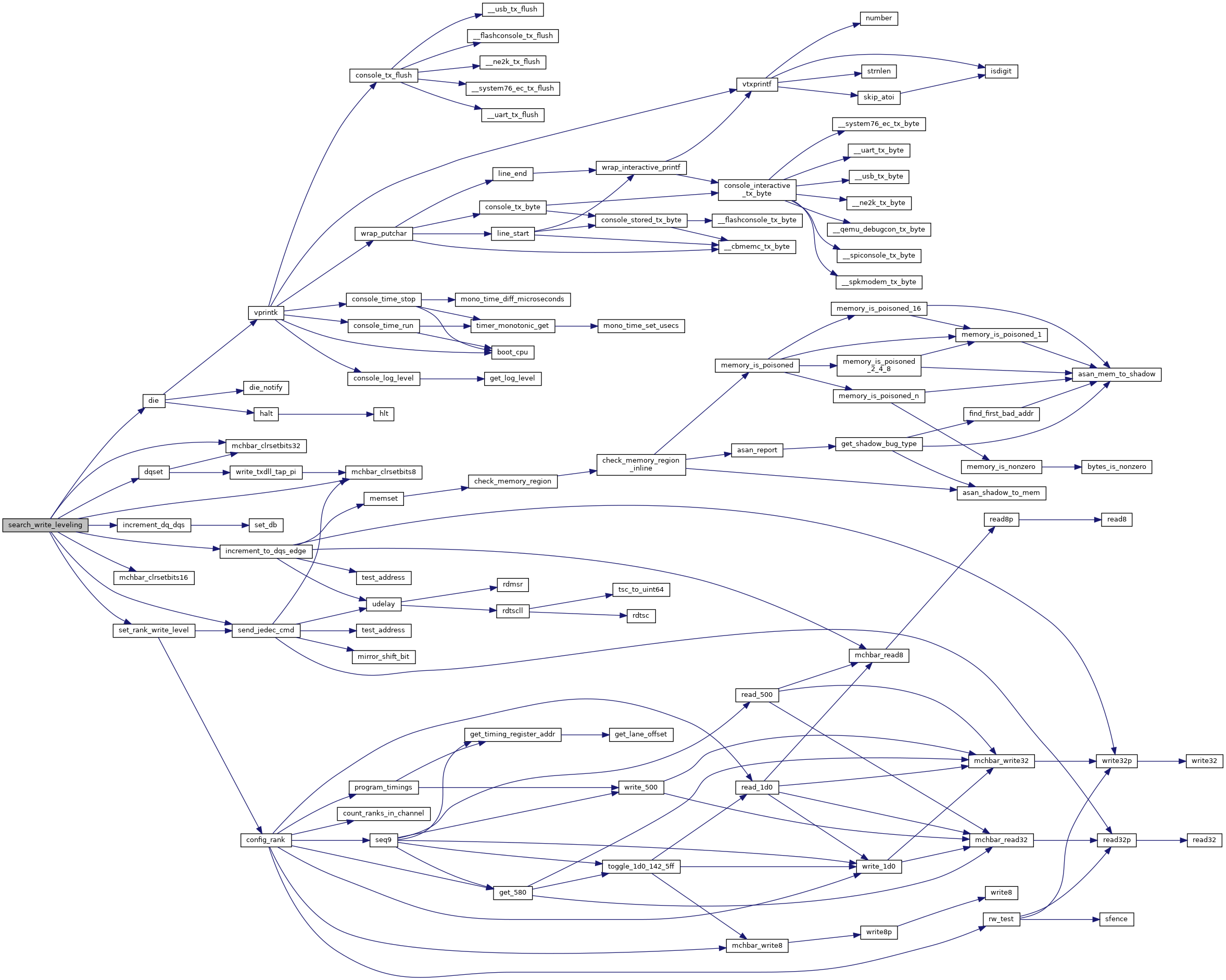

Definition at line 740 of file dq_dqs.c.

References BIOS_DEBUG, ch, config, count, die(), dqset(), FOR_EACH_POPULATED_CHANNEL, FOR_EACH_POPULATED_CHANNEL_AND_BYTELANE, FOR_EACH_POPULATED_RANK_IN_CHANNEL, increment_dq_dqs(), increment_to_dqs_edge(), mchbar_clrbits8, mchbar_clrsetbits16(), mchbar_clrsetbits32(), mchbar_clrsetbits8(), mchbar_setbits8, MEM_CLOCK_1066MHz, MEM_CLOCK_1333MHz, MEM_CLOCK_800MHz, NORMALOP_CMD, printk, s, send_jedec_cmd(), and set_rank_write_level().

Referenced by do_raminit().

Definition at line 1264 of file raminit_ddr23.c.

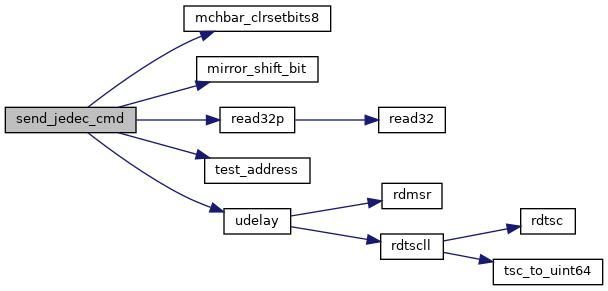

References addr, ch, DDR3, mchbar_clrsetbits8(), mirror_shift_bit(), NORMALOP_CMD, read32p(), s, test_address(), udelay(), and val.

Referenced by jedec_ddr2(), jedec_ddr3(), search_write_leveling(), and set_rank_write_level().

| u32 test_address | ( | int | channel, |

| int | rank | ||

| ) |

Definition at line 1245 of file raminit_ddr23.c.

Referenced by do_raminit(), do_read_training(), increment_to_dqs_edge(), rcven(), send_jedec_cmd(), test_dq_aligned(), and test_dqs_aligned().

|

extern |

Definition at line 311 of file raminit_tables.c.

Referenced by power_settings().

|

extern |

Definition at line 376 of file raminit_tables.c.

Referenced by power_settings().

|

extern |

Definition at line 355 of file raminit_tables.c.

Referenced by power_settings().

|

extern |

Definition at line 274 of file raminit_tables.c.

Referenced by jedec_ddr3(), and set_rank_write_level().

|

extern |

Definition at line 1 of file raminit_tables.c.

Referenced by program_dll().

|

extern |

Definition at line 1 of file raminit_tables.c.

Referenced by select_default_dq_dqs_settings().

|

extern |

Definition at line 1 of file raminit_tables.c.

Referenced by select_default_dq_dqs_settings().

|

extern |

Definition at line 1 of file raminit_tables.c.

Referenced by program_dll().

|

extern |

Definition at line 1 of file raminit_tables.c.

Referenced by select_default_dq_dqs_settings().

|

extern |

Definition at line 1 of file raminit_tables.c.

Referenced by select_default_dq_dqs_settings().

|

extern |

Definition at line 1 of file raminit_tables.c.

Referenced by program_dll().

|

extern |

Definition at line 1 of file raminit_tables.c.

Referenced by select_default_dq_dqs_settings().

|

extern |

Definition at line 1 of file raminit_tables.c.

Referenced by select_default_dq_dqs_settings().

|

extern |

Definition at line 1 of file raminit_tables.c.

Referenced by program_dll().

|

extern |

Definition at line 1 of file raminit_tables.c.

Referenced by select_default_dq_dqs_settings().

|

extern |

Definition at line 1 of file raminit_tables.c.

Referenced by select_default_dq_dqs_settings().

|

extern |

Definition at line 1 of file raminit_tables.c.

Referenced by program_dll().

|

extern |

Definition at line 1 of file raminit_tables.c.

Referenced by select_default_dq_dqs_settings().

|

extern |

Definition at line 1 of file raminit_tables.c.

Referenced by select_default_dq_dqs_settings().

|

extern |

Definition at line 293 of file raminit_tables.c.

Referenced by do_raminit().