|

coreboot

coreboot is an Open Source project aimed at replacing the proprietary BIOS found in most computers.

|

|

coreboot

coreboot is an Open Source project aimed at replacing the proprietary BIOS found in most computers.

|

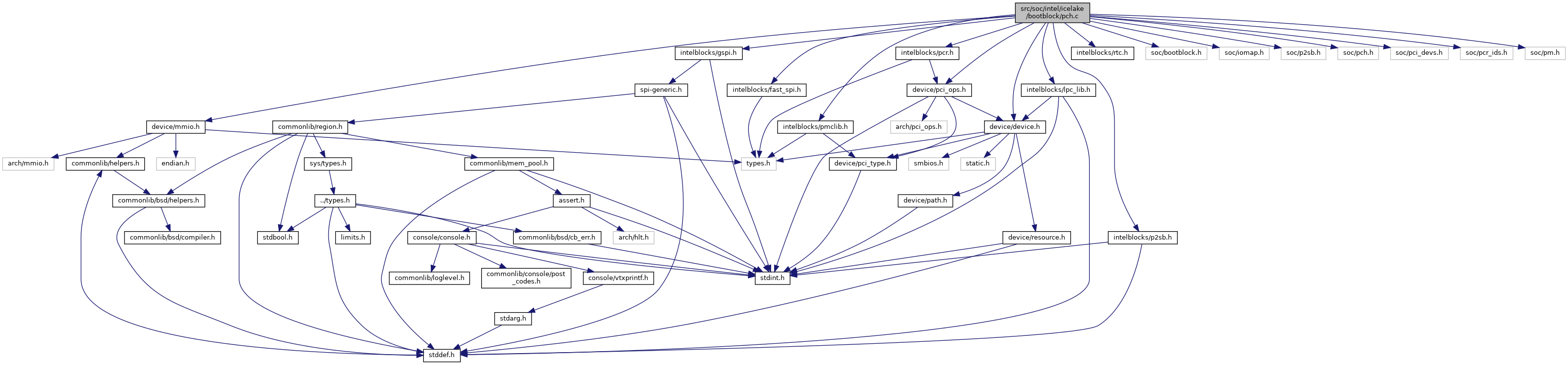

#include <device/mmio.h>#include <device/device.h>#include <device/pci_ops.h>#include <intelblocks/fast_spi.h>#include <intelblocks/gspi.h>#include <intelblocks/lpc_lib.h>#include <intelblocks/p2sb.h>#include <intelblocks/pcr.h>#include <intelblocks/pmclib.h>#include <intelblocks/rtc.h>#include <soc/bootblock.h>#include <soc/iomap.h>#include <soc/p2sb.h>#include <soc/pch.h>#include <soc/pci_devs.h>#include <soc/pcr_ids.h>#include <soc/pm.h>

Go to the source code of this file.

Macros | |

| #define | PCR_PSF3_TO_SHDW_PMC_REG_BASE 0x0600 |

| #define | PCR_PSFX_TO_SHDW_BAR0 0 |

| #define | PCR_PSFX_TO_SHDW_BAR1 0x4 |

| #define | PCR_PSFX_TO_SHDW_BAR2 0x8 |

| #define | PCR_PSFX_TO_SHDW_BAR3 0xC |

| #define | PCR_PSFX_TO_SHDW_BAR4 0x10 |

| #define | PCR_PSFX_TO_SHDW_PCIEN_IOEN 0x01 |

| #define | PCR_PSFX_T0_SHDW_PCIEN 0x1C |

Functions | |

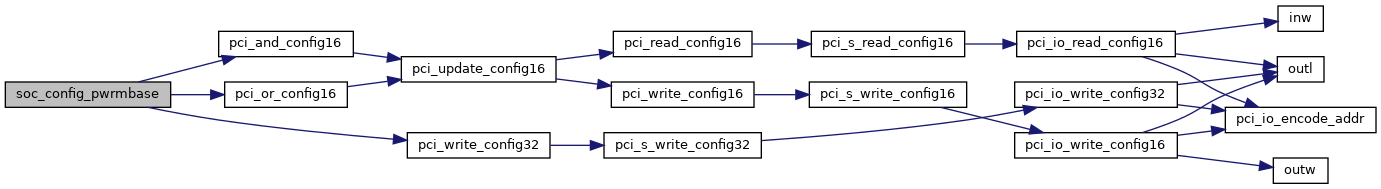

| static void | soc_config_pwrmbase (void) |

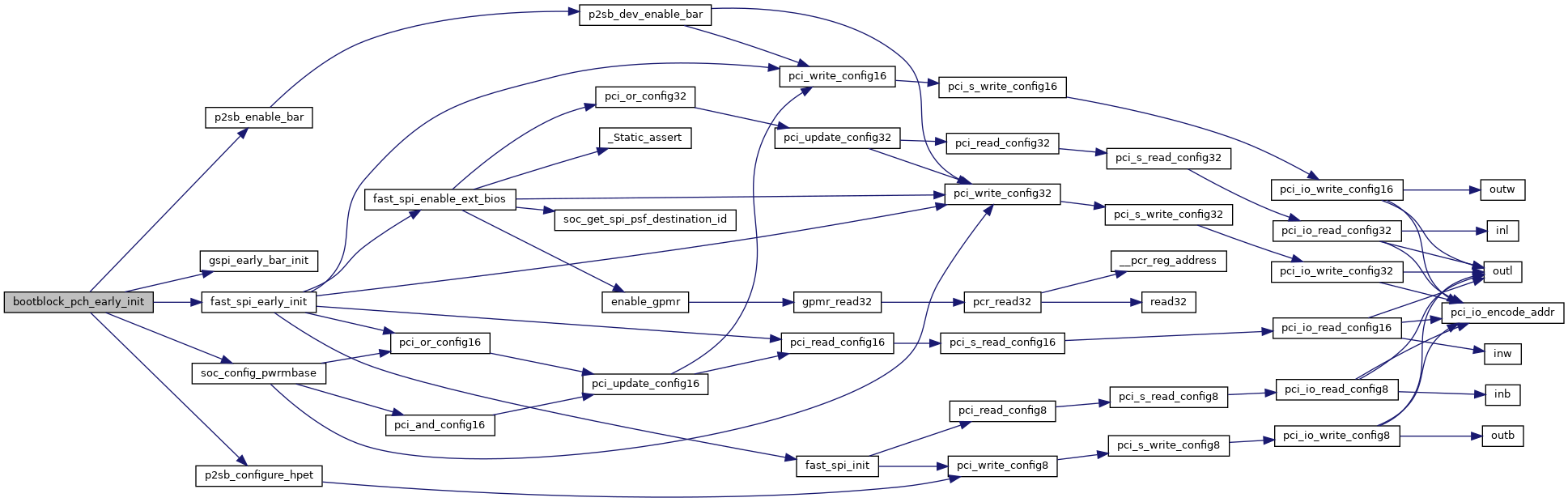

| void | bootblock_pch_early_init (void) |

| static void | soc_config_acpibase (void) |

| void | pch_early_iorange_init (void) |

| void | bootblock_pch_init (void) |

Definition at line 48 of file pch.c.

References fast_spi_early_init(), gspi_early_bar_init(), p2sb_configure_hpet(), p2sb_enable_bar(), soc_config_pwrmbase(), and SPI_BASE_ADDRESS.

Definition at line 106 of file pch.c.

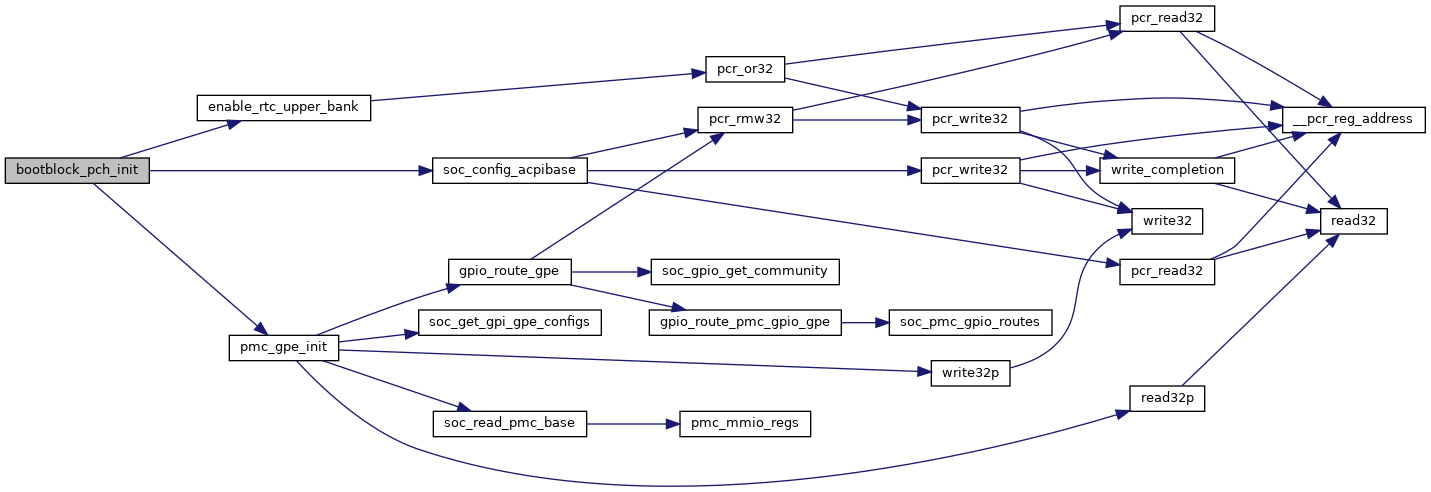

References enable_rtc_upper_bank(), pmc_gpe_init(), and soc_config_acpibase().

Definition at line 90 of file pch.c.

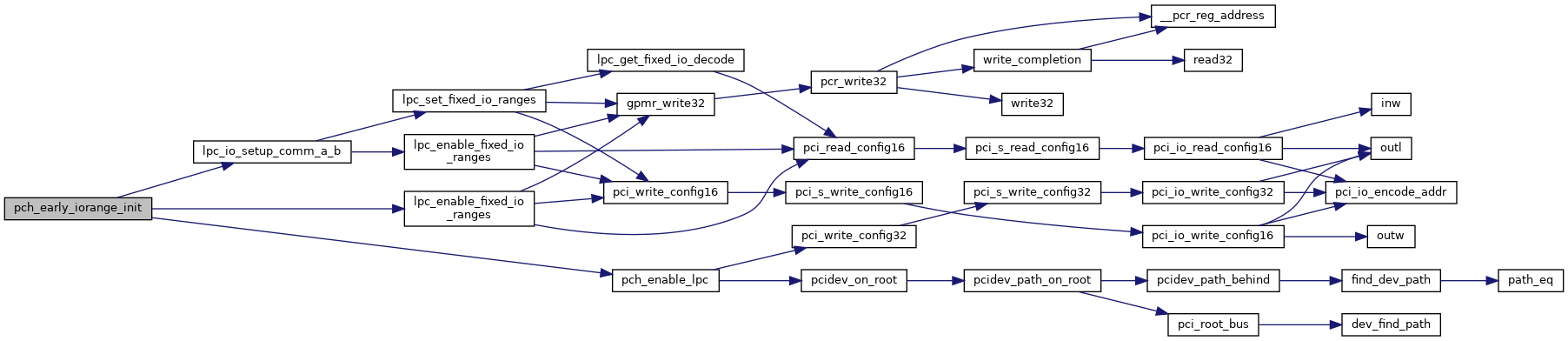

References CONFIG, lpc_enable_fixed_io_ranges(), lpc_io_setup_comm_a_b(), LPC_IOE_EC_62_66, LPC_IOE_KBC_60_64, LPC_IOE_LGE_200, LPC_IOE_SUPERIO_2E_2F, and pch_enable_lpc().

Definition at line 67 of file pch.c.

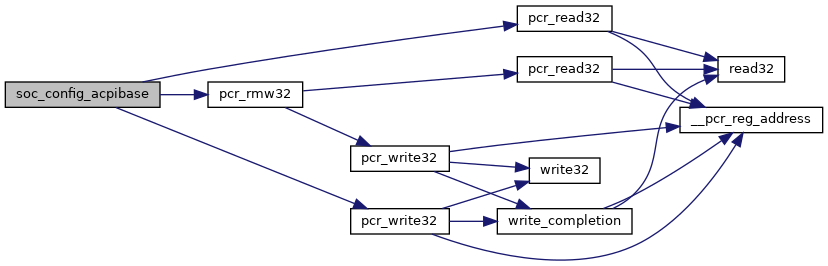

References ACPI_BASE_ADDRESS, PCR_PSF3_TO_SHDW_PMC_REG_BASE, PCR_PSFX_T0_SHDW_PCIEN, PCR_PSFX_TO_SHDW_BAR4, PCR_PSFX_TO_SHDW_PCIEN_IOEN, pcr_read32(), pcr_rmw32(), pcr_write32(), and PID_PSF3.

Referenced by bootblock_pch_init().

Definition at line 30 of file pch.c.

References ACTL, PCH_DEV_PMC, PCH_PWRM_BASE_ADDRESS, pci_and_config16(), PCI_COMMAND, PCI_COMMAND_MASTER, PCI_COMMAND_MEMORY, pci_or_config16(), pci_write_config32(), PWRM_EN, PWRMBASE, and setbits32.

Referenced by bootblock_pch_early_init().