|

coreboot

coreboot is an Open Source project aimed at replacing the proprietary BIOS found in most computers.

|

|

coreboot

coreboot is an Open Source project aimed at replacing the proprietary BIOS found in most computers.

|

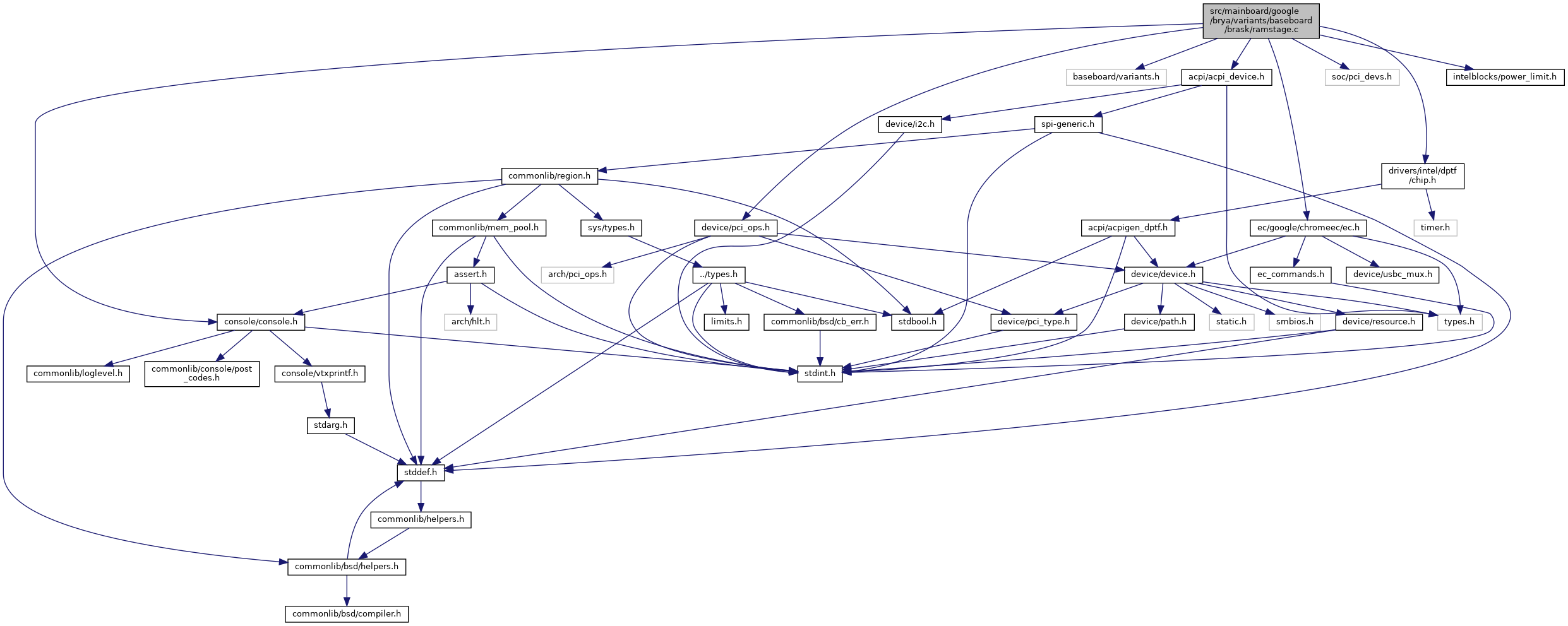

#include <acpi/acpi_device.h>#include <baseboard/variants.h>#include <console/console.h>#include <device/pci_ops.h>#include <ec/google/chromeec/ec.h>#include <soc/pci_devs.h>#include <drivers/intel/dptf/chip.h>#include <intelblocks/power_limit.h>

Go to the source code of this file.

Macros | |

| #define | SET_PSYSPL2(e, w) ((e) * (w) / 100) |

Functions | |

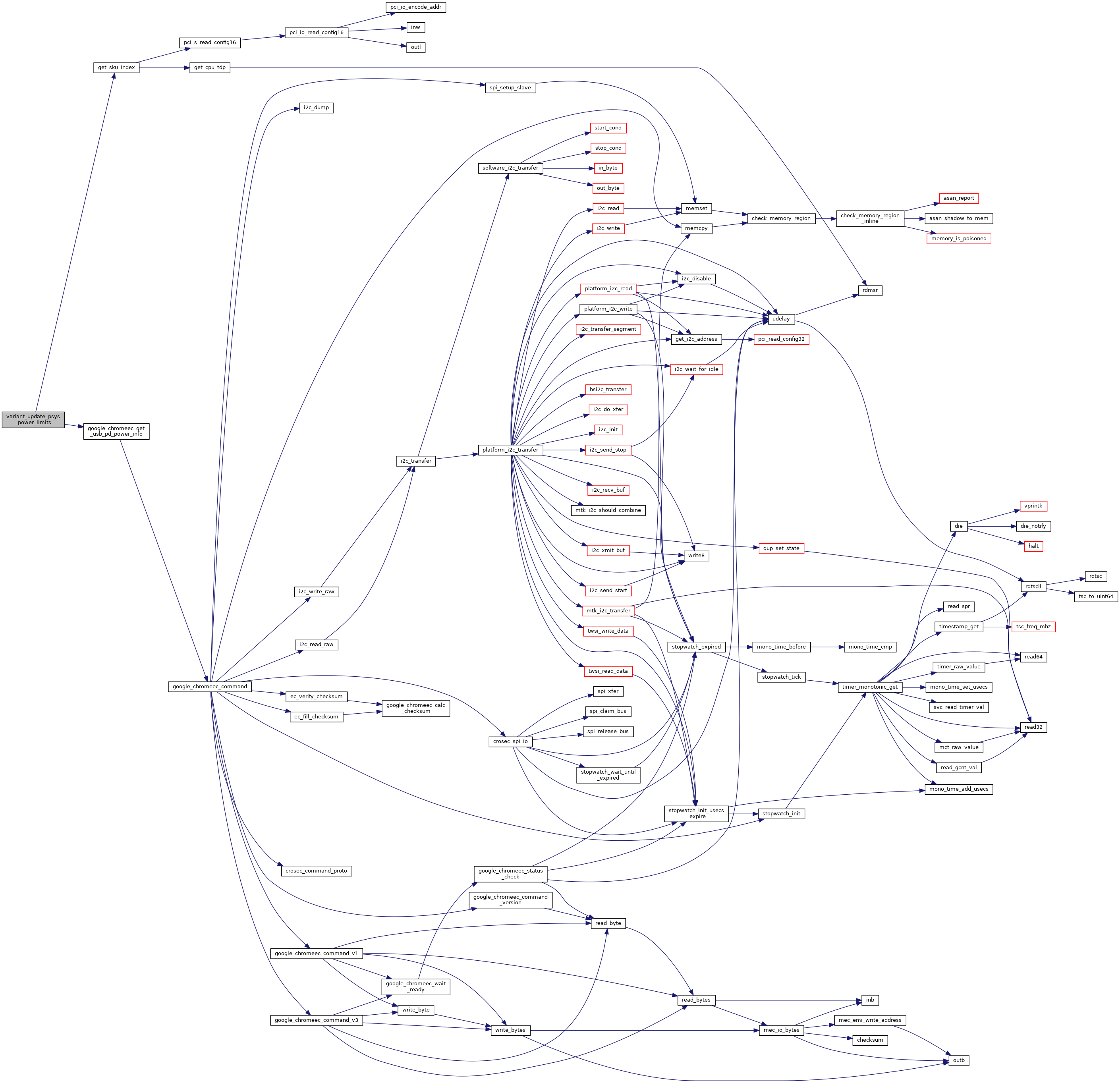

| WEAK_DEV_PTR (dptf_policy) | |

| static bool | get_sku_index (const struct cpu_power_limits *limits, size_t num_entries, size_t *intel_idx, size_t *brask_idx) |

| void | variant_update_power_limits (const struct cpu_power_limits *limits, size_t num_entries) |

| void | variant_update_psys_power_limits (const struct cpu_power_limits *limits, const struct system_power_limits *sys_limits, size_t num_entries, const struct psys_config *config_psys) |

| #define SET_PSYSPL2 | ( | e, | |

| w | |||

| ) | ((e) * (w) / 100) |

Definition at line 15 of file ramstage.c.

|

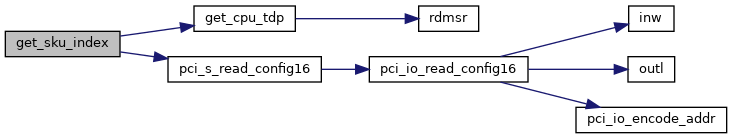

static |

Definition at line 17 of file ramstage.c.

References ARRAY_SIZE, BIOS_ERR, cpu_id, cpu_tdp, cpuid_to_adl, get_cpu_tdp(), limits, mchid, PCI_DEV, PCI_DEVICE_ID, pci_s_read_config16(), and printk.

Referenced by variant_update_power_limits(), and variant_update_psys_power_limits().

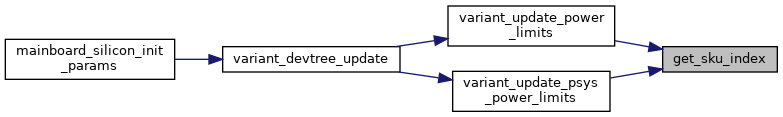

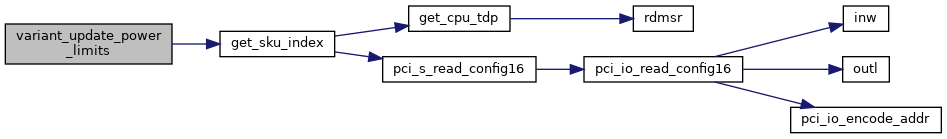

| void variant_update_power_limits | ( | const struct cpu_power_limits * | limits, |

| size_t | num_entries | ||

| ) |

Definition at line 51 of file ramstage.c.

References BIOS_INFO, device::chip_info, config, config_of_soc, DEV_PTR, DIV_ROUND_UP, get_sku_index(), limits, dptf_power_limit_config::max_power, MILLIWATTS_TO_WATTS, dptf_power_limit_config::min_power, dptf_power_limits::pl1, cpu_power_limits::pl1_max_power, cpu_power_limits::pl1_min_power, dptf_power_limits::pl2, cpu_power_limits::pl2_max_power, cpu_power_limits::pl2_min_power, printk, soc_power_limits_config::tdp_pl2_override, and soc_power_limits_config::tdp_pl4.

Referenced by variant_devtree_update().

| void variant_update_psys_power_limits | ( | const struct cpu_power_limits * | limits, |

| const struct system_power_limits * | sys_limits, | ||

| size_t | num_entries, | ||

| const struct psys_config * | config_psys | ||

| ) |

Definition at line 96 of file ramstage.c.

References BIOS_INFO, psys_config::bj_volts_mv, config_of_soc, DEV_PTR, DIV_ROUND_UP, psys_config::efficiency, get_sku_index(), google_chromeec_get_usb_pd_power_info(), limits, MILLIWATTS_TO_WATTS, printk, psys_config::psys_imax_ma, system_power_limits::psys_pl2_power, soc_power_limits_config::psys_pmax, SET_PSYSPL2, sys_limits, soc_power_limits_config::tdp_pl2_override, soc_power_limits_config::tdp_pl4, soc_power_limits_config::tdp_psyspl2, type, and USB_CHG_TYPE_PD.

Referenced by variant_devtree_update().

| WEAK_DEV_PTR | ( | dptf_policy | ) |