|

coreboot

coreboot is an Open Source project aimed at replacing the proprietary BIOS found in most computers.

|

|

coreboot

coreboot is an Open Source project aimed at replacing the proprietary BIOS found in most computers.

|

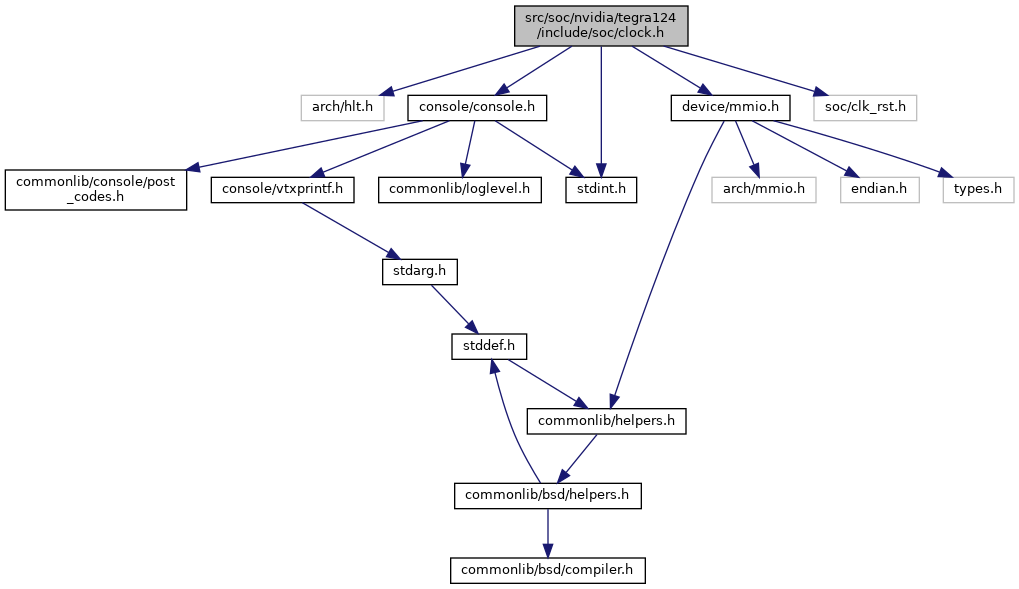

#include <arch/hlt.h>#include <console/console.h>#include <device/mmio.h>#include <soc/clk_rst.h>#include <stdint.h>

Go to the source code of this file.

Macros | |

| #define | CLOCK_PLL_STABLE_DELAY_US 300 |

| #define | IO_STABILIZATION_DELAY (2) |

| #define | CLK_DIVIDER(REF, FREQ) (DIV_ROUND_UP(((REF) * 2), (FREQ)) - 2) |

| #define | CLK_FREQUENCY(REF, REG) (((REF) * 2) / ((REG) + 2)) |

| #define | clock_configure_irregular_source(device, src, freq, src_id) |

| #define | clock_configure_source(device, src, freq) clock_configure_irregular_source(device, src, freq, src) |

| #define | clock_configure_i2c_scl_freq(device, src, freq) |

| #define | TEGRA_CLK_M_KHZ clock_get_osc_khz() |

| #define | TEGRA_PLLX_KHZ CONFIG_PLLX_KHZ |

| #define | TEGRA_PLLP_KHZ (408000) |

| #define | TEGRA_PLLC_KHZ (600000) |

| #define | TEGRA_PLLD_KHZ (925000) |

| #define | TEGRA_PLLU_KHZ (960000) |

| #define | TEGRA_SCLK_KHZ (300000) |

| #define | TEGRA_HCLK_RATIO 1 |

| #define | TEGRA_HCLK_KHZ (TEGRA_SCLK_KHZ / (1 + TEGRA_HCLK_RATIO)) |

| #define | TEGRA_PCLK_RATIO 0 |

| #define | TEGRA_PCLK_KHZ (TEGRA_HCLK_KHZ / (1 + TEGRA_PCLK_RATIO)) |

Enumerations | |

| enum | { CLK_L_CPU = 0x1 << 0 , CLK_L_COP = 0x1 << 1 , CLK_L_TRIG_SYS = 0x1 << 2 , CLK_L_RTC = 0x1 << 4 , CLK_L_TMR = 0x1 << 5 , CLK_L_UARTA = 0x1 << 6 , CLK_L_UARTB = 0x1 << 7 , CLK_L_GPIO = 0x1 << 8 , CLK_L_SDMMC2 = 0x1 << 9 , CLK_L_SPDIF = 0x1 << 10 , CLK_L_I2S1 = 0x1 << 11 , CLK_L_I2C1 = 0x1 << 12 , CLK_L_NDFLASH = 0x1 << 13 , CLK_L_SDMMC1 = 0x1 << 14 , CLK_L_SDMMC4 = 0x1 << 15 , CLK_L_PWM = 0x1 << 17 , CLK_L_I2S2 = 0x1 << 18 , CLK_L_EPP = 0x1 << 19 , CLK_L_VI = 0x1 << 20 , CLK_L_2D = 0x1 << 21 , CLK_L_USBD = 0x1 << 22 , CLK_L_ISP = 0x1 << 23 , CLK_L_3D = 0x1 << 24 , CLK_L_DISP2 = 0x1 << 26 , CLK_L_DISP1 = 0x1 << 27 , CLK_L_HOST1X = 0x1 << 28 , CLK_L_VCP = 0x1 << 29 , CLK_L_I2S0 = 0x1 << 30 , CLK_L_CACHE2 = 0x1 << 31 , CLK_H_MEM = 0x1 << 0 , CLK_H_AHBDMA = 0x1 << 1 , CLK_H_APBDMA = 0x1 << 2 , CLK_H_KBC = 0x1 << 4 , CLK_H_STAT_MON = 0x1 << 5 , CLK_H_PMC = 0x1 << 6 , CLK_H_FUSE = 0x1 << 7 , CLK_H_KFUSE = 0x1 << 8 , CLK_H_SBC1 = 0x1 << 9 , CLK_H_SNOR = 0x1 << 10 , CLK_H_JTAG2TBC = 0x1 << 11 , CLK_H_SBC2 = 0x1 << 12 , CLK_H_SBC3 = 0x1 << 14 , CLK_H_I2C5 = 0x1 << 15 , CLK_H_DSI = 0x1 << 16 , CLK_H_HSI = 0x1 << 18 , CLK_H_HDMI = 0x1 << 19 , CLK_H_CSI = 0x1 << 20 , CLK_H_I2C2 = 0x1 << 22 , CLK_H_UARTC = 0x1 << 23 , CLK_H_MIPI_CAL = 0x1 << 24 , CLK_H_EMC = 0x1 << 25 , CLK_H_USB2 = 0x1 << 26 , CLK_H_USB3 = 0x1 << 27 , CLK_H_MPE = 0x1 << 28 , CLK_H_VDE = 0x1 << 29 , CLK_H_BSEA = 0x1 << 30 , CLK_H_BSEV = 0x1 << 31 , CLK_U_UARTD = 0x1 << 1 , CLK_U_UARTE = 0x1 << 2 , CLK_U_I2C3 = 0x1 << 3 , CLK_U_SBC4 = 0x1 << 4 , CLK_U_SDMMC3 = 0x1 << 5 , CLK_U_PCIE = 0x1 << 6 , CLK_U_OWR = 0x1 << 7 , CLK_U_AFI = 0x1 << 8 , CLK_U_CSITE = 0x1 << 9 , CLK_U_PCIEXCLK = 0x1 << 10 , CLK_U_AVPUCQ = 0x1 << 11 , CLK_U_TRACECLKIN = 0x1 << 13 , CLK_U_SOC_THERM = 0x1 << 14 , CLK_U_DTV = 0x1 << 15 , CLK_U_NAND_SPEED = 0x1 << 16 , CLK_U_I2C_SLOW = 0x1 << 17 , CLK_U_DSIB = 0x1 << 18 , CLK_U_TSEC = 0x1 << 19 , CLK_U_IRAMA = 0x1 << 20 , CLK_U_IRAMB = 0x1 << 21 , CLK_U_IRAMC = 0x1 << 22 , CLK_U_EMUCIF = 0x1 << 23 , CLK_U_IRAMD = 0x1 << 23 , CLK_U_CRAM2 = 0x2 << 24 , CLK_U_XUSB_HOST = 0x1 << 25 , CLK_U_MSENC = 0x1 << 27 , CLK_U_SUS_OUT = 0x1 << 28 , CLK_U_DEV2_OUT = 0x1 << 29 , CLK_U_DEV1_OUT = 0x1 << 30 , CLK_U_XUSB_DEV = 0x1 << 31 , CLK_V_CPUG = 0x1 << 0 , CLK_V_CPULP = 0x1 << 1 , CLK_V_3D2 = 0x1 << 2 , CLK_V_MSELECT = 0x1 << 3 , CLK_V_I2S3 = 0x1 << 5 , CLK_V_I2S4 = 0x1 << 6 , CLK_V_I2C4 = 0x1 << 7 , CLK_V_SBC5 = 0x1 << 8 , CLK_V_SBC6 = 0x1 << 9 , CLK_V_AUDIO = 0x1 << 10 , CLK_V_APBIF = 0x1 << 11 , CLK_V_DAM0 = 0x1 << 12 , CLK_V_DAM1 = 0x1 << 13 , CLK_V_DAM2 = 0x1 << 14 , CLK_V_HDA2CODEC_2X = 0x1 << 15 , CLK_V_ATOMICS = 0x1 << 16 , CLK_V_ACTMON = 0x1 << 23 , CLK_V_EXTPERIPH1 = 0x1 << 24 , CLK_V_SATA = 0x1 << 28 , CLK_V_HDA = 0x1 << 29 , CLK_W_HDA2HDMICODEC = 0x1 << 0 , CLK_W_SATACOLD = 0x1 << 1 , CLK_W_CEC = 0x1 << 8 , CLK_W_XUSB_PADCTL = 0x1 << 14 , CLK_W_ENTROPY = 0x1 << 21 , CLK_W_AMX0 = 0x1 << 25 , CLK_W_ADX0 = 0x1 << 26 , CLK_W_DVFS = 0x1 << 27 , CLK_W_XUSB_SS = 0x1 << 28 , CLK_W_MC1 = 0x1 << 30 , CLK_W_EMC1 = 0x1 << 31 , CLK_X_AFC0 = 0x1 << 31 , CLK_X_AFC1 = 0x1 << 30 , CLK_X_AFC2 = 0x1 << 29 , CLK_X_AFC3 = 0x1 << 28 , CLK_X_AFC4 = 0x1 << 27 , CLK_X_AFC5 = 0x1 << 26 , CLK_X_AMX1 = 0x1 << 25 , CLK_X_GPU = 0x1 << 24 , CLK_X_SOR0 = 0x1 << 22 , CLK_X_DPAUX = 0x1 << 21 , CLK_X_ADX1 = 0x1 << 20 , CLK_X_VIC = 0x1 << 18 , CLK_X_CLK72MHZ = 0x1 << 17 , CLK_X_HDMI_AUDIO = 0x1 << 16 , CLK_X_EMC_DLL = 0x1 << 14 , CLK_X_VIM2_CLK = 0x1 << 11 , CLK_X_I2C6 = 0x1 << 6 , CLK_X_CAM_MCLK2 = 0x1 << 5 , CLK_X_CAM_MCLK = 0x1 << 4 , CLK_X_SPARE = 0x1 << 0 } |

| enum | clock_source { PLLP = 0 , PLLC2 = 1 , PLLC = 2 , PLLD = 2 , PLLC3 = 3 , PLLA = 3 , PLLM = 4 , PLLD2 = 5 , CLK_M = 6 } |

Functions | |

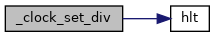

| static void | _clock_set_div (u32 *reg, const char *name, u32 div, u32 div_mask, u32 src) |

| int | clock_get_osc_khz (void) |

| int | clock_get_pll_input_khz (void) |

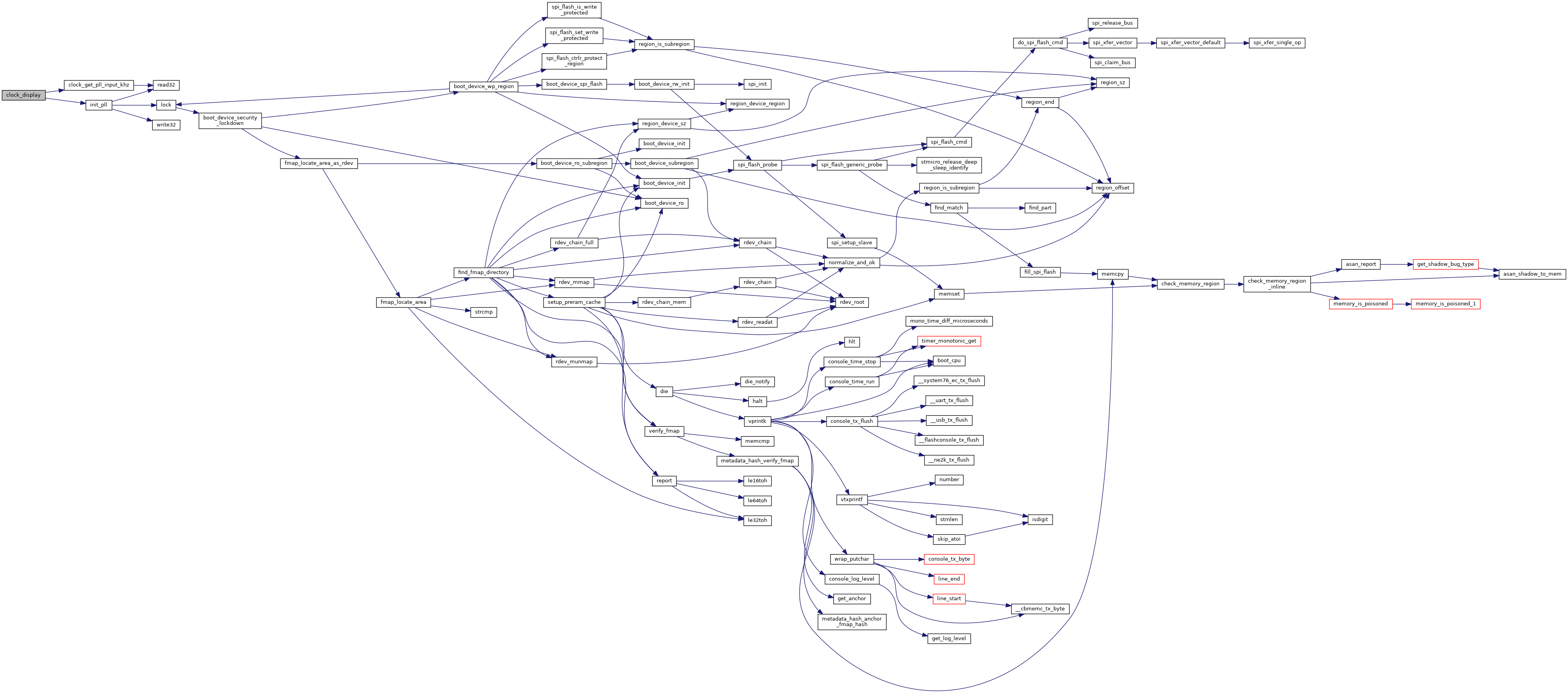

| u32 | clock_display (u32 frequency) |

| void | clock_early_uart (void) |

| void | clock_external_output (int clk_id) |

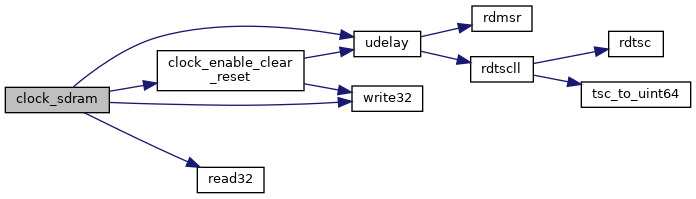

| void | clock_sdram (u32 m, u32 n, u32 p, u32 setup, u32 ph45, u32 ph90, u32 ph135, u32 kvco, u32 kcp, u32 stable_time, u32 emc_source, u32 same_freq) |

| void | clock_cpu0_config (void *entry) |

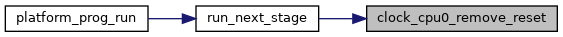

| void | clock_cpu0_remove_reset (void) |

| void | clock_halt_avp (void) |

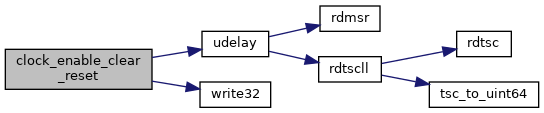

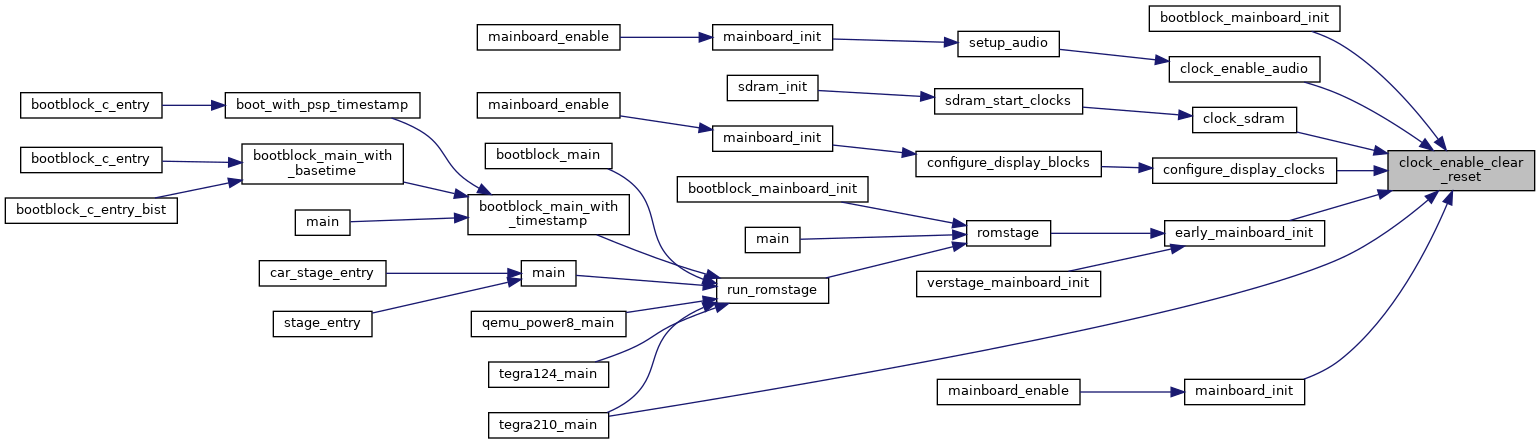

| void | clock_enable_clear_reset (u32 l, u32 h, u32 u, u32 v, u32 w, u32 x) |

| void | clock_reset_l (u32 l) |

| void | clock_reset_h (u32 h) |

| void | clock_reset_u (u32 u) |

| void | clock_reset_v (u32 v) |

| void | clock_reset_w (u32 w) |

| void | clock_reset_x (u32 x) |

| void | clock_init (void) |

| void | clock_init_arm_generic_timer (void) |

| void | sor_clock_stop (void) |

| void | sor_clock_start (void) |

| #define CLK_DIVIDER | ( | REF, | |

| FREQ | |||

| ) | (DIV_ROUND_UP(((REF) * 2), (FREQ)) - 2) |

| #define clock_configure_source | ( | device, | |

| src, | |||

| freq | |||

| ) | clock_configure_irregular_source(device, src, freq, src) |

| #define TEGRA_CLK_M_KHZ clock_get_osc_khz() |

| #define TEGRA_HCLK_KHZ (TEGRA_SCLK_KHZ / (1 + TEGRA_HCLK_RATIO)) |

| #define TEGRA_PCLK_KHZ (TEGRA_HCLK_KHZ / (1 + TEGRA_PCLK_RATIO)) |

| anonymous enum |

| enum clock_source |

|

inlinestatic |

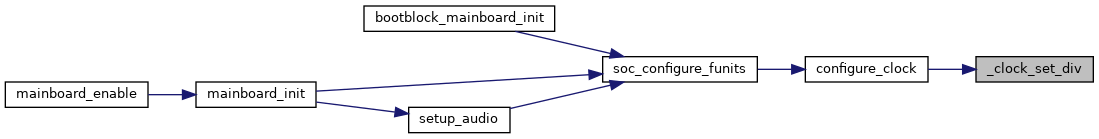

Definition at line 209 of file clock.h.

References BIOS_ERR, CLK_DIVISOR_MASK, CLK_SOURCE_MASK, CLK_SOURCE_SHIFT, clrsetbits32, hlt(), name, and printk.

Referenced by configure_clock().

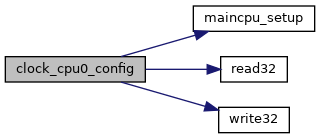

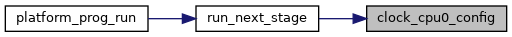

Definition at line 472 of file clock.c.

References clk_rst_ctlr::cclk_brst_pol, clk_rst_ctlr::clk_cpu_cmplx_clr, CLK_L_CPU, clk_rst_ctlr::clk_out_enb_l, clk_rst_ctlr::clk_out_enb_v, clk_rst, CLK_V_CPUG, CLK_V_CPULP, clrbits32, flow_ctlr::cluster_control, CRC_CCLK_BRST_POL_CPU_STATE_RUN, CRC_CCLK_BRST_POL_PLLX_OUT0, CRC_CLK_CLR_CPU0_STP, CRC_CLK_CLR_CPU1_STP, CRC_CLK_CLR_CPU2_STP, CRC_CLK_CLR_CPU3_STP, CRC_SUPER_CCLK_DIVIDER_SUPER_CDIV_ENB, flow, maincpu_entry_point, maincpu_setup(), maincpu_stack_pointer, read32(), setbits32, clk_rst_ctlr::super_cclk_div, TEGRA_EVP_BASE, and write32().

Referenced by run_next_stage().

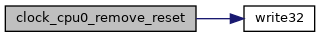

Definition at line 505 of file clock.c.

References clk_rst, CRC_RST_CPUG_CLR_CORE0, CRC_RST_CPUG_CLR_CORE1, CRC_RST_CPUG_CLR_CORE2, CRC_RST_CPUG_CLR_CORE3, CRC_RST_CPUG_CLR_CPU0, CRC_RST_CPUG_CLR_CPU1, CRC_RST_CPUG_CLR_CPU2, CRC_RST_CPUG_CLR_CPU3, CRC_RST_CPUG_CLR_CX0, CRC_RST_CPUG_CLR_CX1, CRC_RST_CPUG_CLR_CX2, CRC_RST_CPUG_CLR_CX3, CRC_RST_CPUG_CLR_DBG0, CRC_RST_CPUG_CLR_DBG1, CRC_RST_CPUG_CLR_DBG2, CRC_RST_CPUG_CLR_DBG3, CRC_RST_CPUG_CLR_L2, CRC_RST_CPUG_CLR_NONCPU, CRC_RST_CPUG_CLR_PDBG, CRC_RST_CPULP_CLR_CORE0, CRC_RST_CPULP_CLR_CPU0, CRC_RST_CPULP_CLR_CX0, CRC_RST_CPULP_CLR_DBG0, CRC_RST_CPULP_CLR_L2, CRC_RST_CPULP_CLR_NONCPU, CRC_RST_CPULP_CLR_PDBG, clk_rst_ctlr::rst_cpug_cmplx_clr, clk_rst_ctlr::rst_cpulp_cmplx_clr, and write32().

Referenced by run_next_stage().

plld (fo) = vco >> p, where 500MHz < vco < 1000MHz = (cf * n) >> p, where 1MHz < cf < 6MHz = ((ref / m) * n) >> p

Iterate the possible values of p (3 bits, 2^7) to find out a minimum safe vco, then find best (m, n). since m has only 5 bits, we can iterate all possible values. Note Tegra 124 supports 11 bits for n, but our pll_fields has only 10 bits for n.

Note values undershoot or overshoot target output frequency may not work if the values are not in "safe" range by panel specification.

Definition at line 294 of file clock.c.

References assert, BIOS_DEBUG, BIOS_ERR, BIOS_WARNING, clk_rst, clock_get_pll_input_khz(), pllpad_dividers::cpcon, init_pll(), pllpad_dividers::m, m, mhz, pllpad_dividers::n, pllpad_dividers::p, clk_rst_ctlr::plld_base, clk_rst_ctlr::plld_misc, PLLD_MISC_CLK_ENABLE, PLLUD_MISC_LOCK_ENABLE, and printk.

Referenced by display_startup().

Definition at line 600 of file clock.c.

References clk_rst_ctlr::clk_enb_h_set, clk_rst_ctlr::clk_enb_l_set, clk_rst_ctlr::clk_enb_u_set, clk_rst_ctlr::clk_enb_v_set, clk_rst_ctlr::clk_enb_w_set, clk_rst_ctlr::clk_enb_x_set, clk_rst, IO_STABILIZATION_DELAY, clk_rst_ctlr::rst_dev_h_clr, clk_rst_ctlr::rst_dev_l_clr, clk_rst_ctlr::rst_dev_u_clr, clk_rst_ctlr::rst_dev_v_clr, clk_rst_ctlr::rst_dev_w_clr, clk_rst_ctlr::rst_dev_x_clr, udelay(), write32(), and x.

Referenced by bootblock_mainboard_init(), clock_enable_audio(), clock_sdram(), configure_display_clocks(), early_mainboard_init(), mainboard_init(), and tegra210_main().

| void clock_sdram | ( | u32 | m, |

| u32 | n, | ||

| u32 | p, | ||

| u32 | setup, | ||

| u32 | ph45, | ||

| u32 | ph90, | ||

| u32 | ph135, | ||

| u32 | kvco, | ||

| u32 | kcp, | ||

| u32 | stable_time, | ||

| u32 | emc_source, | ||

| u32 | same_freq | ||

| ) |

Definition at line 416 of file clock.c.

References base, CLK_H_EMC, CLK_H_MEM, clk_rst, CLK_SOURCE_EMC_MC_EMC_SAME_FREQ, clk_rst_ctlr::clk_src_emc, clock_enable_clear_reset(), IO_STABILIZATION_DELAY, m, pllpad_dividers::n, pllpad_dividers::p, PLL_BASE_BYPASS, PLL_BASE_DIVM_SHIFT, PLL_BASE_DIVN_SHIFT, PLL_BASE_DIVP_SHIFT, PLL_BASE_ENABLE, PLL_BASE_LOCK, PLLCMX_BASE_DIVM_MASK, PLLCMX_BASE_DIVN_MASK, clk_rst_ctlr::pllm_base, PLLM_BASE_DIVP_MASK, clk_rst_ctlr::pllm_misc1, PLLM_MISC1_PD_LSHIFT_PH135_SHIFT, PLLM_MISC1_PD_LSHIFT_PH45_SHIFT, PLLM_MISC1_PD_LSHIFT_PH90_SHIFT, PLLM_MISC1_SETUP_SHIFT, clk_rst_ctlr::pllm_misc2, PLLM_MISC2_KCP_SHIFT, PLLM_MISC2_KVCO_SHIFT, clk_rst_ctlr::pllm_out, PLLM_OUT1_RSTN_RESET_DISABLE, read32(), setbits32, udelay(), and write32().

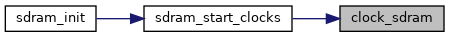

Referenced by sdram_start_clocks().