|

coreboot

coreboot is an Open Source project aimed at replacing the proprietary BIOS found in most computers.

|

|

coreboot

coreboot is an Open Source project aimed at replacing the proprietary BIOS found in most computers.

|

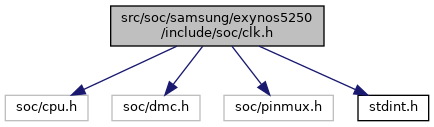

Go to the source code of this file.

Data Structures | |

| struct | clk_bit_info |

| struct | exynos5_clock |

| struct | exynos5_mct |

| struct | st_epll_con_val |

| struct | arm_clk_ratios |

Macros | |

| #define | APLL 0 |

| #define | MPLL 1 |

| #define | EPLL 2 |

| #define | HPLL 3 |

| #define | VPLL 4 |

| #define | BPLL 5 |

| #define | MCT_HZ 24000000 |

| #define | EXYNOS5_EPLLCON0_LOCKED_SHIFT 29 /* EPLL Locked bit position*/ |

| #define | EPLL_SRC_CLOCK 24000000 /*24 MHz Crystal Input */ |

| #define | TIMEOUT_EPLL_LOCK 1000 |

| #define | AUDIO_0_RATIO_MASK 0x0f |

| #define | AUDIO_1_RATIO_MASK 0x0f |

| #define | CLK_SRC_PERIC1 0x254 |

| #define | AUDIO1_SEL_MASK 0xf |

| #define | CLK_SRC_AUDIOCDCLK1 0x0 |

| #define | CLK_SRC_XXTI 0x1 |

| #define | CLK_SRC_SCLK_EPLL 0x7 |

| #define | EPLL_CON0_MDIV_MASK 0x1ff |

| #define | EPLL_CON0_PDIV_MASK 0x3f |

| #define | EPLL_CON0_SDIV_MASK 0x7 |

| #define | EPLL_CON0_LOCKED_SHIFT 29 |

| #define | EPLL_CON0_MDIV_SHIFT 16 |

| #define | EPLL_CON0_PDIV_SHIFT 8 |

| #define | EPLL_CON0_SDIV_SHIFT 0 |

| #define | EPLL_CON0_LOCK_DET_EN_SHIFT 28 |

| #define | EPLL_CON0_LOCK_DET_EN_MASK 1 |

Enumerations | |

| enum | pll_src_bit { SRC_MPLL = 6 , SRC_EPLL , SRC_VPLL } |

Functions | |

| unsigned long | get_pll_clk (int pllreg) |

| unsigned long | get_arm_clk (void) |

| unsigned long | get_pwm_clk (void) |

| unsigned long | get_uart_clk (int dev_index) |

| void | set_mmc_clk (int dev_index, unsigned int div) |

| unsigned long | clock_get_periph_rate (enum periph_id peripheral) |

| get the clk frequency of the required peripheral More... | |

| int | clock_set_mshci (enum periph_id peripheral) |

| int | clock_epll_set_rate (unsigned long rate) |

| void | clock_select_i2s_clk_source (void) |

| int | clock_set_i2s_clk_prescaler (unsigned int src_frq, unsigned int dst_frq) |

| check_member (exynos5_clock, pll_div2_sel, 0x20a24) | |

| check_member (exynos5_mct, l1_wstat, 0x440) | |

| void | clock_ll_set_pre_ratio (enum periph_id periph_id, unsigned int divisor) |

| Low-level function to set the clock pre-ratio for a peripheral. More... | |

| void | clock_ll_set_ratio (enum periph_id periph_id, unsigned int divisor) |

| Low-level function to set the clock ratio for a peripheral. More... | |

| int | clock_set_rate (enum periph_id periph_id, unsigned int rate) |

| Low-level function that selects the best clock scalars for a given rate and sets up the given peripheral's clock accordingly. More... | |

| void | clock_gate (void) |

| struct arm_clk_ratios * | get_arm_clk_ratios (void) |

| Get the clock ratios for CPU configuration. More... | |

| void | system_clock_init (struct mem_timings *mem, struct arm_clk_ratios *arm_clk_ratio) |

Variables | |

| static struct exynos5_clock *const | exynos_clock = (void *)EXYNOS5_CLOCK_BASE |

| static struct exynos5_mct *const | exynos_mct |

| #define EXYNOS5_EPLLCON0_LOCKED_SHIFT 29 /* EPLL Locked bit position*/ |

| enum pll_src_bit |

| check_member | ( | exynos5_clock | , |

| pll_div2_sel | , | ||

| 0x20a24 | |||

| ) |

| check_member | ( | exynos5_mct | , |

| l1_wstat | , | ||

| 0x440 | |||

| ) |

Definition at line 267 of file clock_init.c.

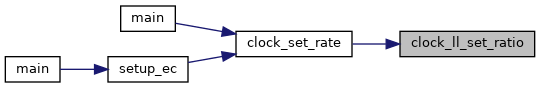

Low-level function to set the clock pre-ratio for a peripheral.

| periph_id | Peripheral ID of peripheral to change |

| divisor | New divisor for this peripheral's clock |

Definition at line 374 of file clock.c.

References BIOS_DEBUG, clrsetbits32, exynos5_clock::div_peric1, exynos5_clock::div_peric2, exynos_clock, mask, PERIPH_ID_SPI0, PERIPH_ID_SPI1, PERIPH_ID_SPI2, PERIPH_ID_SPI3, PERIPH_ID_SPI4, printk, and exynos5_clock::sclk_div_isp.

Referenced by clock_set_rate().

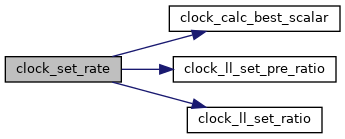

Low-level function to set the clock ratio for a peripheral.

| periph_id | Peripheral ID of peripheral to change |

| divisor | New divisor for this peripheral's clock |

Definition at line 417 of file clock.c.

References BIOS_DEBUG, clrsetbits32, exynos5_clock::div_peric1, exynos5_clock::div_peric2, exynos_clock, mask, PERIPH_ID_SPI0, PERIPH_ID_SPI1, PERIPH_ID_SPI2, PERIPH_ID_SPI3, PERIPH_ID_SPI4, printk, and exynos5_clock::sclk_div_isp.

Referenced by clock_set_rate().

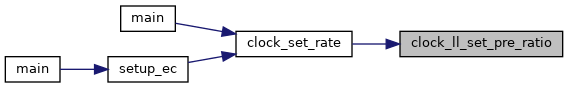

Low-level function that selects the best clock scalars for a given rate and sets up the given peripheral's clock accordingly.

| periph_id | Peripheral ID of peripheral to change |

| rate | Desired clock rate in Hz |

Definition at line 511 of file clock.c.

References BIOS_DEBUG, clock_calc_best_scalar(), clock_ll_set_pre_ratio(), clock_ll_set_ratio(), PERIPH_ID_SPI0, PERIPH_ID_SPI1, PERIPH_ID_SPI2, PERIPH_ID_SPI3, PERIPH_ID_SPI4, and printk.

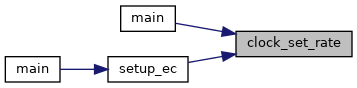

Referenced by main(), and setup_ec().

| struct arm_clk_ratios* get_arm_clk_ratios | ( | void | ) |

| unsigned long get_uart_clk | ( | int | dev_index | ) |

| void system_clock_init | ( | struct mem_timings * | mem, |

| struct arm_clk_ratios * | arm_clk_ratio | ||

| ) |

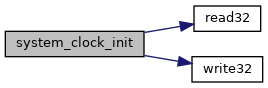

Definition at line 10 of file clock_init.c.

References arm_clk_ratios::acp_ratio, exynos5_clock::apll_con0, APLL_CON0_LOCKED, exynos5_clock::apll_con1, APLL_CON1_VAL, APLL_FOUT, exynos5_clock::apll_lock, APLL_LOCK_VAL, arm_clk_ratios::apll_mdiv, arm_clk_ratios::apll_pdiv, arm_clk_ratios::apll_ratio, arm_clk_ratios::apll_sdiv, arm_clk_ratios::arm2_ratio, arm_clk_ratios::arm_ratio, arm_clk_ratios::atb_ratio, exynos5_clock::bpll_con0, BPLL_CON0_LOCKED, exynos5_clock::bpll_con1, BPLL_CON1_VAL, exynos5_clock::bpll_lock, BPLL_LOCK_VAL, mem_timings::bpll_mdiv, mem_timings::bpll_pdiv, mem_timings::bpll_sdiv, CLK_DIV_ACP_VAL, CLK_DIV_CDREX_VAL, CLK_DIV_CORE0_VAL, CLK_DIV_CORE1_VAL, CLK_DIV_CPU1_VAL, CLK_DIV_FSYS0_VAL, CLK_DIV_ISP0_VAL, CLK_DIV_ISP1_VAL, CLK_DIV_ISP2_VAL, CLK_DIV_LEX_VAL, CLK_DIV_PERIC0_VAL, CLK_DIV_PERIC1_VAL, CLK_DIV_PERIC2_VAL, CLK_DIV_R0X_VAL, CLK_DIV_R1X_VAL, CLK_DIV_SYSLFT_VAL, CLK_DIV_SYSRGT_VAL, CLK_DIV_TOP0_VAL, CLK_DIV_TOP1_VAL, CLK_REG_DISABLE, CLK_SRC_CORE0_VAL, CLK_SRC_CORE1_VAL, CLK_SRC_CPU_VAL, CLK_SRC_DISP1_0_VAL, CLK_SRC_FSYS0_VAL, CLK_SRC_LEX_VAL, CLK_SRC_PERIC0_VAL, CLK_SRC_PERIC1_VAL, CLK_SRC_TOP0_VAL, CLK_SRC_TOP1_VAL, CLK_SRC_TOP2_VAL, CLK_SRC_TOP3_VAL, exynos5_clock::clkout_cmu_acp, exynos5_clock::clkout_cmu_cdrex, exynos5_clock::clkout_cmu_core, exynos5_clock::clkout_cmu_cpu, exynos5_clock::clkout_cmu_lex, exynos5_clock::clkout_cmu_r0x, exynos5_clock::clkout_cmu_r1x, exynos5_clock::clkout_cmu_top, clrbits32, exynos5_clock::cpll_con0, CPLL_CON0_LOCKED, exynos5_clock::cpll_con1, CPLL_CON1_VAL, exynos5_clock::cpll_lock, CPLL_LOCK_VAL, mem_timings::cpll_mdiv, mem_timings::cpll_pdiv, mem_timings::cpll_sdiv, arm_clk_ratios::cpud_ratio, exynos5_clock::div_acp, exynos5_clock::div_cdrex, exynos5_clock::div_core0, exynos5_clock::div_core1, exynos5_clock::div_cpu0, exynos5_clock::div_cpu1, exynos5_clock::div_fsys0, exynos5_clock::div_fsys2, exynos5_clock::div_isp0, exynos5_clock::div_isp1, exynos5_clock::div_isp2, exynos5_clock::div_lex, exynos5_clock::div_peric0, exynos5_clock::div_peric1, exynos5_clock::div_peric2, exynos5_clock::div_r0x, exynos5_clock::div_r1x, exynos5_clock::div_stat_acp, exynos5_clock::div_stat_cdrex, exynos5_clock::div_stat_core0, exynos5_clock::div_stat_core1, exynos5_clock::div_stat_cpu0, exynos5_clock::div_stat_cpu1, exynos5_clock::div_stat_fsys0, exynos5_clock::div_stat_lex, exynos5_clock::div_stat_r0x, exynos5_clock::div_stat_r1x, exynos5_clock::div_stat_syslft, exynos5_clock::div_stat_sysrgt, exynos5_clock::div_stat_top0, exynos5_clock::div_stat_top1, exynos5_clock::div_syslft, exynos5_clock::div_sysrgt, exynos5_clock::div_top0, exynos5_clock::div_top1, exynos5_clock::epll_con0, EPLL_CON0_LOCKED, exynos5_clock::epll_con1, EPLL_CON1_VAL, exynos5_clock::epll_con2, EPLL_CON2_VAL, exynos5_clock::epll_lock, EPLL_LOCK_VAL, mem_timings::epll_mdiv, mem_timings::epll_pdiv, mem_timings::epll_sdiv, exynos_clock, exynos_mct, exynos5_mct::g_tcon, exynos5_clock::gpll_con0, GPLL_CON0_LOCKED, exynos5_clock::gpll_con1, GPLL_CON1_VAL, exynos5_clock::gpll_lock, GPLL_LOCK_VAL, mem_timings::gpll_mdiv, mem_timings::gpll_pdiv, mem_timings::gpll_sdiv, HPM_SEL_SCLK_MPLL, MMC2_PRE_RATIO_OFFSET, MMC2_PRE_RATIO_VAL, MMC2_RATIO_OFFSET, MMC2_RATIO_VAL, MMC3_PRE_RATIO_OFFSET, MMC3_PRE_RATIO_VAL, MMC3_RATIO_OFFSET, MMC3_RATIO_VAL, exynos5_clock::mpll_con0, MPLL_CON0_LOCKED, exynos5_clock::mpll_con1, MPLL_CON1_VAL, exynos5_clock::mpll_lock, MPLL_LOCK_VAL, mem_timings::mpll_mdiv, mem_timings::mpll_pdiv, mem_timings::mpll_sdiv, MUX_APLL_SEL_MASK, MUX_BPLL_FOUT_SEL, MUX_BPLL_SEL_MASK, MUX_CPLL_SEL_MASK, MUX_EPLL_SEL_MASK, MUX_GPLL_SEL_MASK, MUX_HPM_SEL_MASK, MUX_MCLK_CDREX_SEL, MUX_MCLK_DPHY_SEL, MUX_MPLL_FOUT_SEL, MUX_MPLL_SEL_MASK, exynos5_clock::mux_stat_cdrex, exynos5_clock::mux_stat_core1, exynos5_clock::mux_stat_cpu, exynos5_clock::mux_stat_lex, exynos5_clock::mux_stat_top2, MUX_VPLL_SEL_MASK, arm_clk_ratios::pclk_dbg_ratio, arm_clk_ratios::periph_ratio, exynos5_clock::pll_div2_sel, read32(), exynos5_clock::sclk_div_isp, SCLK_DIV_ISP_VAL, exynos5_clock::sclk_src_isp, SCLK_SRC_ISP_VAL, set_pll, setbits32, exynos5_clock::src_cdrex, exynos5_clock::src_core0, exynos5_clock::src_core1, exynos5_clock::src_cpu, exynos5_clock::src_disp1_0, exynos5_clock::src_fsys, exynos5_clock::src_lex, exynos5_clock::src_peric0, exynos5_clock::src_peric1, exynos5_clock::src_top0, exynos5_clock::src_top1, exynos5_clock::src_top2, exynos5_clock::src_top3, TOP2_VAL, mem_timings::use_bpll, val, exynos5_clock::vpll_con0, VPLL_CON0_LOCKED, exynos5_clock::vpll_con1, VPLL_CON1_VAL, exynos5_clock::vpll_con2, VPLL_CON2_VAL, exynos5_clock::vpll_lock, VPLL_LOCK_VAL, mem_timings::vpll_mdiv, mem_timings::vpll_pdiv, mem_timings::vpll_sdiv, and write32().

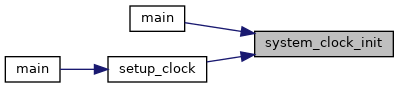

Referenced by main(), and setup_clock().

|

static |

Definition at line 446 of file clk.h.

Referenced by clock_epll_set_rate(), clock_gate(), clock_get_periph_rate(), clock_init_dp_clock(), clock_ll_set_pre_ratio(), clock_ll_set_ratio(), clock_select_i2s_clk_source(), clock_set_i2s_clk_prescaler(), clock_set_mshci(), ddr3_mem_ctrl_init(), get_arm_clk(), get_lcd_clk(), get_mmc_clk(), get_pll_clk(), reset_phy_ctrl(), set_mmc_clk(), and system_clock_init().

|

static |

Definition at line 507 of file clk.h.

Referenced by init_timer(), mct_raw_value(), and system_clock_init().