|

coreboot

coreboot is an Open Source project aimed at replacing the proprietary BIOS found in most computers.

|

|

coreboot

coreboot is an Open Source project aimed at replacing the proprietary BIOS found in most computers.

|

Go to the source code of this file.

Data Structures | |

| struct | elf_se_hdr |

| struct | gsi_fw_hdr |

| struct | gsi_fw_iram |

| struct | gsi_fw_iep |

| struct | qupv3_common_reg |

Functions | |

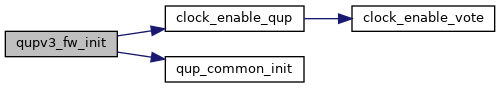

| void | qupv3_fw_init (void) |

| void | qupv3_se_fw_load_and_init (unsigned int bus, unsigned int protocol, unsigned int mode) |

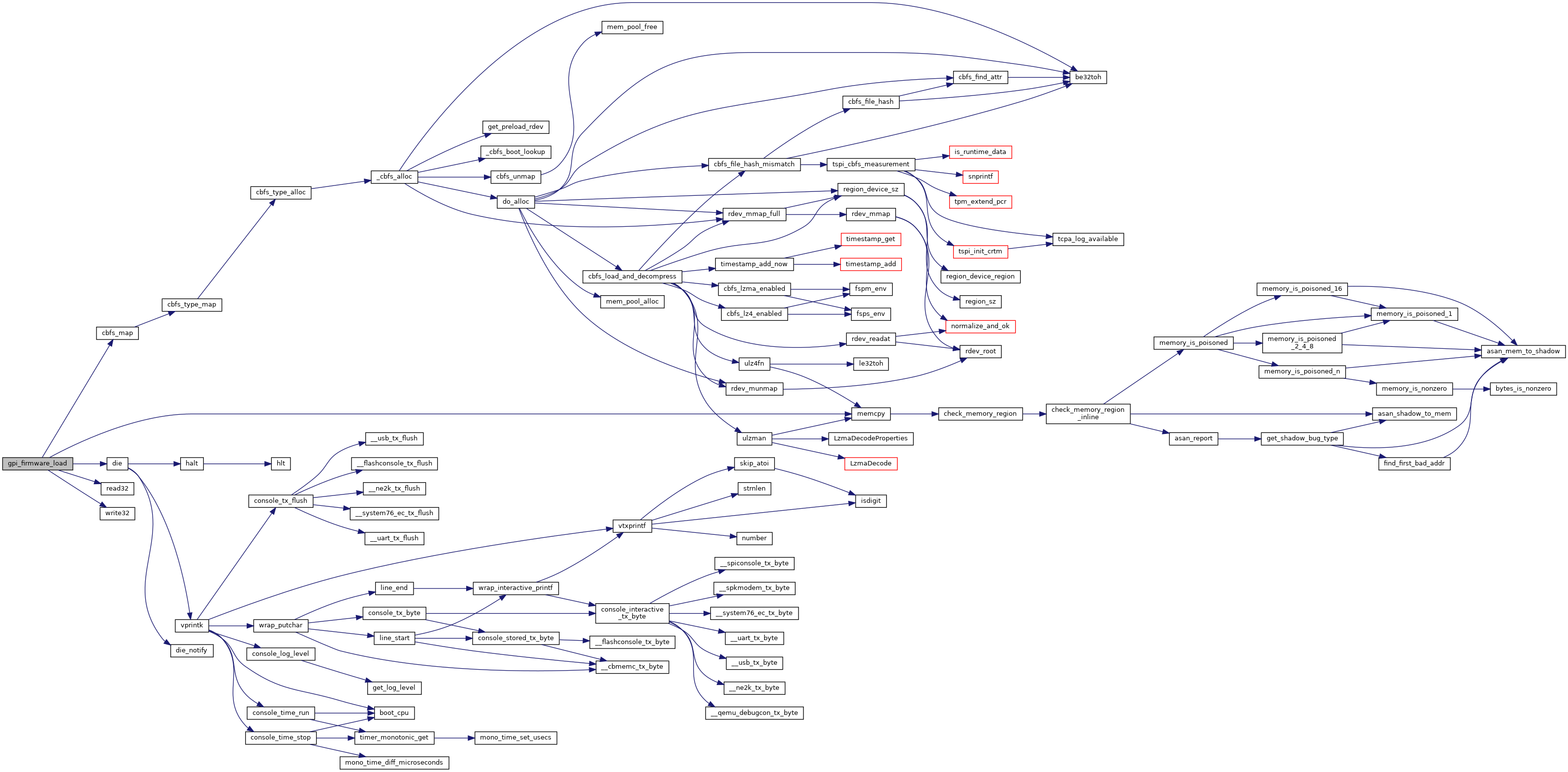

| void | gpi_firmware_load (int addr) |

| #define DMA_GENERAL_CFG_AHB_SEC_SLV_CLK_CGC_ON_BMSK 0x00000008 |

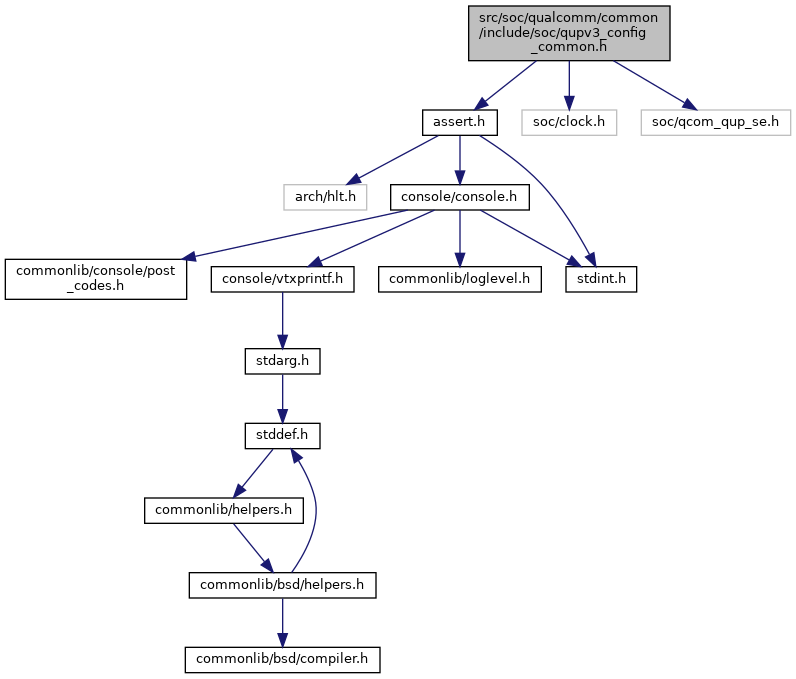

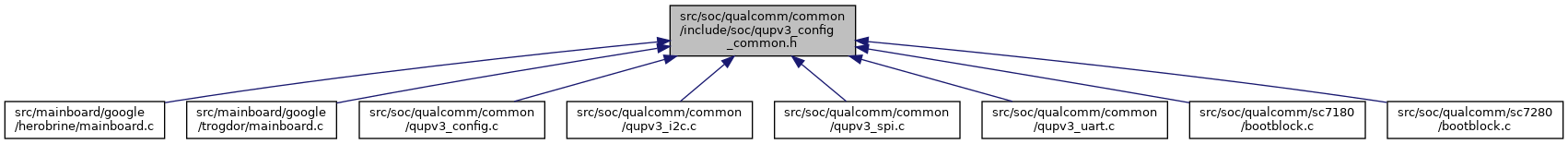

Definition at line 27 of file qupv3_config_common.h.

| #define DMA_GENERAL_CFG_DMA_AHB_SLV_CLK_CGC_ON_BMSK 0x00000004 |

Definition at line 28 of file qupv3_config_common.h.

| #define DMA_GENERAL_CFG_DMA_RX_CLK_CGC_ON_BMSK 0x00000001 |

Definition at line 30 of file qupv3_config_common.h.

| #define DMA_GENERAL_CFG_DMA_TX_CLK_CGC_ON_BMSK 0x00000002 |

Definition at line 29 of file qupv3_config_common.h.

| #define DMA_IF_EN_DMA_IF_EN_BMSK 0x00000001 |

Definition at line 33 of file qupv3_config_common.h.

| #define DMA_RX_IRQ_EN_SET_DMA_DONE_EN_SET_BMSK 0x00000001 |

Definition at line 25 of file qupv3_config_common.h.

| #define DMA_RX_IRQ_EN_SET_FLUSH_DONE_EN_SET_BMSK 0x00000010 |

Definition at line 22 of file qupv3_config_common.h.

| #define DMA_RX_IRQ_EN_SET_RESET_DONE_EN_SET_BMSK 0x00000008 |

Definition at line 23 of file qupv3_config_common.h.

| #define DMA_RX_IRQ_EN_SET_SBE_EN_SET_BMSK 0x00000004 |

Definition at line 24 of file qupv3_config_common.h.

| #define DMA_TX_IRQ_EN_SET_DMA_DONE_EN_SET_BMSK 0x00000001 |

Definition at line 20 of file qupv3_config_common.h.

| #define DMA_TX_IRQ_EN_SET_RESET_DONE_EN_SET_BMSK 0x00000008 |

Definition at line 18 of file qupv3_config_common.h.

| #define DMA_TX_IRQ_EN_SET_SBE_EN_SET_BMSK 0x00000004 |

Definition at line 19 of file qupv3_config_common.h.

| #define GENI_CGC_CTRL_PROG_RAM_HCLK_OFF_BMSK 0x00000100 |

Definition at line 14 of file qupv3_config_common.h.

| #define GENI_CGC_CTRL_PROG_RAM_SCLK_OFF_BMSK 0x00000200 |

Definition at line 13 of file qupv3_config_common.h.

| #define GENI_CLK_CTRL_SER_CLK_SEL_BMSK 0x00000001 |

Definition at line 32 of file qupv3_config_common.h.

| #define GENI_DMA_MODE_EN_GENI_DMA_MODE_EN_BMSK 0x00000001 |

Definition at line 16 of file qupv3_config_common.h.

| #define GSI_CFG_DOUBLE_MCS_CLK_FREQ_BMSK 0x4 |

Definition at line 45 of file qupv3_config_common.h.

| #define GSI_CFG_GSI_ENABLE_BMSK 0x1 |

Definition at line 46 of file qupv3_config_common.h.

| #define GSI_CGC_CTRL_REGION_2_HW_CGC_EN_BMSK 0x2 |

Definition at line 47 of file qupv3_config_common.h.

| #define GSI_FW_BYTES_PER_LINE 8 |

Definition at line 43 of file qupv3_config_common.h.

| #define GSI_FW_MAGIC_HEADER 0x20495351 |

Definition at line 40 of file qupv3_config_common.h.

| #define GSI_INST_RAM_n_MAX_n 4095 |

Definition at line 42 of file qupv3_config_common.h.

| #define GSI_MCS_CFG_MCS_ENABLE_BMSK 0x1 |

Definition at line 44 of file qupv3_config_common.h.

| #define GSI_REG_BASE_SIZE 0x5000 |

Definition at line 41 of file qupv3_config_common.h.

| #define QUPV3_COMMON_CFG_FAST_SWITCH_TO_HIGH_DISABLE_BMSK 0x00000001 |

Definition at line 10 of file qupv3_config_common.h.

| #define QUPV3_SE_AHB_M_CFG_AHB_M_CLK_CGC_ON_BMSK 0x00000001 |

Definition at line 11 of file qupv3_config_common.h.

| #define SE_GSI_EVENT_EN_BMSK 0x0000000f |

Definition at line 34 of file qupv3_config_common.h.

| #define SE_IRQ_EN_RMSK 0x0000000f |

Definition at line 35 of file qupv3_config_common.h.

| #define SEFW_MAGIC_HEADER 0x57464553 |

Definition at line 38 of file qupv3_config_common.h.

| #define SIZE_GENI_FW_RAM 0x00000200 |

Definition at line 37 of file qupv3_config_common.h.

| void gpi_firmware_load | ( | int | addr | ) |

Definition at line 184 of file qupv3_config.c.

References addr, assert, cbfs_map(), clrbits_le32, die(), gsi_fw_hdr::fw_offset, gsi_fw_hdr::fw_size_in_items, GSI_CFG_DOUBLE_MCS_CLK_FREQ_BMSK, GSI_CFG_GSI_ENABLE_BMSK, GSI_CGC_CTRL_REGION_2_HW_CGC_EN_BMSK, GSI_FW_BYTES_PER_LINE, GSI_FW_MAGIC_HEADER, GSI_INST_RAM_n_MAX_n, GSI_MCS_CFG_MCS_ENABLE_BMSK, GSI_REG_BASE_SIZE, gsi_fw_hdr::iep_offset, gsi_fw_hdr::iep_size_in_items, gsi_fw_iram::iram_dword0, gsi_fw_hdr::magic, memcpy(), NULL, offset, gsi_fw_iep::offset, read32(), setbits_le32, gsi_fw_iep::value, and write32().

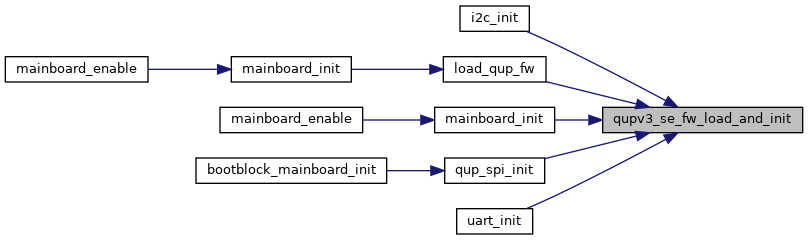

Referenced by mainboard_init().

Definition at line 253 of file qupv3_config.c.

References clock_enable_qup(), qup_common_init(), QUP_WRAP0_BASE, QUP_WRAP1_BASE, and QUPV3_SE_MAX.

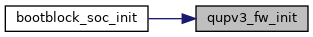

Referenced by bootblock_soc_init().

Definition at line 13 of file qupv3_config.c.

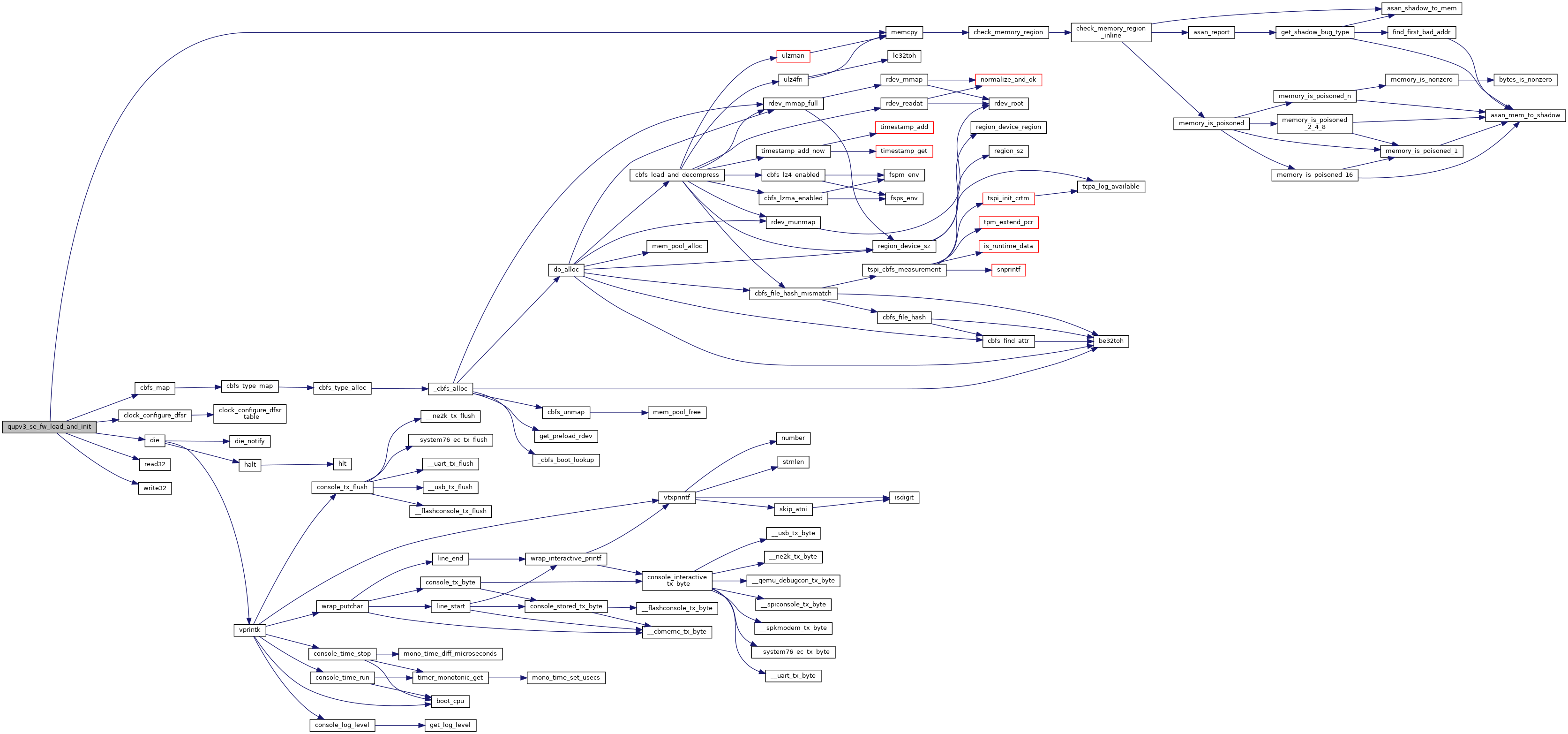

References assert, cbfs_map(), elf_se_hdr::cfg_idx_offset, elf_se_hdr::cfg_size_in_items, elf_se_hdr::cfg_val_offset, elf_se_hdr::cfg_version, clock_configure_dfsr(), clrbits_le32, CPU_DMA, DEFAULT_CGC_EN, DEFAULT_IO_OUTPUT_CTRL_MSK, die(), DMA_GENERAL_CFG_AHB_SEC_SLV_CLK_CGC_ON_BMSK, DMA_GENERAL_CFG_DMA_AHB_SLV_CLK_CGC_ON_BMSK, DMA_GENERAL_CFG_DMA_RX_CLK_CGC_ON_BMSK, DMA_GENERAL_CFG_DMA_TX_CLK_CGC_ON_BMSK, DMA_IF_EN_DMA_IF_EN_BMSK, DMA_RX_IRQ_EN_SET_DMA_DONE_EN_SET_BMSK, DMA_RX_IRQ_EN_SET_FLUSH_DONE_EN_SET_BMSK, DMA_RX_IRQ_EN_SET_RESET_DONE_EN_SET_BMSK, DMA_RX_IRQ_EN_SET_SBE_EN_SET_BMSK, DMA_TX_IRQ_EN_SET_DMA_DONE_EN_SET_BMSK, DMA_TX_IRQ_EN_SET_RESET_DONE_EN_SET_BMSK, DMA_TX_IRQ_EN_SET_SBE_EN_SET_BMSK, FIFO, FIFO_DEPTH, FIFO_IF_DISABLE, fw_list, elf_se_hdr::fw_offset, FW_REV_PROTOCOL_SHFT, FW_REV_VERSION_SHFT, elf_se_hdr::fw_size_in_items, elf_se_hdr::fw_version, GENI_CGC_CTRL_PROG_RAM_HCLK_OFF_BMSK, GENI_CGC_CTRL_PROG_RAM_SCLK_OFF_BMSK, GENI_CLK_CTRL_SER_CLK_SEL_BMSK, GENI_DFS_IF_CFG_DFS_IF_EN_BMSK, GENI_DMA_MODE_EN_GENI_DMA_MODE_EN_BMSK, GSI, M_COMMON_GENI_M_IRQ_EN, elf_se_hdr::magic, MAX_OFFSET_CFG_REG, memcpy(), MIXED, NULL, read32(), qup::regs, S_CMD_ABORT_EN, S_CMD_CANCEL_EN, S_CMD_OVERRUN_EN, S_GP_IRQ_0_EN, S_GP_IRQ_1_EN, S_GP_IRQ_2_EN, S_GP_IRQ_3_EN, S_ILLEGAL_CMD_EN, S_RX_FIFO_RD_ERR_EN, S_RX_FIFO_WR_ERR_EN, SE_GSI_EVENT_EN_BMSK, SE_IRQ_EN_RMSK, SE_PROTOCOL_I2C, SE_PROTOCOL_MAX, SE_PROTOCOL_SPI, SE_PROTOCOL_UART, SEFW_MAGIC_HEADER, elf_se_hdr::serial_protocol, setbits_le32, SIZE_GENI_FW_RAM, and write32().

Referenced by i2c_init(), load_qup_fw(), mainboard_init(), qup_spi_init(), and uart_init().