|

coreboot

coreboot is an Open Source project aimed at replacing the proprietary BIOS found in most computers.

|

|

coreboot

coreboot is an Open Source project aimed at replacing the proprietary BIOS found in most computers.

|

#include <path.h>

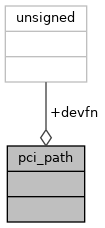

Data Fields | |

| unsigned int | devfn |

| unsigned int pci_path::devfn |

Definition at line 54 of file path.h.

Referenced by acpi_create_ipmi(), acpigen_write_ADR_pci_device(), acpigen_write_pci_FCH_PRT(), acpigen_write_pci_GNB_PRT(), add_ivhd_dev_entry(), add_ivhd_device_entries(), all_ports_no_dev_present(), amdfam14_nodeid(), amdfam15_nodeid(), amdfam16_nodeid(), attach_iio_stacks(), broadwell_pch_enable_dev(), camera_fill_ssdt(), dev_ctl_reg(), dev_find_slot(), dev_path(), dev_path_encode(), disable_dev(), dnv_get_int_line(), dw_i2c_soc_dev_to_bus(), ecam0_fix_missing_devices(), ecam0_init(), enable_dev(), get_pci_irq_pins(), handleInt1a(), hide_pci_fn(), hudson_enable(), i2c_disable_resets(), i82801dx_enable(), i82801gx_enable(), ich_pcie_device_set_func(), int1a_handler(), intel_acpi_gen_def_acpi_pirq(), is_part_of_group(), lpc_acpi_name(), northbridge_acpi_name(), path_eq(), pch_disable_devfn(), pch_enable(), pch_pcie_acpi_name(), pch_pcie_check_set_enabled(), pch_pcie_device_set_func(), pch_pcie_devicetree_update(), pch_pcie_enable(), pch_pcie_pm_early(), pch_pcie_pm_late(), pch_pirq_init(), pci_init(), pci_match_simple_dev(), pci_probe_dev(), pci_scan_get_dev(), pcidev_bdf(), pcie_gpp_acpi_name(), pcie_rp_update_dev(), pcie_update_device_tree(), pciexp_config_L1_sub_state(), pciexp_L1_substate_commit(), pciexp_scan_bus(), place_device_in_d3hot(), rl5c476_init(), rl5c476_read_resources(), rl5c476_set_resources(), root_port_is_first(), root_port_is_last(), root_port_mark_disable(), root_port_number(), root_port_offset(), run_bios(), sb800_enable(), sc_disable_devfn(), serialio_init(), serialio_uart_is_debug(), set_usb_over_current(), smbios_generate_type41_from_devtree(), smbios_generate_type9_from_devtree(), smp_write_intsrc_pci_bridge(), soc_enable(), soc_get_cpu_rp_vw_idx(), swizzle_irq_pins(), write_pci_cfg_irqs(), write_pci_config_irqs(), write_smp_table(), and xeonsp_pci_domain_scan_bus().