|

coreboot

coreboot is an Open Source project aimed at replacing the proprietary BIOS found in most computers.

|

|

coreboot

coreboot is an Open Source project aimed at replacing the proprietary BIOS found in most computers.

|

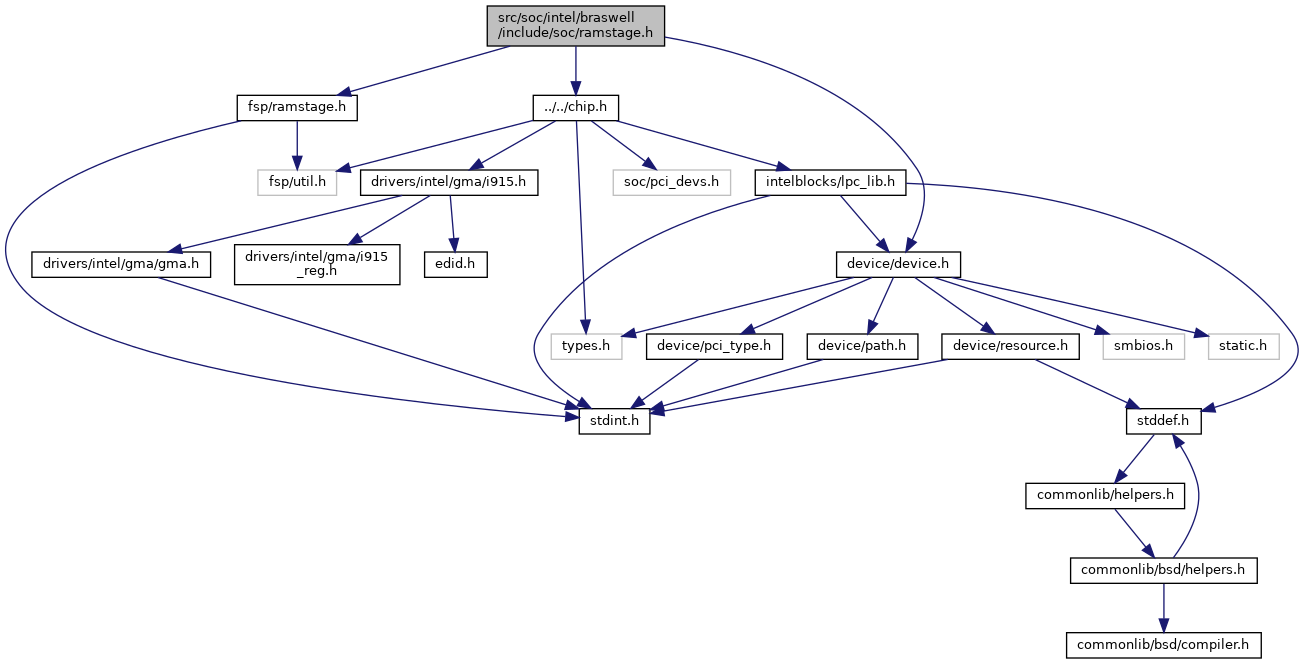

Go to the source code of this file.

Enumerations | |

| enum | { SocA0 = 0 , SocA1 = 1 , SocA2 = 2 , SocA3 = 3 , SocA4 = 4 , SocA5 = 5 , SocA6 = 6 , SocA7 = 7 , SocB0 = 8 , SocB1 = 9 , SocB2 = 10 , SocB3 = 11 , SocB4 = 12 , SocB5 = 13 , SocB6 = 14 , SocB7 = 15 , SocC0 = 16 , SocC1 = 17 , SocC2 = 18 , SocC3 = 19 , SocC4 = 20 , SocC5 = 21 , SocC6 = 22 , SocC7 = 23 , SocD0 = 24 , SocD1 = 25 , SocD2 = 26 , SocD3 = 27 , SocD4 = 28 , SocD5 = 29 , SocD6 = 30 , SocD7 = 31 , SocSteppingMax } |

Functions | |

| void | soc_init_pre_device (struct soc_intel_braswell_config *config) |

| void | southcluster_enable_dev (struct device *dev) |

| void | scc_enable_acpi_mode (struct device *dev, int iosf_reg, int nvs_index) |

| int | SocStepping (void) |

| Return SoC stepping type. More... | |

| void | board_silicon_USB2_override (SILICON_INIT_UPD *params) |

Variables | |

| struct pci_operations | soc_pci_ops |

| #define B_PCH_LPC_RID_STEPPING_MASK 0xFC |

Definition at line 43 of file ramstage.h.

| #define V_PCH_LPC_RID_A0 0x00 |

Definition at line 11 of file ramstage.h.

| #define V_PCH_LPC_RID_A1 0x04 |

Definition at line 12 of file ramstage.h.

| #define V_PCH_LPC_RID_A2 0x08 |

Definition at line 13 of file ramstage.h.

| #define V_PCH_LPC_RID_A3 0x0C |

Definition at line 14 of file ramstage.h.

| #define V_PCH_LPC_RID_A4 0x80 |

Definition at line 15 of file ramstage.h.

| #define V_PCH_LPC_RID_A5 0x84 |

Definition at line 16 of file ramstage.h.

| #define V_PCH_LPC_RID_A6 0x88 |

Definition at line 17 of file ramstage.h.

| #define V_PCH_LPC_RID_A7 0x8C |

Definition at line 18 of file ramstage.h.

| #define V_PCH_LPC_RID_B0 0x10 |

Definition at line 19 of file ramstage.h.

| #define V_PCH_LPC_RID_B1 0x14 |

Definition at line 20 of file ramstage.h.

| #define V_PCH_LPC_RID_B2 0x18 |

Definition at line 21 of file ramstage.h.

| #define V_PCH_LPC_RID_B3 0x1C |

Definition at line 22 of file ramstage.h.

| #define V_PCH_LPC_RID_B4 0x90 |

Definition at line 23 of file ramstage.h.

| #define V_PCH_LPC_RID_B5 0x94 |

Definition at line 24 of file ramstage.h.

| #define V_PCH_LPC_RID_B6 0x98 |

Definition at line 25 of file ramstage.h.

| #define V_PCH_LPC_RID_B7 0x9C |

Definition at line 26 of file ramstage.h.

| #define V_PCH_LPC_RID_C0 0x20 |

Definition at line 27 of file ramstage.h.

| #define V_PCH_LPC_RID_C1 0x24 |

Definition at line 28 of file ramstage.h.

| #define V_PCH_LPC_RID_C2 0x28 |

Definition at line 29 of file ramstage.h.

| #define V_PCH_LPC_RID_C3 0x2C |

Definition at line 30 of file ramstage.h.

| #define V_PCH_LPC_RID_C4 0xA0 |

Definition at line 31 of file ramstage.h.

| #define V_PCH_LPC_RID_C5 0xA4 |

Definition at line 32 of file ramstage.h.

| #define V_PCH_LPC_RID_C6 0xA8 |

Definition at line 33 of file ramstage.h.

| #define V_PCH_LPC_RID_C7 0xAC |

Definition at line 34 of file ramstage.h.

| #define V_PCH_LPC_RID_D0 0x30 |

Definition at line 35 of file ramstage.h.

| #define V_PCH_LPC_RID_D1 0x34 |

Definition at line 36 of file ramstage.h.

| #define V_PCH_LPC_RID_D2 0x38 |

Definition at line 37 of file ramstage.h.

| #define V_PCH_LPC_RID_D3 0x3C |

Definition at line 38 of file ramstage.h.

| #define V_PCH_LPC_RID_D4 0xB0 |

Definition at line 39 of file ramstage.h.

| #define V_PCH_LPC_RID_D5 0xB4 |

Definition at line 40 of file ramstage.h.

| #define V_PCH_LPC_RID_D6 0xB8 |

Definition at line 41 of file ramstage.h.

| #define V_PCH_LPC_RID_D7 0xBC |

Definition at line 42 of file ramstage.h.

| anonymous enum |

Definition at line 45 of file ramstage.h.

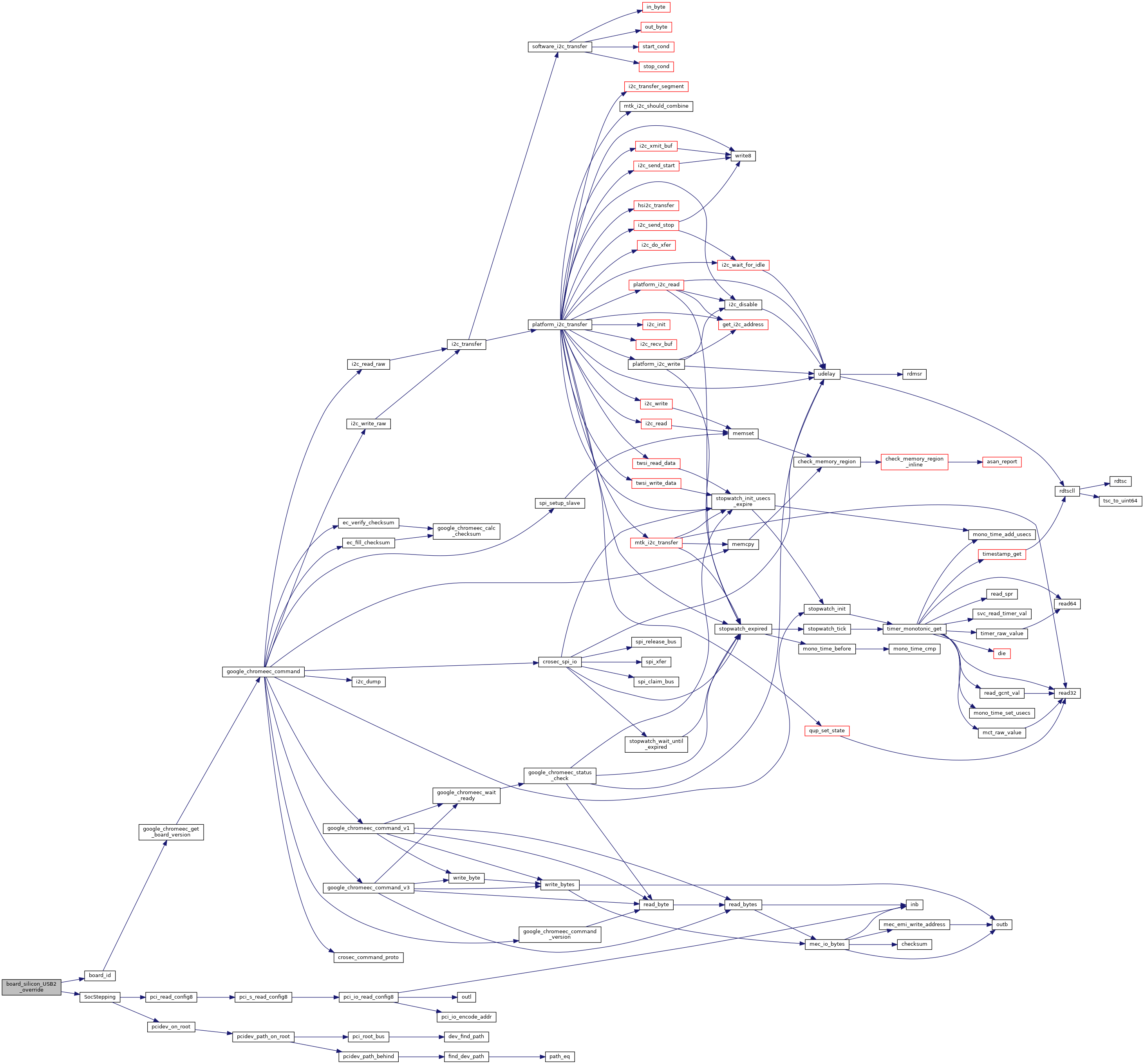

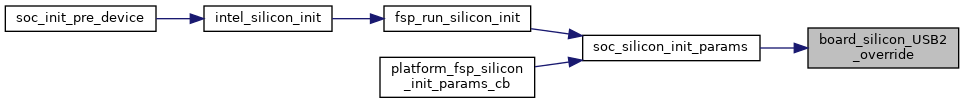

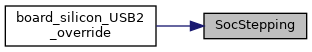

| void board_silicon_USB2_override | ( | SILICON_INIT_UPD * | params | ) |

Definition at line 5 of file ramstage.c.

References board_id(), params, SocD0, SocStepping(), and TERRA2_PROJECT_ID.

Referenced by soc_silicon_init_params().

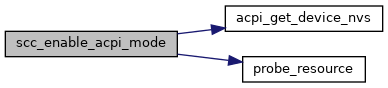

Definition at line 71 of file scc.c.

References acpi_get_device_nvs(), resource::base, PCI_BASE_ADDRESS_0, PCI_BASE_ADDRESS_2, probe_resource(), device_nvs::scc_bar0, device_nvs::scc_bar1, and device_nvs::scc_en.

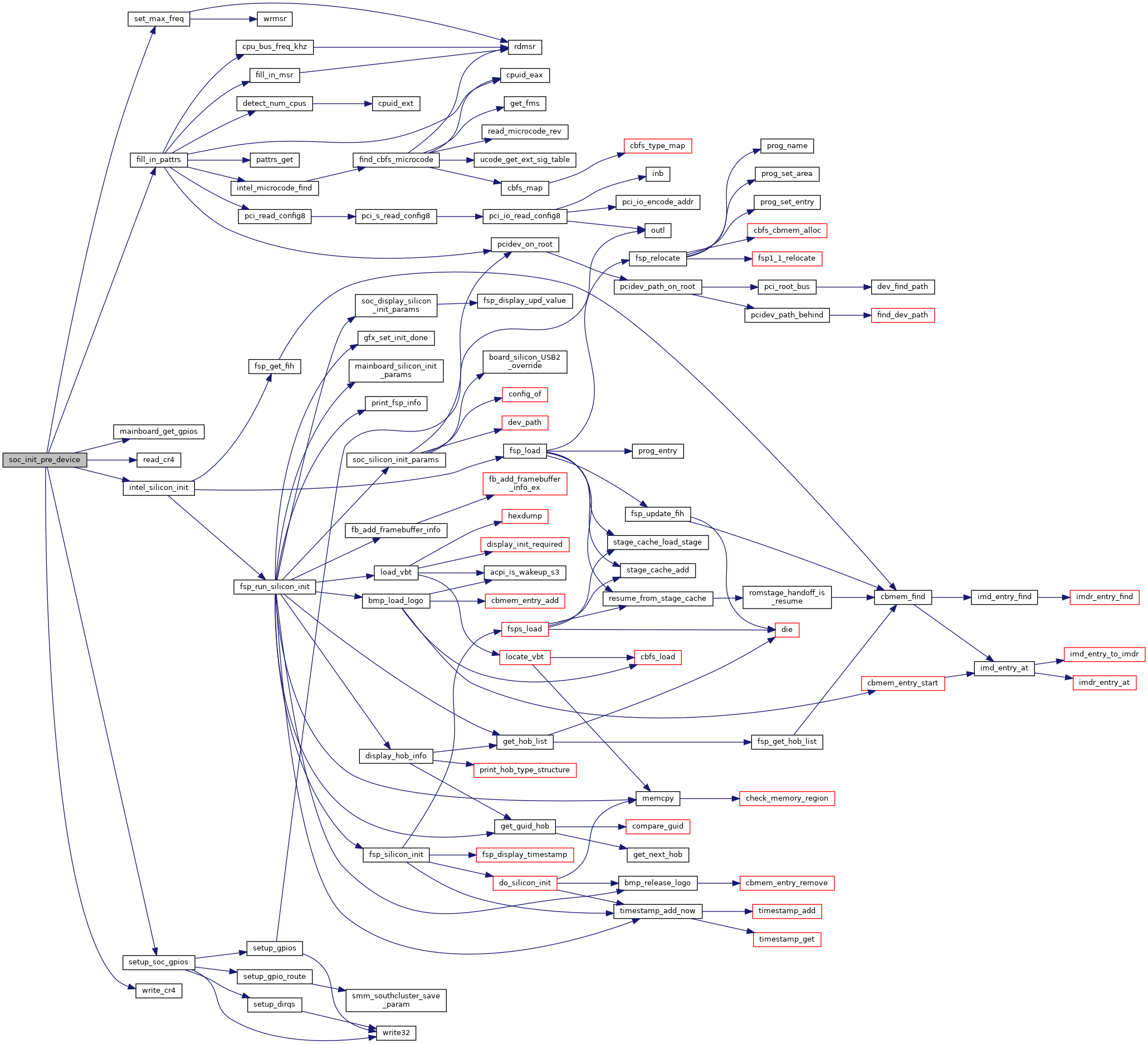

| void soc_init_pre_device | ( | struct soc_intel_braswell_config * | config | ) |

Definition at line 133 of file ramstage.c.

References config, CR4_OSFXSR, CR4_OSXMMEXCPT, fill_in_pattrs(), gpio_config, intel_silicon_init(), mainboard_get_gpios(), read_cr4(), set_max_freq(), setup_soc_gpios(), and write_cr4().

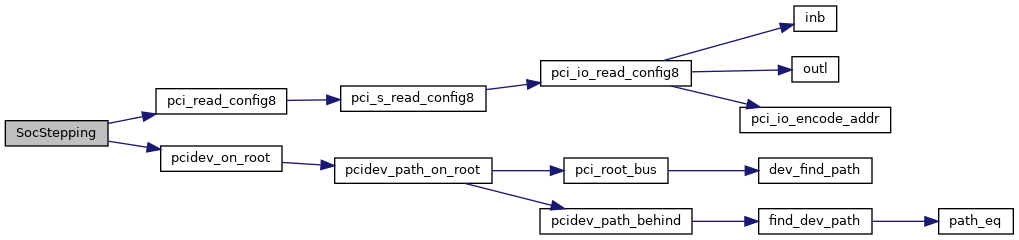

| int SocStepping | ( | void | ) |

Return SoC stepping type.

| SOC_STEPPING | SoC stepping type |

Definition at line 311 of file chip.c.

References B_PCH_LPC_RID_STEPPING_MASK, LPC_DEV, LPC_FUNC, pci_read_config8(), pcidev_on_root(), revid, SocA0, SocA1, SocA2, SocA3, SocA4, SocA5, SocA6, SocA7, SocB0, SocB1, SocB2, SocB3, SocB4, SocB5, SocB6, SocB7, SocC0, SocC1, SocC2, SocC3, SocC4, SocC5, SocC6, SocC7, SocD0, SocD1, SocD2, SocD3, SocD4, SocD5, SocD6, SocD7, SocSteppingMax, V_PCH_LPC_RID_A0, V_PCH_LPC_RID_A1, V_PCH_LPC_RID_A2, V_PCH_LPC_RID_A3, V_PCH_LPC_RID_A4, V_PCH_LPC_RID_A5, V_PCH_LPC_RID_A6, V_PCH_LPC_RID_A7, V_PCH_LPC_RID_B0, V_PCH_LPC_RID_B1, V_PCH_LPC_RID_B2, V_PCH_LPC_RID_B3, V_PCH_LPC_RID_B4, V_PCH_LPC_RID_B5, V_PCH_LPC_RID_B6, V_PCH_LPC_RID_B7, V_PCH_LPC_RID_C0, V_PCH_LPC_RID_C1, V_PCH_LPC_RID_C2, V_PCH_LPC_RID_C3, V_PCH_LPC_RID_C4, V_PCH_LPC_RID_C5, V_PCH_LPC_RID_C6, V_PCH_LPC_RID_C7, V_PCH_LPC_RID_D0, V_PCH_LPC_RID_D1, V_PCH_LPC_RID_D2, V_PCH_LPC_RID_D3, V_PCH_LPC_RID_D4, V_PCH_LPC_RID_D5, V_PCH_LPC_RID_D6, and V_PCH_LPC_RID_D7.

Referenced by board_silicon_USB2_override().

Definition at line 452 of file southcluster.c.