|

coreboot

coreboot is an Open Source project aimed at replacing the proprietary BIOS found in most computers.

|

|

coreboot

coreboot is an Open Source project aimed at replacing the proprietary BIOS found in most computers.

|

Go to the source code of this file.

Functions | |

| void | clock_init (void) |

| int | clock_get_coreclk_khz (void) |

| int | clock_get_tlclk_khz (void) |

| int clock_get_coreclk_khz | ( | void | ) |

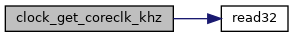

Definition at line 253 of file clock.c.

References BIOS_SPEW, prci_ctlr::coreclksel, prci_ctlr::corepllcfg0, FU540_BASE_FQY, prci, PRCI_CORECLK_MASK, PRCI_PLLCFG_DIVF_MASK, PRCI_PLLCFG_DIVF_SHIFT, PRCI_PLLCFG_DIVQ_MASK, PRCI_PLLCFG_DIVQ_SHIFT, PRCI_PLLCFG_DIVR_MASK, PRCI_PLLCFG_DIVR_SHIFT, printk, and read32().

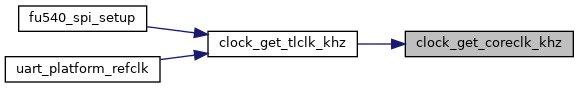

Referenced by clock_get_tlclk_khz().

| int clock_get_tlclk_khz | ( | void | ) |

Definition at line 274 of file clock.c.

References clock_get_coreclk_khz().

Referenced by fu540_spi_setup(), and uart_platform_refclk().

Definition at line 539 of file clock.c.

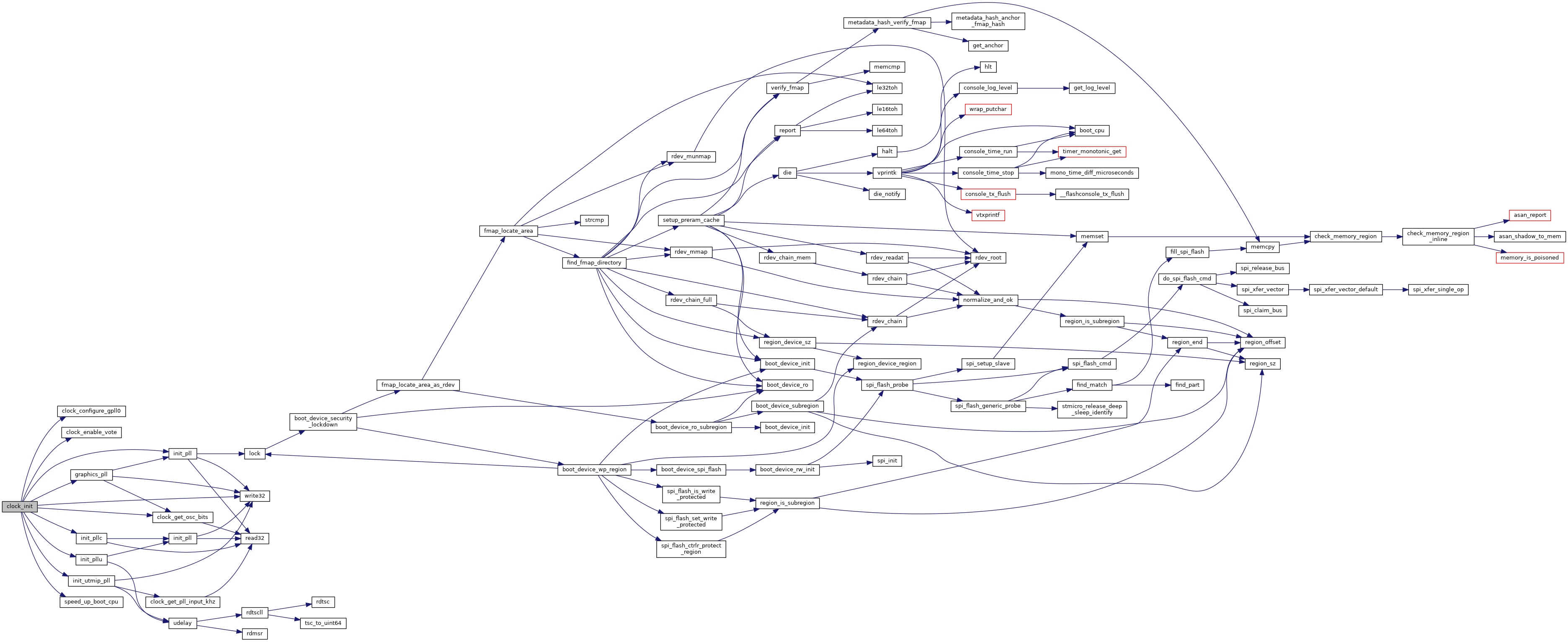

References qcs405_gcc::blsp1_ahb_cbcr, BLSP1_AHB_CLK_ENA, qcs405_gcc::blsp2_ahb_cbcr, BLSP2_AHB_CLK_ENA, CCLK_BURST_POLICY_VAL, CLK_DIVIDER, CLK_M_DIVISOR_BY_2, CLK_M_DIVISOR_MASK, clk_rst, CLK_RST_REG, clk_rst_ctlr::clk_sys_rate, clock_configure_gpll0(), clock_enable_vote(), clock_get_osc_bits(), clrbits32, clrsetbits32, gcc, qcs405_gcc::gcc_apcs_clock_branch_en_vote, graphics_pll(), HCLK_DIVISOR_SHIFT, init_pll(), init_pllc(), init_pllu(), init_utmip_pll(), clk_rst_ctlr::osc_ctrl, OSC_DRIVE_STRENGTH, tegra_pmc_regs::osc_edpd_over, osc_table, OSC_XOFS_MASK, OSC_XOFS_SHIFT, PCLK_DIVISOR_SHIFT, PLL_OUT1_SHIFT, PLL_OUT2_SHIFT, PLL_OUT3_SHIFT, PLL_OUT4_SHIFT, PLL_OUT_CLKEN, PLL_OUT_OVR, PLL_OUT_RATIO_SHIFT, PLL_OUT_RSTN, clk_rst_ctlr::pllc_base, clk_rst_ctlr::pllc_misc, clk_rst_ctlr::pllc_misc2, PLLC_MISC_LOCK_ENABLE, clk_rst_ctlr::pllc_out, clk_rst_ctlr::pllp_outa, clk_rst_ctlr::pllp_outb, PLLPAXS_MISC_LOCK_ENABLE, clk_rst_ctlr::pllu_base, clk_rst_ctlr::pllu_misc, PLLUD_MISC_LOCK_ENABLE, clk_rst_ctlr::pllx_base, PLLX_IDDQ_MASK, PLLX_INDEX, clk_rst_ctlr::pllx_misc, clk_rst_ctlr::pllx_misc3, pmc, PMC_OSC_EDPD_OVER_XOFS_MASK, PMC_OSC_EDPD_OVER_XOFS_SHIFT, QUPV3_WRAP0_CORE_2X_CLK_ENA, QUPV3_WRAP0_CORE_CLK_ENA, QUPV3_WRAP1_CORE_2X_CLK_ENA, QUPV3_WRAP1_CORE_CLK_ENA, QUPV3_WRAP_0_M_AHB_CLK_ENA, QUPV3_WRAP_0_S_AHB_CLK_ENA, QUPV3_WRAP_1_M_AHB_CLK_ENA, QUPV3_WRAP_1_S_AHB_CLK_ENA, clk_rst_ctlr::sclk_brst_pol, SCLK_RUN_SHIFT, SCLK_SOURCE_PLLC_OUT1, SCLK_SYS_STATE_RUN, SCLK_SYS_STATE_SHIFT, speed_up_boot_cpu(), TEGRA_HCLK_RATIO, TEGRA_PCLK_RATIO, TEGRA_PLLC_KHZ, TEGRA_PLLP_KHZ, TEGRA_PLLP_OUT3_KHZ, TEGRA_SCLK_KHZ, TEGRA_TMRUS_BASE, TIMERUS_USEC_CFG, TIMERUS_USEC_CFG_19P2_CLK_M, and write32().

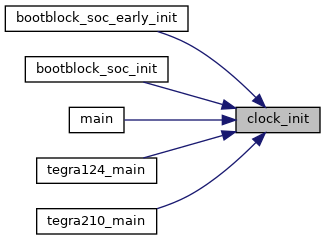

Referenced by bootblock_soc_early_init(), bootblock_soc_init(), main(), tegra124_main(), and tegra210_main().