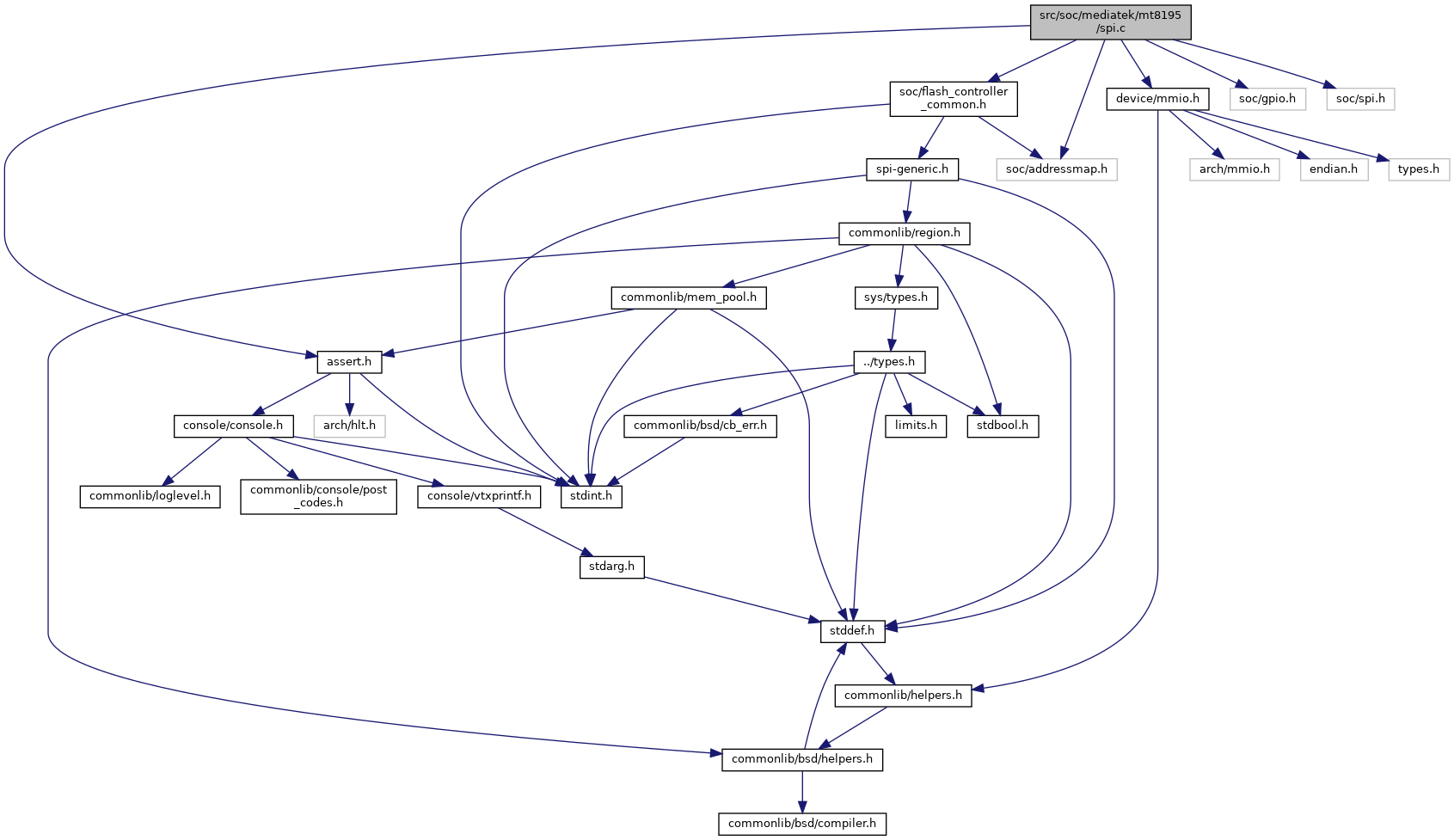

#include <assert.h>

#include <device/mmio.h>

#include <soc/addressmap.h>

#include <soc/flash_controller_common.h>

#include <soc/gpio.h>

#include <soc/spi.h>

Go to the source code of this file.

◆ PAD_FUNC

| #define PAD_FUNC |

( |

|

name, |

|

|

|

func |

|

) |

| {PAD_##name##_ID, PAD_##name##_FUNC_##func} |

Definition at line 42 of file spi.c.

◆ PAD_FUNC_GPIO

| #define PAD_FUNC_GPIO |

( |

|

name | ) |

{PAD_##name##_ID, 0} |

Definition at line 43 of file spi.c.

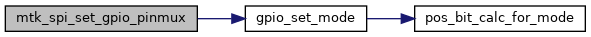

◆ mtk_spi_set_gpio_pinmux()

◆ pad0_funcs

◆ spi_bus

Initial value:= {

{

.cs_gpio =

GPIO(SPIM0_CSB),

},

{

.cs_gpio =

GPIO(SPIM1_CSB),

},

{

.cs_gpio =

GPIO(SPIM2_CSB),

},

{

.cs_gpio =

GPIO(PWRAP_SPI_CSN),

},

{

},

{

},

}

Definition at line 1 of file spi.c.

Referenced by gspi_ctrlr_params_init(), and gspi_spi_to_gspi_bus().

◆ spi_ctrlr_bus_map

Initial value:= {

{

.bus_start = 0,

},

{

.bus_start = CONFIG_BOOT_DEVICE_SPI_FLASH_BUS,

.bus_end = CONFIG_BOOT_DEVICE_SPI_FLASH_BUS,

},

}

Definition at line 84 of file spi.c.

◆ spi_ctrlr_bus_map_count

◆ spi_flash_ctrlr

Initial value:= {

.max_xfer_size = 65535,

}

int mtk_spi_flash_probe(const struct spi_slave *spi, struct spi_flash *flash)

Definition at line 84 of file spi.c.