|

coreboot

coreboot is an Open Source project aimed at replacing the proprietary BIOS found in most computers.

|

|

coreboot

coreboot is an Open Source project aimed at replacing the proprietary BIOS found in most computers.

|

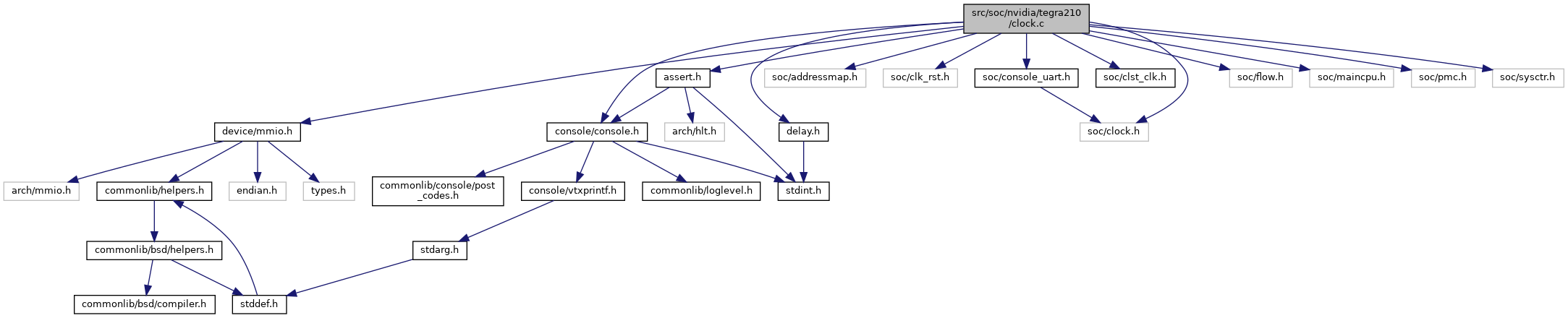

#include <device/mmio.h>#include <assert.h>#include <console/console.h>#include <delay.h>#include <soc/addressmap.h>#include <soc/clk_rst.h>#include <soc/clock.h>#include <soc/clst_clk.h>#include <soc/console_uart.h>#include <soc/flow.h>#include <soc/maincpu.h>#include <soc/pmc.h>#include <soc/sysctr.h>

Go to the source code of this file.

Data Structures | |

| struct | pll_reg_info |

| struct | pll_fields |

Macros | |

| #define | PLL_HAS_KCP_KVCO(_n, _m, _p, _kcp, _kvco) {.n = _n, .m = _m, .p = _p, .kcp = _kcp, .kvco = _kvco,} |

| #define | PLL_NO_KCP_KVCO(_n, _m, _p) {.n = _n, .m = _m, .p = _p,} |

| #define | PLLX(_n, _m, _p, _kcp, _kvco) [PLLX_INDEX] = PLL_HAS_KCP_KVCO(_n, _m, _p, _kcp, _kvco) |

| #define | PLLC(_n, _m, _p) [PLLC_INDEX] = PLL_NO_KCP_KVCO(_n, _m, _p) |

| #define | PLLU(_n, _m, _p, _kcp, _kvco) [PLLU_INDEX] = PLL_HAS_KCP_KVCO(_n, _m, _p, _kcp, _kvco) |

| #define | PLLDP(_n, _m, _p, _kcp, _kvco) [PLLDP_INDEX] = PLL_HAS_KCP_KVCO(_n, _m, _p, _kcp, _kvco) |

| #define | PLLD(_n, _m, _p, _kcp, _kvco) [PLLD_INDEX] = PLL_HAS_KCP_KVCO(_n, _m, _p, _kcp, _kvco) |

| #define | SOR0_CLK_SEL0 (1 << 14) |

| #define | SOR0_CLK_SEL1 (1 << 15) |

Enumerations | |

| enum | { PLLX_INDEX , PLLC_INDEX , PLLU_INDEX , PLLDP_INDEX , PLLD_INDEX , PLL_MAX_INDEX } |

Variables | |

| static struct flow_ctlr * | flow = (void *)TEGRA_FLOW_BASE |

| static struct tegra_pmc_regs * | pmc = (void *)TEGRA_PMC_BASE |

| static struct sysctr_regs * | sysctr = (void *)TEGRA_SYSCTR0_BASE |

| struct pll_reg_info | pll_reg_table [] |

| struct { | |

| int khz | |

| struct pll_fields plls [PLL_MAX_INDEX] | |

| } | osc_table [16] |

| static u32 *const | clk_enb_set_arr [DEV_CONFIG_BLOCKS] |

| static u32 *const | clk_enb_clr_arr [DEV_CONFIG_BLOCKS] |

| static u32 *const | rst_dev_set_arr [DEV_CONFIG_BLOCKS] |

| static u32 *const | rst_dev_clr_arr [DEV_CONFIG_BLOCKS] |

| #define PLL_HAS_KCP_KVCO | ( | _n, | |

| _m, | |||

| _p, | |||

| _kcp, | |||

| _kvco | |||

| ) | {.n = _n, .m = _m, .p = _p, .kcp = _kcp, .kvco = _kvco,} |

| #define PLL_NO_KCP_KVCO | ( | _n, | |

| _m, | |||

| _p | |||

| ) | {.n = _n, .m = _m, .p = _p,} |

| #define PLLC | ( | _n, | |

| _m, | |||

| _p | |||

| ) | [PLLC_INDEX] = PLL_NO_KCP_KVCO(_n, _m, _p) |

| #define PLLD | ( | _n, | |

| _m, | |||

| _p, | |||

| _kcp, | |||

| _kvco | |||

| ) | [PLLD_INDEX] = PLL_HAS_KCP_KVCO(_n, _m, _p, _kcp, _kvco) |

| #define PLLDP | ( | _n, | |

| _m, | |||

| _p, | |||

| _kcp, | |||

| _kvco | |||

| ) | [PLLDP_INDEX] = PLL_HAS_KCP_KVCO(_n, _m, _p, _kcp, _kvco) |

| #define PLLU | ( | _n, | |

| _m, | |||

| _p, | |||

| _kcp, | |||

| _kvco | |||

| ) | [PLLU_INDEX] = PLL_HAS_KCP_KVCO(_n, _m, _p, _kcp, _kvco) |

| #define PLLX | ( | _n, | |

| _m, | |||

| _p, | |||

| _kcp, | |||

| _kvco | |||

| ) | [PLLX_INDEX] = PLL_HAS_KCP_KVCO(_n, _m, _p, _kcp, _kvco) |

| anonymous enum |

Definition at line 707 of file clock.c.

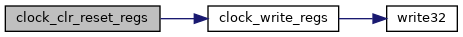

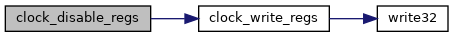

References clock_write_regs(), and rst_dev_clr_arr.

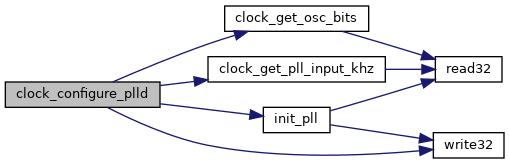

plld (fo) = vco >> p, where 500MHz < vco < 1000MHz = (cf * n) >> p, where 1MHz < cf < 6MHz = ((ref / m) * n) >> p

Iterate the possible values of p (3 bits, 2^7) to find out a minimum safe vco, then find best (m, n). since m has only 5 bits, we can iterate all possible values. Note Tegra1xx supports 11 bits for n, but our pll_fields has only 10 bits for n.

Note values undershoot or overshoot target output frequency may not work if the values are not in "safe" range by panel specification.

Definition at line 385 of file clock.c.

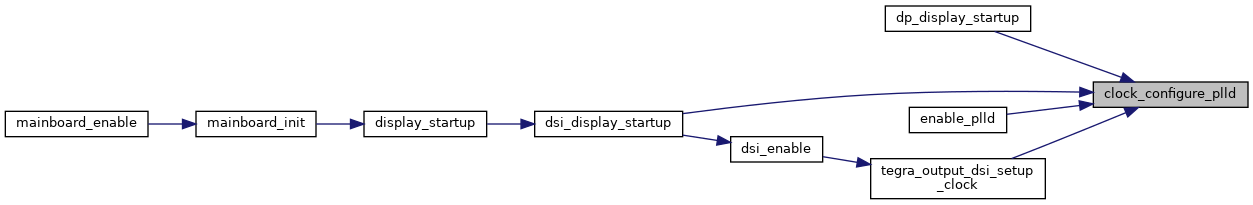

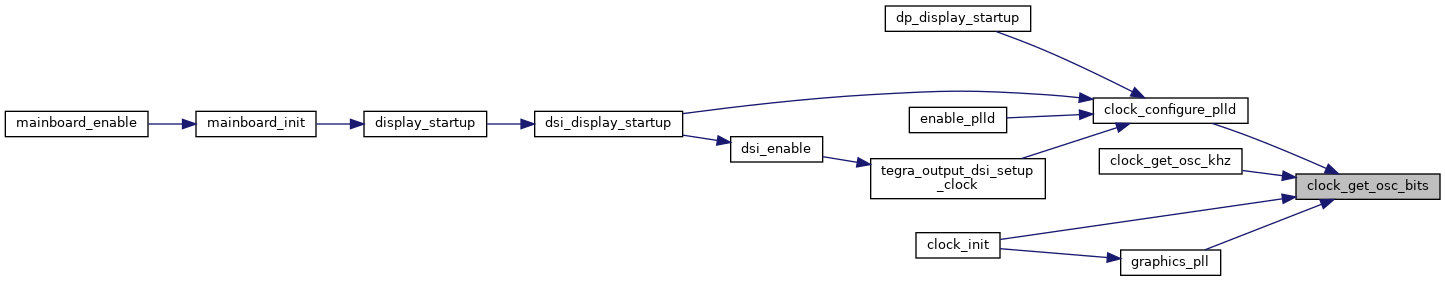

References BIOS_DEBUG, BIOS_ERR, BIOS_WARNING, CLK_RST_REG, clock_get_osc_bits(), clock_get_pll_input_khz(), init_pll(), m, pll_fields::m, mhz, pll_fields::n, osc_table, pll_fields::p, PLLD_INDEX, PLLD_MISC1_SETUP, PLLD_MISC_EN_SDM, PLLD_MISC_SDM_DIN, printk, and write32().

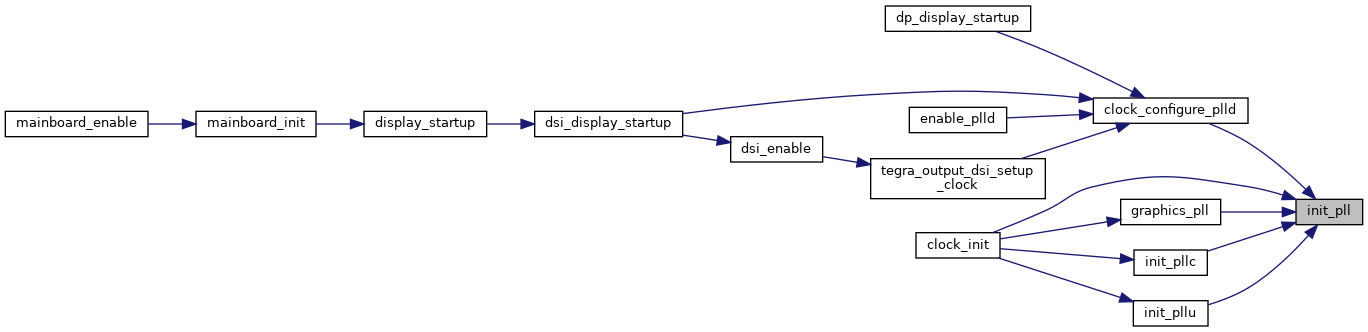

Referenced by dp_display_startup(), dsi_display_startup(), enable_plld(), and tegra_output_dsi_setup_clock().

Definition at line 697 of file clock.c.

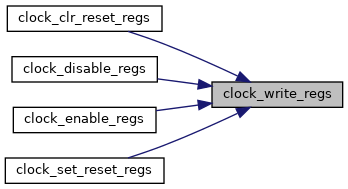

References clk_enb_clr_arr, and clock_write_regs().

Definition at line 478 of file clock.c.

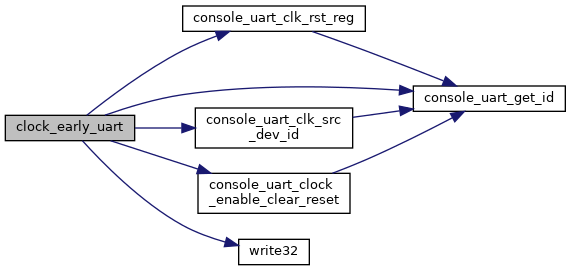

References CLK_DIVIDER, CLK_SOURCE_SHIFT, CLK_UART_DIV_OVERRIDE, console_uart_clk_rst_reg(), console_uart_clk_src_dev_id(), console_uart_clock_enable_clear_reset(), console_uart_get_id(), TEGRA_PLLP_KHZ, UART_ID_NONE, and write32().

Definition at line 772 of file clock.c.

References CLK_L_I2S1, CLK_L_I2S2, CLK_L_I2S3, CLK_L_SPDIF, CLK_V_AHUB, CLK_V_APB2APE, CLK_V_EXTPERIPH1, CLK_V_I2S4, CLK_V_I2S5, and clock_enable_clear_reset().

Referenced by setup_audio().

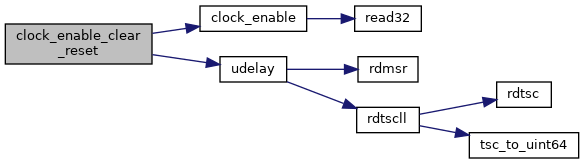

Definition at line 712 of file clock.c.

References clock_clr_reset, clock_enable(), IO_STABILIZATION_DELAY, pll_fields::u, udelay(), x, and y.

Definition at line 692 of file clock.c.

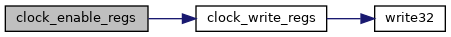

References clk_enb_set_arr, and clock_write_regs().

| void clock_external_output | ( | int | clk_id | ) |

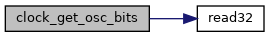

Definition at line 203 of file clock.c.

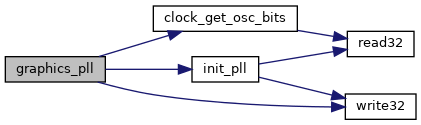

References CLK_RST_REG, OSC_FREQ_MASK, OSC_FREQ_SHIFT, and read32().

Referenced by clock_configure_plld(), clock_get_osc_khz(), clock_init(), and graphics_pll().

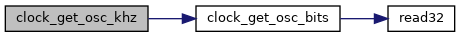

| int clock_get_osc_khz | ( | void | ) |

Definition at line 208 of file clock.c.

References clock_get_osc_bits(), and osc_table.

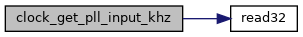

| int clock_get_pll_input_khz | ( | void | ) |

Definition at line 213 of file clock.c.

References CLK_RST_REG, OSC_FREQ_MASK, OSC_FREQ_SHIFT, OSC_PREDIV_MASK, OSC_PREDIV_SHIFT, osc_table, and read32().

Definition at line 634 of file clock.c.

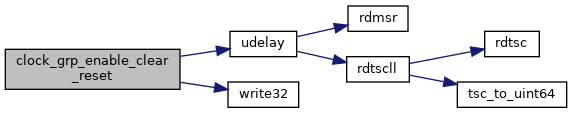

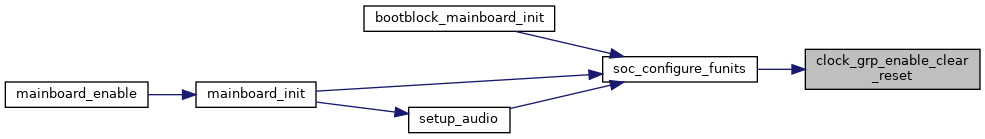

References IO_STABILIZATION_DELAY, udelay(), val, and write32().

Referenced by soc_configure_funits().

Definition at line 562 of file clock.c.

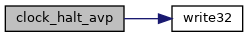

References flow, FLOW_EVENT_GIC_IRQ, FLOW_EVENT_JTAG, FLOW_EVENT_LIC_IRQ, FLOW_MODE_WAITEVENT, flow_ctlr::halt_cop_events, and write32().

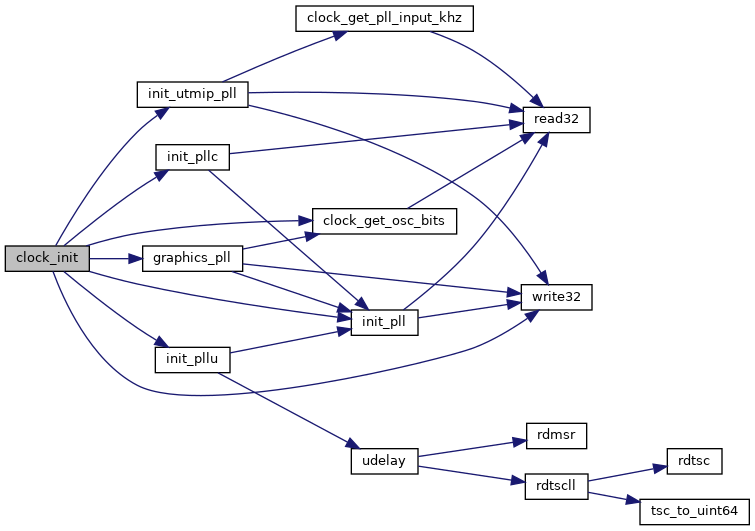

Definition at line 571 of file clock.c.

References CCLK_BURST_POLICY_VAL, CLK_DIVIDER, CLK_M_DIVISOR_BY_2, CLK_M_DIVISOR_MASK, CLK_RST_REG, clock_get_osc_bits(), clrbits32, clrsetbits32, graphics_pll(), HCLK_DIVISOR_SHIFT, init_pll(), init_pllc(), init_pllu(), init_utmip_pll(), OSC_DRIVE_STRENGTH, tegra_pmc_regs::osc_edpd_over, OSC_XOFS_MASK, OSC_XOFS_SHIFT, PCLK_DIVISOR_SHIFT, PLL_OUT1_SHIFT, PLL_OUT2_SHIFT, PLL_OUT3_SHIFT, PLL_OUT4_SHIFT, PLL_OUT_CLKEN, PLL_OUT_OVR, PLL_OUT_RATIO_SHIFT, PLL_OUT_RSTN, PLLX_IDDQ_MASK, PLLX_INDEX, pmc, PMC_OSC_EDPD_OVER_XOFS_MASK, PMC_OSC_EDPD_OVER_XOFS_SHIFT, SCLK_RUN_SHIFT, SCLK_SOURCE_PLLC_OUT1, SCLK_SYS_STATE_RUN, SCLK_SYS_STATE_SHIFT, TEGRA_PLLC_KHZ, TEGRA_PLLP_KHZ, TEGRA_PLLP_OUT3_KHZ, TEGRA_TMRUS_BASE, TIMERUS_USEC_CFG, TIMERUS_USEC_CFG_19P2_CLK_M, and write32().

Definition at line 221 of file clock.c.

References sysctr_regs::cntcr, sysctr_regs::cntfid0, read32(), sysctr, SYSCTR_CNTCR_EN, SYSCTR_CNTCR_HDBG, TEGRA_CLK_M_KHZ, and write32().

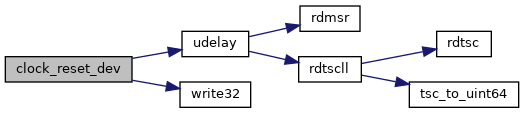

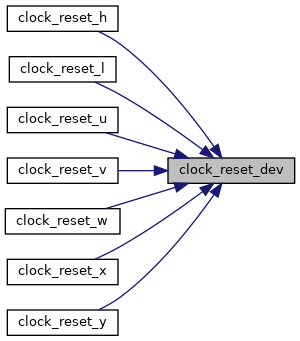

Definition at line 722 of file clock.c.

References LOGIC_STABILIZATION_DELAY, udelay(), and write32().

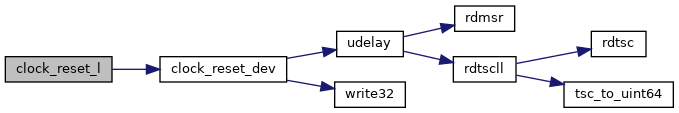

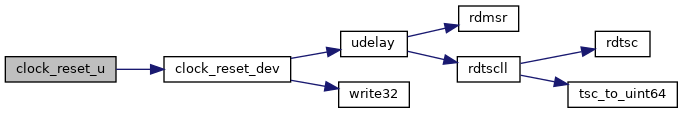

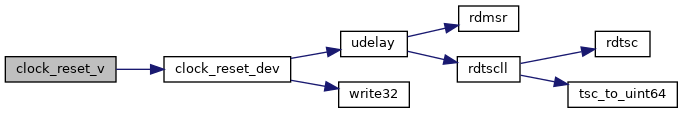

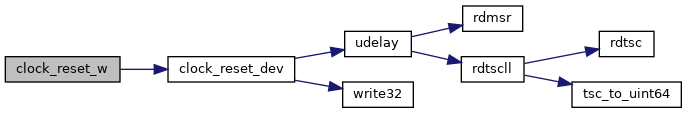

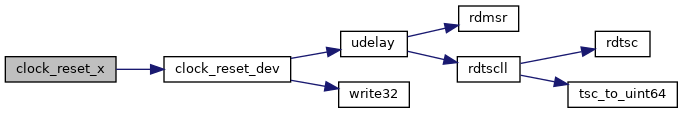

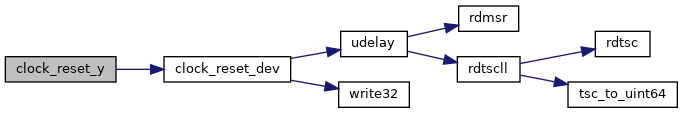

Referenced by clock_reset_h(), clock_reset_l(), clock_reset_u(), clock_reset_v(), clock_reset_w(), clock_reset_x(), and clock_reset_y().

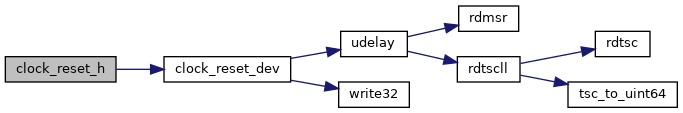

Definition at line 735 of file clock.c.

References CLK_RST_REG, and clock_reset_dev().

Definition at line 729 of file clock.c.

References CLK_RST_REG, and clock_reset_dev().

Definition at line 741 of file clock.c.

References CLK_RST_REG, and clock_reset_dev().

Definition at line 747 of file clock.c.

References CLK_RST_REG, and clock_reset_dev().

Definition at line 753 of file clock.c.

References CLK_RST_REG, and clock_reset_dev().

Definition at line 759 of file clock.c.

References CLK_RST_REG, and clock_reset_dev().

Definition at line 765 of file clock.c.

References CLK_RST_REG, and clock_reset_dev().

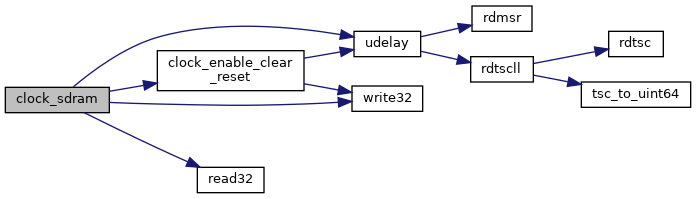

| void clock_sdram | ( | u32 | m, |

| u32 | n, | ||

| u32 | p, | ||

| u32 | setup, | ||

| u32 | kvco, | ||

| u32 | kcp, | ||

| u32 | stable_time, | ||

| u32 | emc_source, | ||

| u32 | same_freq | ||

| ) |

Definition at line 512 of file clock.c.

References base, CLK_H_EMC, CLK_H_MEM, CLK_RST_REG, CLK_SOURCE_EMC_MC_EMC_SAME_FREQ, clock_enable_clear_reset(), IO_STABILIZATION_DELAY, pll_fields::kcp, pll_fields::kvco, m, pll_fields::n, pll_fields::p, PLL_BASE_BYPASS, PLL_BASE_DIVM_SHIFT, PLL_BASE_DIVN_SHIFT, PLL_BASE_DIVP_SHIFT, PLL_BASE_ENABLE, PLL_BASE_LOCK, PLLCMX_BASE_DIVM_MASK, PLLCMX_BASE_DIVN_MASK, PLLM_BASE_DIVP_MASK, PLLM_EN_LCKDET, PLLM_MISC1_SETUP_SHIFT, PLLM_MISC2_KCP_SHIFT, PLLM_MISC2_KVCO_SHIFT, read32(), setbits32, udelay(), and write32().

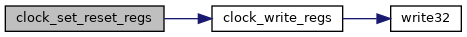

Definition at line 702 of file clock.c.

References clock_write_regs(), and rst_dev_set_arr.

|

static |

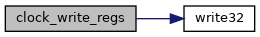

Definition at line 682 of file clock.c.

References DEV_CONFIG_BLOCKS, and write32().

Referenced by clock_clr_reset_regs(), clock_disable_regs(), clock_enable_regs(), and clock_set_reset_regs().

Definition at line 356 of file clock.c.

References CLK_RST_REG, clock_get_osc_bits(), init_pll(), PLLDP_INDEX, and write32().

Referenced by clock_init().

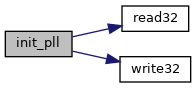

Definition at line 252 of file clock.c.

References assert, pll_reg_info::base_reg, pll_reg_info::kcp_kvco_reg, pll_reg_info::kcp_shift, pll_reg_info::kvco_shift, pll_reg_info::lock_enb_reg, pll_reg_info::lock_enb_val, pll_reg_info::m_shift, pll_reg_info::n_shift, osc_table, pll_reg_info::p_shift, PLL_BASE_BYPASS, PLL_BASE_ENABLE, pll_reg_info::pll_lock_reg, pll_reg_info::pll_lock_val, PLL_MAX_INDEX, pll_reg_table, read32(), setbits32, and write32().

Referenced by clock_configure_plld(), clock_init(), graphics_pll(), init_pllc(), and init_pllu().

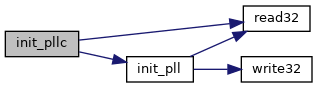

Definition at line 285 of file clock.c.

References CLK_RST_REG, clrbits32, init_pll(), PLLC_BASE_LOCK, PLLC_INDEX, PLLC_MISC_1_IDDQ, PLLC_MISC_RESET, and read32().

Referenced by clock_init().

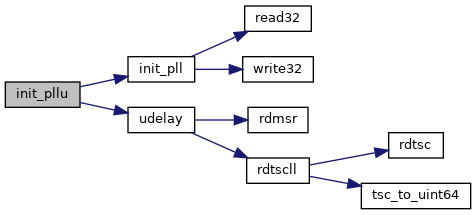

Definition at line 301 of file clock.c.

References CLK_RST_REG, clrbits32, init_pll(), PLLU_INDEX, PLLU_MISC_IDDQ, and udelay().

Referenced by clock_init().

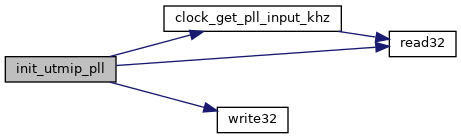

Definition at line 312 of file clock.c.

References BIOS_DEBUG, CLK_RST_REG, clock_get_pll_input_khz(), DIV_ROUND_UP, khz, printk, read32(), UTMIP_CFG1_FORCE_PLL_ACTIVE_POWERDOWN_DISABLE, UTMIP_CFG1_FORCE_PLL_ENABLE_POWERDOWN_DISABLE, UTMIP_CFG1_FORCE_PLL_ENABLE_POWERUP_ENABLE, UTMIP_CFG1_FORCE_PLLU_POWERDOWN_ENABLE, UTMIP_CFG1_PLLU_ENABLE_DLY_COUNT_SHIFT, UTMIP_CFG1_XTAL_FREQ_COUNT_SHIFT, UTMIP_CFG2_FORCE_PD_SAMP_A_POWERDOWN_DISABLE, UTMIP_CFG2_FORCE_PD_SAMP_A_POWERUP_ENABLE, UTMIP_CFG2_FORCE_PD_SAMP_B_POWERDOWN_DISABLE, UTMIP_CFG2_FORCE_PD_SAMP_B_POWERUP_ENABLE, UTMIP_CFG2_FORCE_PD_SAMP_C_POWERDOWN_DISABLE, UTMIP_CFG2_FORCE_PD_SAMP_C_POWERUP_ENABLE, UTMIP_CFG2_FORCE_PD_SAMP_D_POWERDOWN_DISABLE, UTMIP_CFG2_FORCE_PD_SAMP_D_POWERUP_ENABLE, UTMIP_CFG2_PLL_ACTIVE_DLY_COUNT_SHIFT, UTMIP_CFG2_PLLU_STABLE_COUNT_SHIFT, and write32().

Referenced by clock_init().

Definition at line 246 of file clock.c.

References CLK_RST_REG, setbits32, and SOR0_CLK_SEL0.

Definition at line 236 of file clock.c.

References CLK_RST_REG, clrbits32, SOR0_CLK_SEL0, and SOR0_CLK_SEL1.

|

static |

Definition at line 652 of file clock.c.

Referenced by clock_disable_regs().

|

static |

Definition at line 642 of file clock.c.

Referenced by clock_enable_regs().

|

static |

Definition at line 17 of file clock.c.

Referenced by clock_halt_avp().

| struct { ... } osc_table[16] |

| struct pll_reg_info pll_reg_table[] |

Referenced by init_pll().

| struct pll_fields plls[PLL_MAX_INDEX] |

|

static |

Definition at line 18 of file clock.c.

Referenced by clock_external_output(), and clock_init().

|

static |

Definition at line 672 of file clock.c.

Referenced by clock_clr_reset_regs().

|

static |

Definition at line 662 of file clock.c.

Referenced by clock_set_reset_regs().

|

static |

Definition at line 19 of file clock.c.

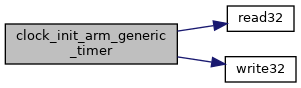

Referenced by clock_init_arm_generic_timer().