|

coreboot

coreboot is an Open Source project aimed at replacing the proprietary BIOS found in most computers.

|

|

coreboot

coreboot is an Open Source project aimed at replacing the proprietary BIOS found in most computers.

|

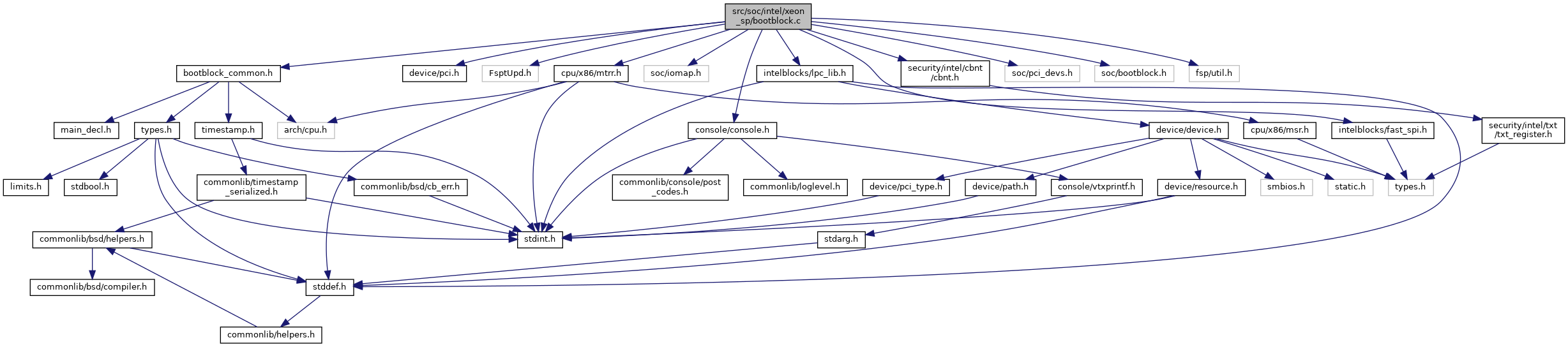

#include <bootblock_common.h>#include <device/pci.h>#include <FsptUpd.h>#include <intelblocks/fast_spi.h>#include <soc/iomap.h>#include <console/console.h>#include <cpu/x86/mtrr.h>#include <intelblocks/lpc_lib.h>#include <security/intel/cbnt/cbnt.h>#include <soc/pci_devs.h>#include <soc/bootblock.h>#include <fsp/util.h>

Go to the source code of this file.

Functions | |

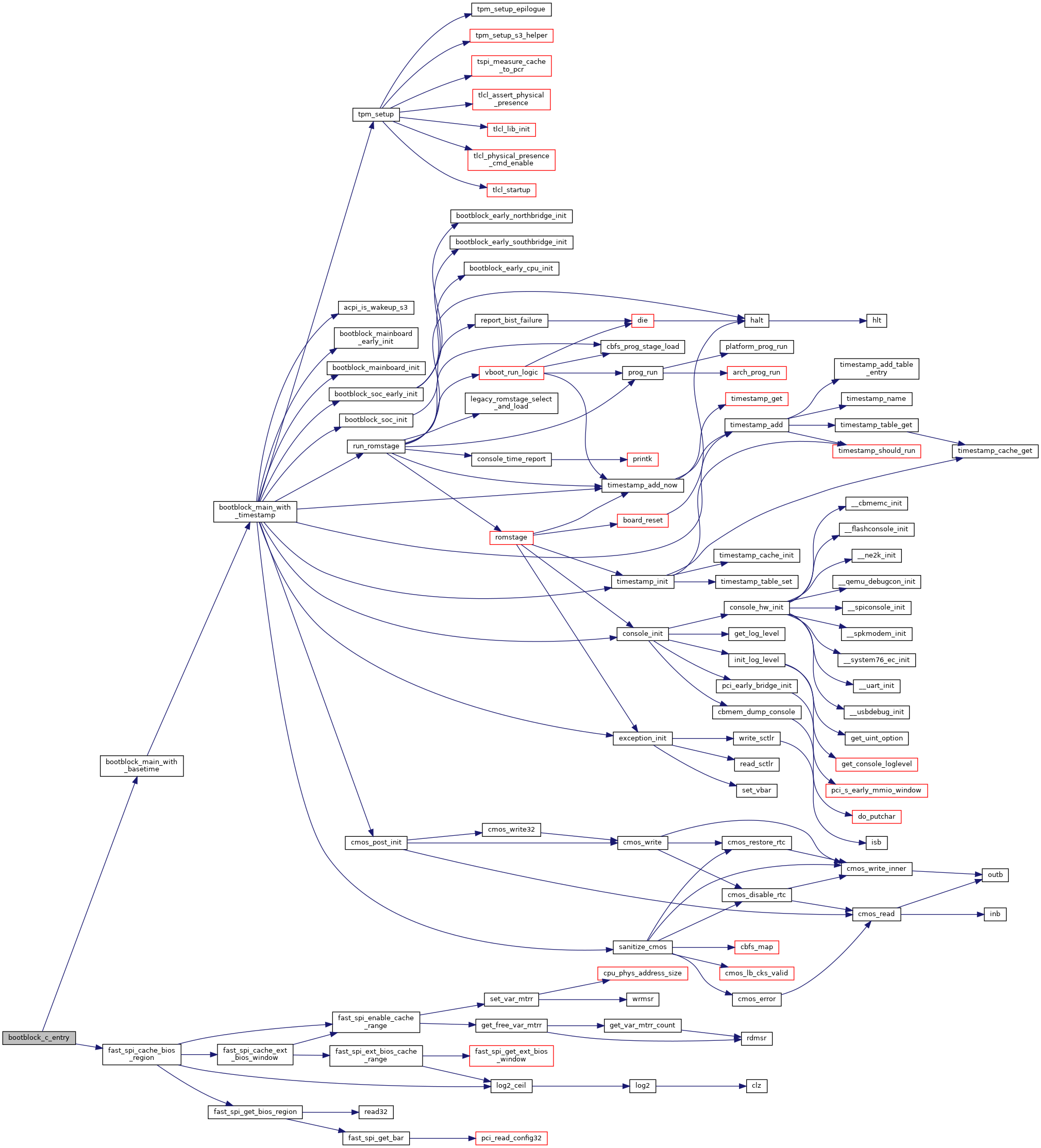

| asmlinkage void | bootblock_c_entry (uint64_t base_timestamp) |

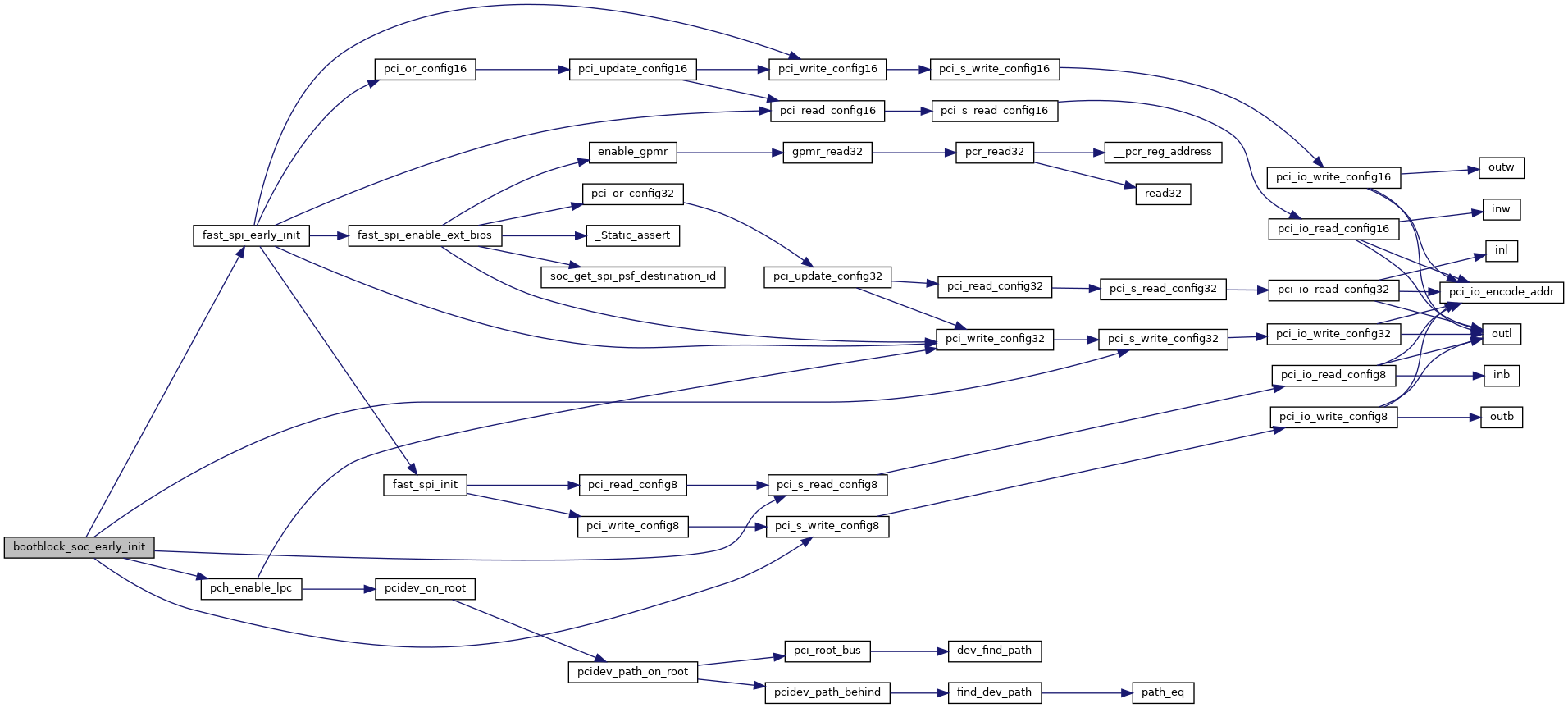

| void | bootblock_soc_early_init (void) |

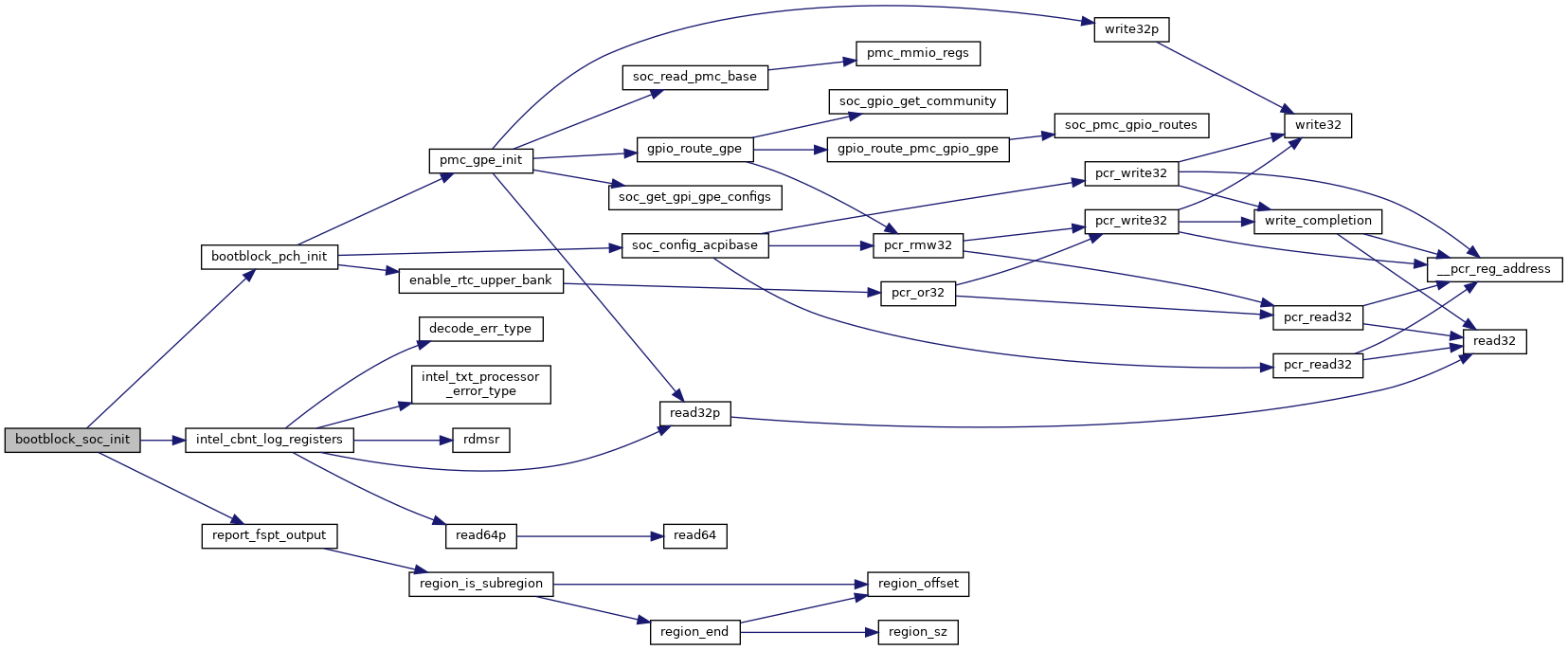

| void | bootblock_soc_init (void) |

Variables | |

| const FSPT_UPD | temp_ram_init_params |

| static uint64_t | assembly_timestamp |

| static uint64_t | bootblock_timestamp |

| asmlinkage void bootblock_c_entry | ( | uint64_t | base_timestamp | ) |

Definition at line 40 of file bootblock.c.

References assembly_timestamp, bootblock_main_with_basetime(), bootblock_timestamp, fast_spi_cache_bios_region(), MIN, and timestamp_get.

Definition at line 53 of file bootblock.c.

References fast_spi_early_init(), PCH_DEV_P2SB, pch_enable_lpc(), PCI_BASE_ADDRESS_0, PCI_COMMAND, PCI_COMMAND_MEMORY, pci_s_read_config8(), pci_s_write_config32(), pci_s_write_config8(), and SPI_BASE_ADDRESS.

Definition at line 64 of file bootblock.c.

References assembly_timestamp, BIOS_WARNING, bootblock_pch_init(), bootblock_timestamp, CONFIG, intel_cbnt_log_registers(), printk, and report_fspt_output().

|

static |

Definition at line 37 of file bootblock.c.

Referenced by bootblock_c_entry(), and bootblock_soc_init().

|

static |

Definition at line 38 of file bootblock.c.

Referenced by bootblock_c_entry(), and bootblock_soc_init().

| const FSPT_UPD temp_ram_init_params |

Definition at line 16 of file bootblock.c.